摘要

在最新的功率半導體技術中,開關速度是最顯眼的屬性,但是在實際電路中,高邊緣速率會造成獨有的問題。本博客將介紹問題和簡單的解決方法。

博客

自從IBM于1958年設計了第一個管以“開關模式供電”后,功率轉換器設計師們就一直夢想擁有沒有導電損耗和開關損耗的理想開關。當然,所有開關技術都降低了開態損耗,而且借助最新的寬帶隙半導體,750V額定值的器件現在可以將電阻降低到6毫歐以下。這些技術尚未達到物理極限,因此預計該值還可進一步降低。

在當今的高性能功率設計中,邊緣速率(V/ns)有所升高,從而降低了開關損耗,因而可以實現更高的頻率、更小的磁性元件和更高的功率密度。然而,這些快速邊緣速率提高了造成電磁干擾設計相關問題的可能性,這些問題會與電路寄生效應交互,還會造成不想要的振蕩和電壓尖峰。借助良好的設計實踐,這些問題可以使用小緩沖電路解決。

實際電路中的高電流邊緣速率會導致電壓尖峰和振鈴

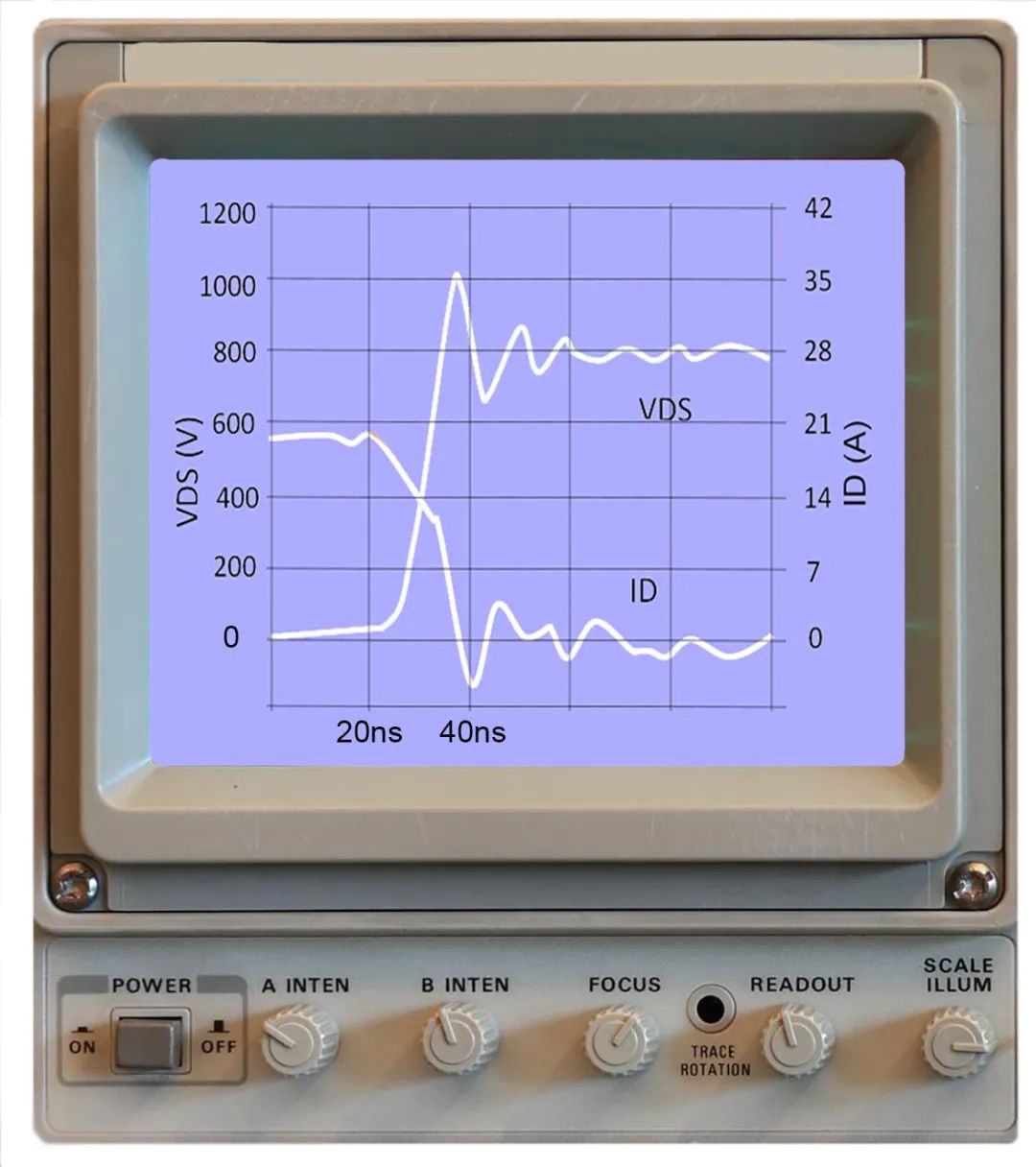

那么,這個問題有多嚴重呢?如果我們看到速率達到3000A/μs,也就是典型的碳化硅開關值,那么根據熟悉的E=-Ldi/dt公式,僅100nH連接電感或漏電電感就會產生300V尖峰電壓。100nH僅僅是幾英寸PCB印制線的電感或者變壓器漏電電感的真實值,因此,這種情況就是通常是會看到的真實情況,而且可能需要一個好示波器才能看到整個電壓瞬態。不過該開關在看到瞬態方面沒有問題,而且如果它超過額定雪崩電壓能量,則會立即停止運轉。在任何電路電容下,該尖峰都會振鈴,從而讓測量的電磁干擾釋放達到峰值。

一個補救措施是嘗試降低電路電感,但是這通常不是實際操作中的選擇。除此以外,還可以大幅降低該開關的電壓,代價是影響成本和導通電阻,也可以使用串聯柵極電阻放緩邊緣速率。這個儀器并不敏感,它延遲了波形,從而通過限制占空比限制了高頻運行,還提高了開關損耗,同時不影響振鈴。

緩沖電路可以允許快速開關,而且會減小尖峰和抑制振鈴。在過去的大電容器和大功率電阻時代,例如與IGBT一起使用時,這看上去像是一個“暴力破解”方法,用于嘗試降低大“尾”電流效應。然而,對于SiC FET等開關而言,這是一個非常高效的解決方案。在這種情況下,主要使用緩沖電路抑制振鈴,同時限制峰值電壓,而且因為器件電容非常低,振鈴頻率高,所以只需要使用一個非常小的緩沖電路電容器,通常為200pF左右,并使用幾歐姆的串聯電阻。和預期一樣,電阻會耗散部分功率,但是它實際上會通過限制硬開關和軟開關應用中的電壓/電流重疊來降低關閉損耗。

在高負荷下使用緩沖電路可提升整體效率

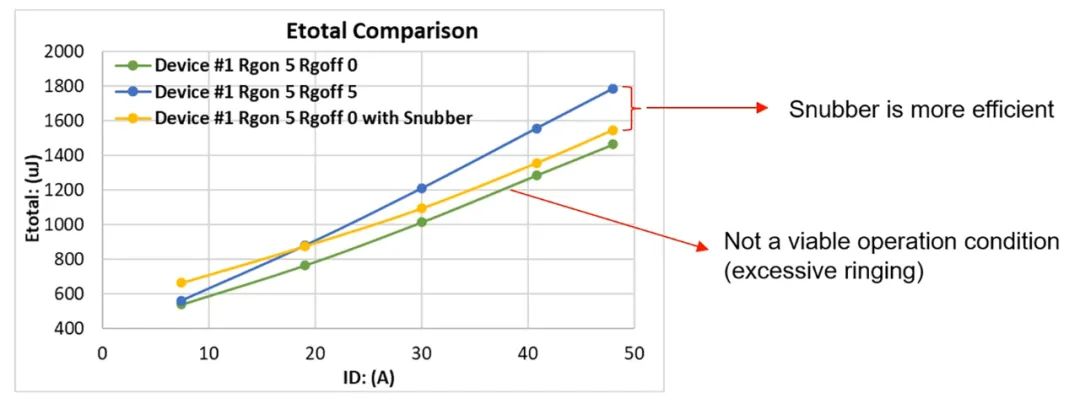

在打開時,緩沖電路會耗散額外的能量,因此需要考慮總損耗E(ON)+ E(OFF)才能公正地評估它的好處。圖1將一些測量值代入E(TOTAL),以體現40毫歐SiC FET在40kHz下的運行狀況,考慮了三種情況:無緩沖電路,RG(ON)和RG(OFF)為5歐姆(藍線);200pF/10歐姆緩沖電路,RG(ON) = 5歐姆,RG(OFF) = 0歐姆(黃線);無緩沖電路,RG(ON) = 5歐姆,RG(OFF) = 0歐姆(綠線)。從中可以看出E(TOTAL)非常低,但是振鈴過高,因而不可行。 在電流大的情況下,使用緩沖電路的好處很明顯,與僅調整柵極電阻相比,在40A下的耗散降低約10.9W。在輕負載下,緩沖電路的整體損耗較高,但是在這些條件下,系統耗散很低。

【圖1:使用小緩沖電路時的能量節約】

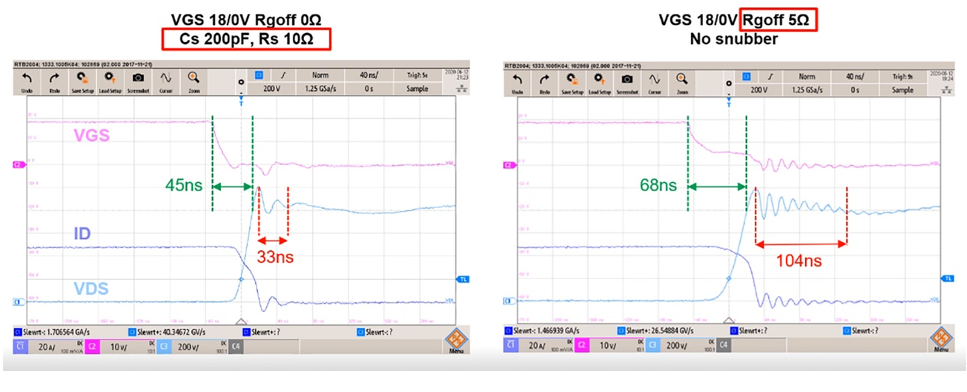

圖2顯示的是使用緩沖電路降低振鈴的效應。

【圖2:使用小緩沖電路顯著降低了振鈴,同時降低了整體耗散,關閉延遲時間也縮短了】

緩沖電路易于實施

綜上所述,緩沖電路是一個好解決方案,但是切實可行嗎?在實踐中,獨立的緩沖電路電阻耗散的熱量不到1瓦,而且可以是小型的表面安裝器件。電容器需要高額定電壓,但是電容值低,因此體積也小。 SIC FET的導電損耗和動態損耗都低,接近理想開關,而且只需增加一個小緩沖電路,它就可以發揮全部潛力,且不會造成過高的電磁干擾或電壓應力問題。更“完美”的是,SiC FET的柵極驅動簡單,整體二極管損耗低,且到外部散熱片的熱阻低。還有什么理由不喜歡它呢?

審核編輯:劉清

-

功率轉換器

+關注

關注

0文章

89瀏覽量

19389 -

緩沖電路

+關注

關注

1文章

74瀏覽量

20196 -

半導體開關

+關注

關注

0文章

6瀏覽量

6919

原文標題:理想半導體開關的挑戰

文章出處:【微信號:UnitedSiC,微信公眾號:UnitedSiC】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

開關電源常見故障及解決方法

pcb設計中遇到的常見問題及解決方法

半導體發展的四個時代

半導體發展的四個時代

開關電源加載電流緩慢上升的解決方法

簡單認識功率金屬-氧化物-半導體場效應管

DC/DC開關電源的開關頻率雜散有什么有效的解決方法嗎?

意法半導體與理想汽車共筑電動汽車未來

化解先進半導體封裝挑戰,這個工藝不得不說

功率半導體器件學習筆記(1)

理想半導體開關的挑戰和簡單的解決方法

理想半導體開關的挑戰和簡單的解決方法

評論