總算是存在這樣一個問題,接收端差分線對之間可否加一匹配電阻?

首先還是要了解匹配電阻是個啥。

匹配電阻的作用. 在探測器或其它什么電路的輸入輸出部分,都有匹配電阻的要求,是用來使輸入輸出設備的電阻與電路其余部分銜接的,十分重要.如果匹配電阻不對,輸入輸出設備及電路無法正常工作(如測試數據不對). 在電路設計中,經常需要使用匹配電阻,如閉路電視同軸電纜、時鐘數據線等,如果阻抗不匹配會有什么不良后果呢?. 如果不匹配,則會形成反射,能量傳遞不過去,降低效率;會在傳輸線上形成駐波(簡單的理解,就是有些地方信號強,有些地方信號弱),導致傳輸線的有效功率容量降低;功率發射不出去,甚至會損壞發射設備。. 高速信號線中才考慮使用這樣的電阻,低頻情況下,一般是直接連接。

接收端差分線對間的匹配電阻通常會加, 其值應等于差分阻抗的值。這樣信號質量會好些。

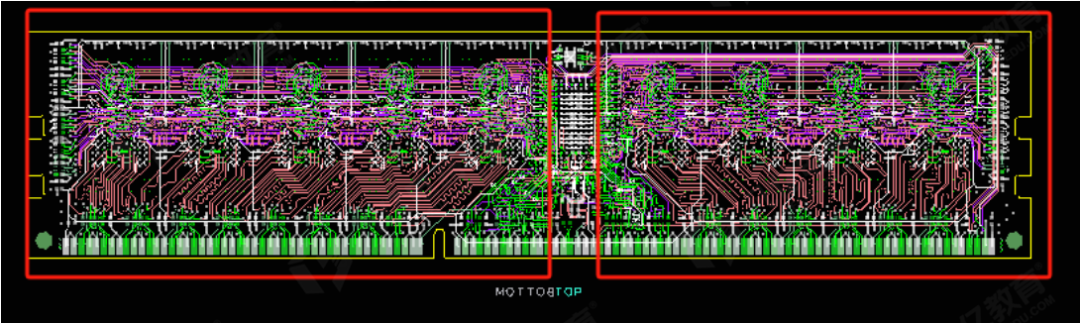

對差分對的布線方式應該要適當的靠近且平行。所謂適當的靠近是因為這間距會影響到差分阻抗(differential impedance)的值, 此值是設計差分對的重要參數。需要平行也是因為要保持差分阻抗的一致性。若兩線忽遠忽近, 差分阻抗就會不一致, 就會影響信號完整性(signal integrity)及時間延遲(timing delay)。

基本上, 將模/數地分割隔離是對的。要注意的是信號走線盡量不要跨過有分割的地方(moat),還有不要讓電源和信號的回流電流路徑(returning current path)變太大。

晶振是模擬的正反饋振蕩電路, 要有穩定的振蕩信號,必須滿足loop gain與phase 的規范, 而這模擬信號的振蕩規范很容易受到干擾,即使加ground guard traces可能也無法完全隔離干擾。而且離的太遠,地平面上的噪聲也會影響正反饋振蕩電路。所以,一定要將晶振和芯片的距離盡可能靠近。

確實高速布線與EMI的要求有很多沖突。但基本原則是因EMI所加的電阻電容或ferrite bead,不能造成信號的一些電氣特性不符合規范。所以,最好先用安排走線和PCB迭層的技巧來解決或減少EMI的問題,如高速信號走內層。最后才用電阻電容或ferrite bead的方式,以降低對信號的傷害。

審核編輯:湯梓紅

-

布線

+關注

關注

9文章

766瀏覽量

84294 -

差分信號

+關注

關注

3文章

367瀏覽量

27654 -

匹配電阻

+關注

關注

0文章

20瀏覽量

11452

發布評論請先 登錄

相關推薦

PCB設計高速差分信號的布線技巧

高速差分信號的經典布線技巧

差分信號PCB布局布線時的幾個常見誤區

基于差分信號的PCB布線優點和策略簡析

匹配電阻與差分信號布線方式

匹配電阻與差分信號布線方式

評論