Design Compiler軟件有四種模式,分別為:

? Wire Load Mode (Default)

? Topographical Mode

? Multimode

? UPF Mode

其中Wire Load Mode和Topographical Mode是工具模式,我們可以在啟動軟件的時候決定啟動哪種模式。如果用dc_shell或者design_vision后邊什么option不加,工具默認以Wire Load Mode啟動軟件。如果啟動軟件的時候后邊加上-topo或者-topographical_mode,則軟件以topo模式啟動。

另外兩種模式Multimode和UPF Mode并非工具啟動的模式而是topo下的兩種模式,分別支持多個工作條件、多個模式以及UPF低功耗。

Wire Load模式 - DC

在線負載模式(Wire Load Mode)下,工具使用Wire Load Model(線負載模型)來估算Wire上的Delay。

默認啟動DC的時候就是啟動Wire Load Mode:

dc_shell或者design_vision

這種模式在老的工藝下用的比較多,深亞微米下用的不太多,你可能會發現有些Foundary的庫里面已經沒有Wire Load Model了,對于大型Design,我們可以使用下面介紹的Topo模式。

Topo模式 - DCT

在拓撲模式(Topographical Mode)下,我們可以讀入一些物理Floorplan信息以及物理約束信息,DC也只有該模式可以讀入這些信息。在該模式下,工具不用借助Wire Load Model來估算Wire delay。因為有了物理信息,因此在邏輯綜合過程中,工具可以借助布局以及優化的技術來優化Timing、Power、Area,使得優化結果更加棒,另外和布局布線后的Timing結果也更加接近。

如前所述,在啟動dc的時候我們后邊加上-topo即可啟動topo模式:

dc_shell -topographical_mode

我們可以在topo模式下運行兩種編譯方法:

compile_ultra

這個大家應該都不陌生,下面著重講另一種DCG:

compile_ultra -spg

DCG(Design Compiler Graphical)

在DC的topo模式下,運行下面的命令進行綜合便會調用DCG:

compile_ultra -spg

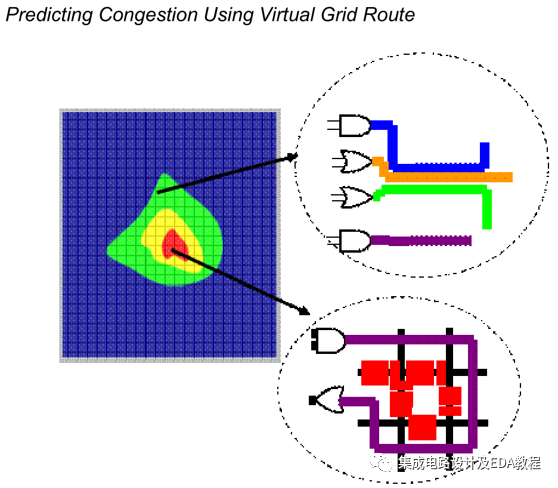

該命令在編譯過程中會使用DCG(Design Compiler Graphical)來對MCMM的Design進行優化,還可以優化Congestion(如下圖所示),做AHFS(Automatic High-Fanout Synthesis)來解邏輯DRC,提高與ICC/ICC2在PPA上的Correlation,優化ICC/ICC2中的runtime,另外我們還可以在DCG中使用Floorplan exploration創建以及修改Floorplan。

需要注意的是運行DCG需要DC Ultra和Design Compiler Graphical的license支持。

審核編輯:劉清

-

DCT

+關注

關注

1文章

56瀏覽量

19852 -

UPF

+關注

關注

0文章

49瀏覽量

13492 -

DCG

+關注

關注

0文章

7瀏覽量

2363

原文標題:DC、DCT與DCG

文章出處:【微信號:集成電路設計及EDA教程,微信公眾號:集成電路設計及EDA教程】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

伺服驅動器控制模式有哪幾種?

斷路器有哪幾種

STM32單片機有哪幾種常見的開發環境?

Design Compiler軟件有哪幾種模式

Design Compiler軟件有哪幾種模式

評論