在硬件設計過程中,當原理圖設計完成后需要提交EDA團隊進行PCB的繪制,其中傳輸線阻抗的控制是重要的一項內容。在提交PCB設計說明書時,需要對線寬/線間距做出要求;在PCB設計過程中,需要與EDA設計人員進行溝通,可能會對線寬/線間距、相鄰層厚度做適當調整;在提交PCB制版后,廠家會結合實際生產條件進行阻抗調整,這也需要硬件開發人員進行確認。因此,作為硬件開發人員,需要對傳輸線阻抗的原理和計算方法有所了解。傳輸線阻抗控制主要有兩種:單端阻抗和差分阻抗。單端阻抗的阻值一般控制在50歐姆左右,差分阻抗一般控制在100歐姆左右。接下來介紹傳輸線特征阻抗的等效模型,并結合具體單板PCB設計,介紹如何利用Polar Si9000工具進行特征阻抗的計算。

一、傳輸線的等效模型

1. 等效模型及參數

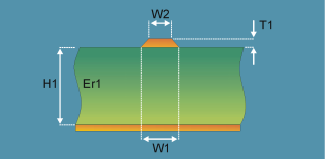

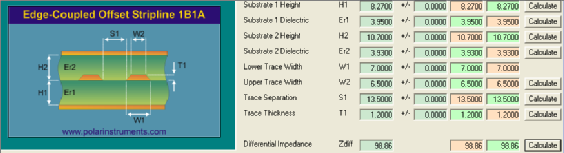

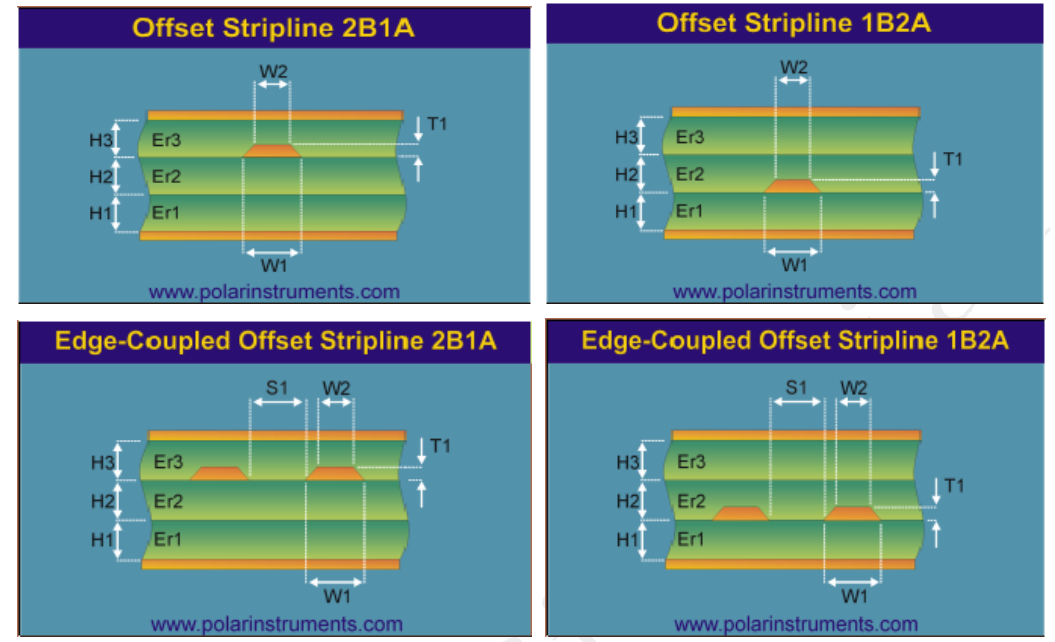

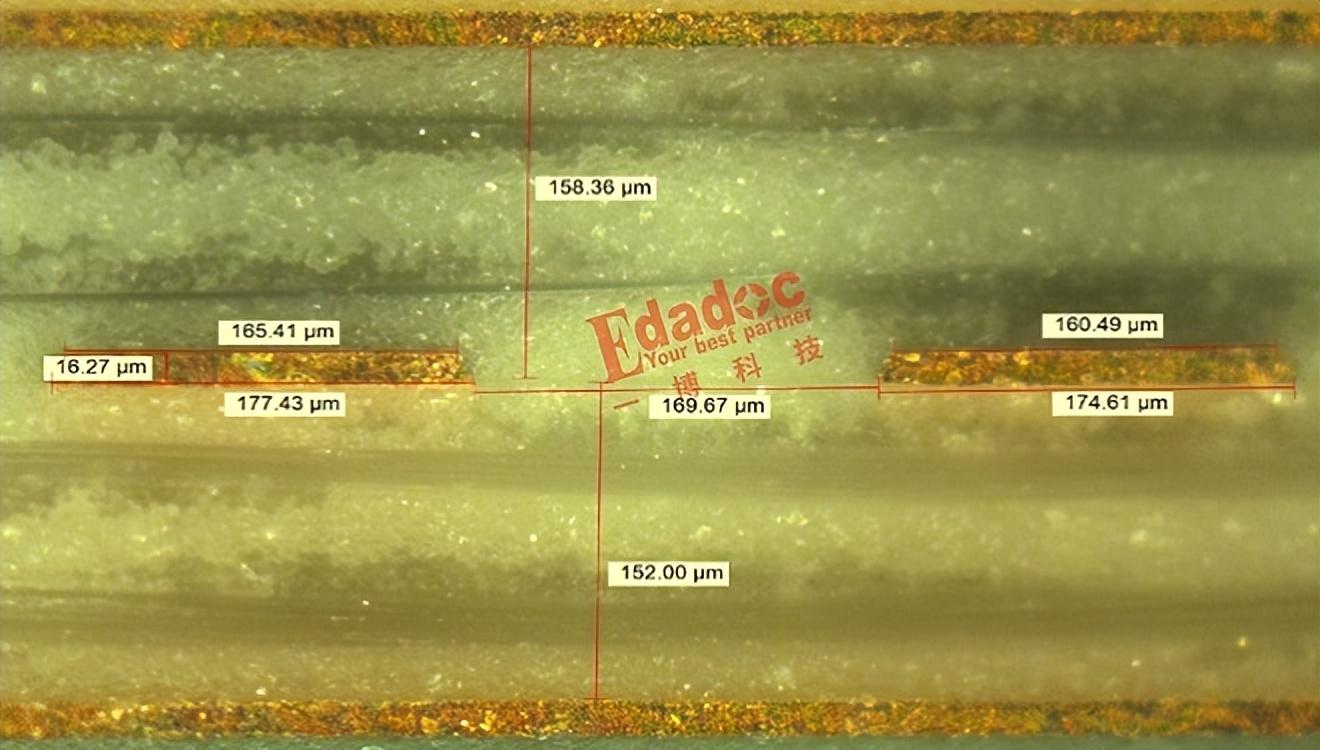

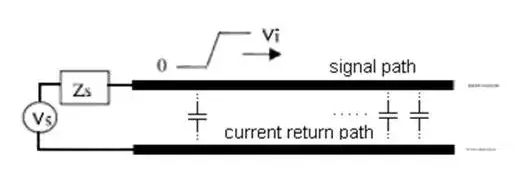

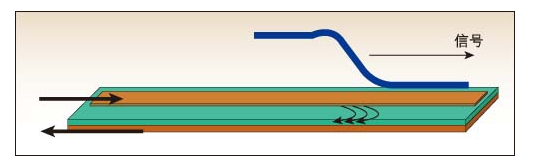

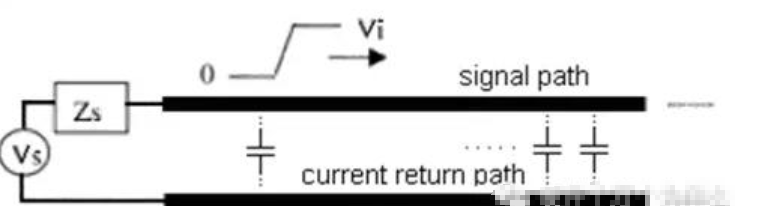

圖1:傳輸線等效模型傳輸線等效模型如圖1示,其中各參數如下:1、銅層厚度(T1)2、PCB板跡線的上下線寬(W2,W1)3、絕緣層厚度(H1)4、介電常數(Er1)5、若為差分線,則還有一個參數線間距(S1)。

圖1:傳輸線等效模型傳輸線等效模型如圖1示,其中各參數如下:1、銅層厚度(T1)2、PCB板跡線的上下線寬(W2,W1)3、絕緣層厚度(H1)4、介電常數(Er1)5、若為差分線,則還有一個參數線間距(S1)。2.參數說明

特征阻抗主要與線寬,絕緣層厚度等參數有關。線寬越大,特征阻抗越小;絕緣層越厚,相應的特征阻抗越大。阻抗控制采用以下參數:介質常數(Er1):4.0,FR4材料。下線寬(W1):設計線寬(假設為W);上線寬(W2):外層走線=W-1; 內層走線=W-0.5;銅層厚度(T1):分為表層與內層,如下表。需電鍍填銅層銅厚(表層):| 電鍍填銅層基銅銅厚(OZ) | 1/3 OZ | 1/2OZ | 1 OZ |

| 計算銅厚(mil) | 1.7 | 2.0 | 2.7 |

| 非電鍍填銅層銅厚(OZ) | 1/2OZ | 1 OZ | 1.5OZ |

| 計算銅厚(mil) | 0.6 | 1.2 | 2.56 |

二、具體計算實例:

計算所使用的PCB模型為某低速業務板工裝測試背板,有18層,其結構如下:表1:| L1 | --------------------------------------- | 0.5oz +電鍍 |

| PP 2116 4.495mil | ||

| L2 | 1oz | |

| CORE 0.21 8.27mil | ||

| L3 | --------------------------------------- | 1oz |

| PP 1080+7628 9.445mil | ||

| L4 | --------------------------------------- | 1oz |

| CORE 0.21 8.27mil | ||

| L5 | --------------------------------------- | 1oz |

| PP 1080+7628 9.445mil | ||

| L6 | --------------------------------------- | 1oz |

| CORE 0.21 8.27mil | ||

| L7 | --------------------------------------- | 1oz |

| PP 1080+7628 9.82mil | ||

| L8 | --------------------------------------- | 1oz |

| CORE 0.15 5.9mil | ||

| L9 | --------------------------------------- | 1oz |

| PP 3313 3.42mil | ||

| CORE 1(0.5oz) 37.99mil | ||

| PP 3313 3.37mil | ||

| L10 | --------------------------------------- | 1oz |

| CORE 0.15 5.9mil | ||

| L11 | --------------------------------------- | 1oz |

| PP 1080+7628 9.8325mil | ||

| L12 | --------------------------------------- | 1oz |

| CORE 0.21 8.27mil | ||

| L13 | --------------------------------------- | 1oz |

| PP 1080+7628 9.4575mil | ||

| L14 | --------------------------------------- | 1oz |

| CORE 0.21 8.27mil | ||

| L15 | --------------------------------------- | 1oz |

| PP 1080+7628 9.445mil | ||

| L16 | --------------------------------------- | 1oz |

| CORE 0.21 8.27mil | ||

| L17 | --------------------------------------- | 1oz |

| PP 2116 4.495mil | ||

| L18 | ---------------------------------------- | 0.5oz+電鍍 |

| 阻抗計算值 | ||||||

| 層別 | 調整線寬/線間距 | 計算值(ohm) | H1(mil) | Er1 | H2(mil) | Er2 |

| L1/18 | 7.6 mil to 7 mil | 49.6 | 4.5 | 3.95 | ||

| L1/18 | 7/13.5 mil to 5.9/14.6 mil | 98.3 | 4.5 | 3.95 | ||

| L3/16/5/14 | 7.6 mil | 49.6 | 8.27 | 3.95 | 10.7 | 3.93 |

| L3/16/5/14 | 7/13.5 mil | 98.1 | 8.27 | 3.95 | 10.7 | 3.93 |

| L7/12 | 7.6 mil | 50 | 8.27 | 3.95 | 11.07 | 3.93 |

| L7/12 | 7/13.5 mil | 98.7 | 8.27 | 3.95 | 11.07 | 3.93 |

| L9/10 | 7.6 mil to 8 mil | 51.5 | 5.9 | 3.65 | 53.18 | 3.89 |

| L9/10 | 7/13.5 mil | 99.1 | 5.9 | 3.65 | 53.18 | 3.89 |

| L9的屏蔽層為: | L8/L11 | |||||

| L10的屏蔽層為: | L8/L11 | |||||

| 其他層鄰層屏蔽 | ||||||

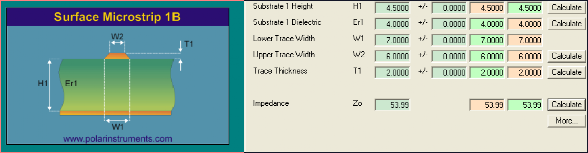

2.1 表層(L1/L18)單端阻抗計算:(單位:mil)

參數說明:H1為絕緣層的厚度4.5mil;W1= 7.0mil;W2= W1-1=6.0mil;T1=2. 0 mil;Er1=4;計算結果:Z0=53.99歐姆。加工后的實際阻抗應為:Z0′=Z0-3=50.99歐姆與廠家所給出的阻抗值基本一致。

參數說明:H1為絕緣層的厚度4.5mil;W1= 7.0mil;W2= W1-1=6.0mil;T1=2. 0 mil;Er1=4;計算結果:Z0=53.99歐姆。加工后的實際阻抗應為:Z0′=Z0-3=50.99歐姆與廠家所給出的阻抗值基本一致。2.2表層(L1/L18)差分線阻抗計算:(單位:mil)

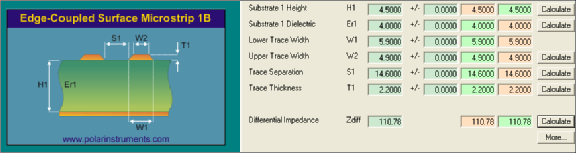

參數說明:H1為絕緣層的厚度4.5mil;W1= 5.9mil;W2=4.9mil;S1= 14.6 mil;T1=2.2mil;Er1=4;計算結果:Z0=110.78歐姆。加工后的實際阻抗應為:Z0′=Z0-9=101.78歐姆與廠家所給出的阻抗值基本一致。

參數說明:H1為絕緣層的厚度4.5mil;W1= 5.9mil;W2=4.9mil;S1= 14.6 mil;T1=2.2mil;Er1=4;計算結果:Z0=110.78歐姆。加工后的實際阻抗應為:Z0′=Z0-9=101.78歐姆與廠家所給出的阻抗值基本一致。2.3內層(L3/L10)單端阻抗計算:(單位:mil)

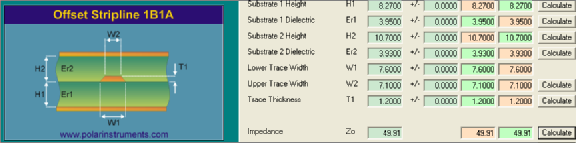

以L3層為例,參數設置如下: 參數說明:H1為絕緣層厚度8.27mil。Er1為3.95;W1=7.6 mil;W2= W1-0.5=7.1mil;T1=1.2mil;Er2 =3.93;H2為芯板的厚度加上銅箔的厚度為10.7mil計算結果:Z0=49.91歐姆。與廠家所給出的阻抗值基本一致。

參數說明:H1為絕緣層厚度8.27mil。Er1為3.95;W1=7.6 mil;W2= W1-0.5=7.1mil;T1=1.2mil;Er2 =3.93;H2為芯板的厚度加上銅箔的厚度為10.7mil計算結果:Z0=49.91歐姆。與廠家所給出的阻抗值基本一致。2.4內層差分線(L3/L10)阻抗計算: (單位:mil)

以L3層為例,參數設置如下: 參數說明:H1為絕緣層的厚度8.27mil。Er1為3.95;W1 =7 mil;W2= W1-0.5=6.5mil;S1 =13.5 mil;T1=1.2mil;Er2 =3.93;H2為絕緣層的厚度加上銅箔的厚度,為10.7mil計算結果:Z0=98.86歐姆。與廠家所給出的阻抗值基本一致。

參數說明:H1為絕緣層的厚度8.27mil。Er1為3.95;W1 =7 mil;W2= W1-0.5=6.5mil;S1 =13.5 mil;T1=1.2mil;Er2 =3.93;H2為絕緣層的厚度加上銅箔的厚度,為10.7mil計算結果:Z0=98.86歐姆。與廠家所給出的阻抗值基本一致。2.5 相鄰信號層的阻抗計算

理論上相鄰信號層的阻抗計算應該用如下模型,如第9第10兩層。但是這樣非常繁瑣,可以簡化成2.3,2.4中所述的模型,實際廠家給出的參數也證明了這一點。只要將H1,H2,Er1 ,Er1作相應調整即可,具體參數見表1,表2中所示。

三、總結

本文介紹了傳輸線特征阻抗的等效模型,并結合具體單板PCB設計,介紹了利用Polar Si9000工具計算特征阻抗的方法,希望能對大家有所幫助。審核編輯 :李倩

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

阻抗

+關注

關注

17文章

940瀏覽量

45821 -

PCB設計

+關注

關注

394文章

4670瀏覽量

85287 -

傳輸線

+關注

關注

0文章

375瀏覽量

23998

原文標題:【PCB設計】傳輸線特征阻抗的計算方法及實例

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

為什么選擇hdmi光纖傳輸線

HDMI光纖傳輸線,也稱為光纖HDMI線或HDMI光纖線,是一種通過光纖傳輸高清視頻和音頻信號的設備。它采用了光纖技術,具有以下主要優勢: 高傳輸

輸入阻抗、輸出阻抗、阻抗匹配到底是個啥?

在原信號上將會改變原信號的形狀。如果傳輸線的特征阻抗跟負載阻抗不相等(即不匹配)時,在負載端就會產生反射。為什么阻抗不匹配時會產生反射以及

發表于 06-01 08:08

掌握了這個分析方法,實現傳輸線阻抗5%的加工公差不是夢!

高速先生成員--黃剛

傳輸線阻抗控制對系統性能的重要性不言而喻,每一家的PCB加工板廠都在往能控制更嚴格的阻抗公差這個目標而不斷努力。但是我們也知道,傳輸線

發表于 03-25 18:05

掌握了這個分析方法,實現傳輸線阻抗5%的加工公差不是夢!

傳輸線結構很多因素都會影響阻抗,例如線寬、介質厚度、介電常數、銅厚等,那大家有沒有想過到底哪個因素最影響阻抗呢?學會了本文的分析方法,或許有一天阻抗加工公差控制到5%也很可能哦!

信號傳輸使用傳輸電纜的電路原理

不同電平不同速率的信號傳輸。請問有關信號線傳輸理論在哪本書里,與電磁波和電磁場的聯系大不大?在應用中主要是利用了傳輸線的那些優點,傳輸線材質

發表于 01-30 13:59

PCB的傳輸線結構

傳輸線的定義是有信號回流的信號線(由兩條一定長度導線組成,一條是信號傳播路徑,另一條是信號返回路徑。),很常見的傳輸線也就是我們PCB板上的走線。

發表于 01-15 15:13

?334次閱讀

如何解決PCB設計總是有阻抗不連續?

如果傳輸線是各向同性的,那么只要信號在傳輸,就始終存在一個電流 I,而如果信號的輸出電壓為 V,在信號傳輸過程中,傳輸線就會等效成一個電阻,

發表于 01-09 16:15

?296次閱讀

高速PCB設計基礎知識:傳輸線

傳輸線的定義是有信號回流的信號線(由兩條一定長度導線組成,一條是信號傳播路徑,另一條是信號返回路徑。),常見的傳輸線也就是我們PCB板上的走線。

發表于 01-02 15:36

?383次閱讀

傳輸線特征阻抗的等效模型

傳輸線特征阻抗的等效模型

評論