數字IC是傳遞、加工、處理數字信號的集成電路(Integrated Circuit, IC), 一般將其分為通用數字IC和專用數字IC。

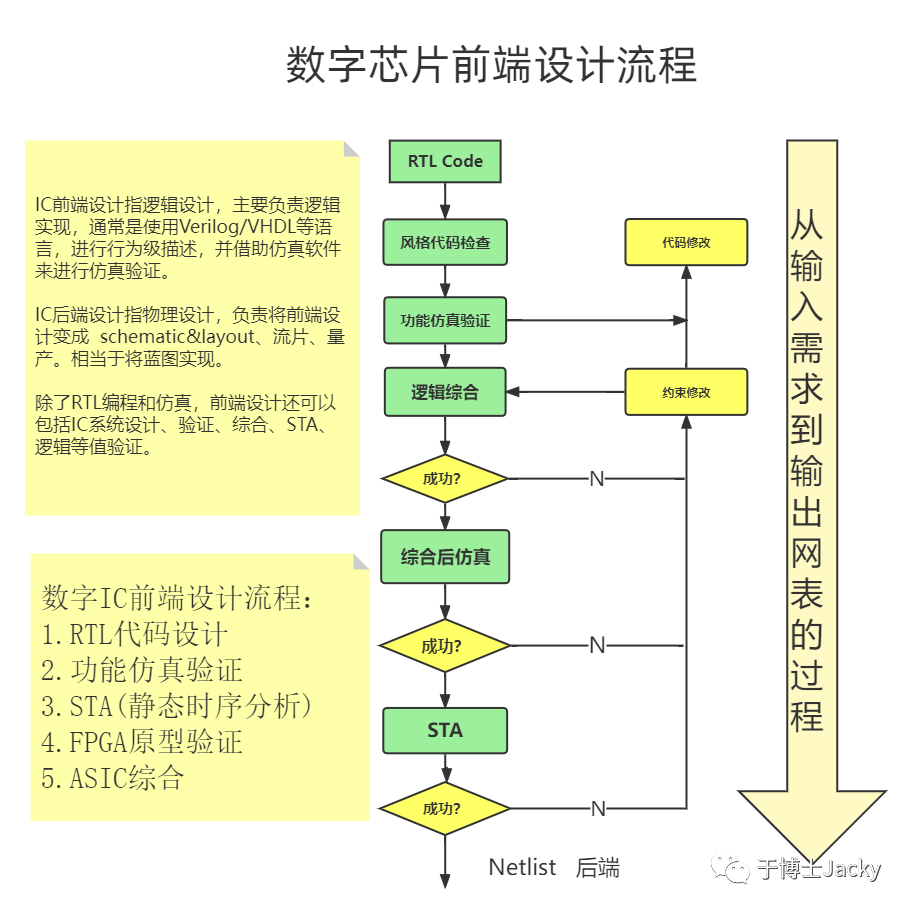

數字IC前端設計,以架構設計為起點,以生成可布局布線的網表級為終點。該過程主要包括:TRL編程、仿真驗證、邏輯綜合(Design Compiler)、靜態時序分析(STA)、形式驗證(Formality)。

1.RTL代碼設計

使用硬件描述語言(HDL )將功能以代碼的形式描述實現,形成RTL代碼。

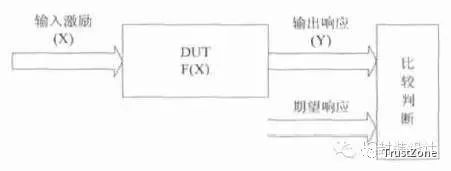

2.功能仿真驗證

檢驗RTL級的代碼設計的正確性。

常用工具:Mentor公司的Modelsim、Synopsys的VCS、Cadence的NC-Verilog等。

3.STA(靜態時序分析)

靜態時序分析屬于驗證范疇,指的是在時序上對電路進行驗證,檢查電路是否存在建立時間(setup time)和保持時間(hold time)的違例(violation)。

常用工具:Synopsys的Prime Time。

4.邏輯綜合

將HDL代碼翻譯成門級網表Netlist。

常用工具:Synopsys的Design Compiler。

5.形式驗證(Formality)

為保證在邏輯綜合過程中不改變原先HDL描述的電路功能,在功能上對綜合后的網表進行的驗證,就是形式驗證。

常用方法:等價性檢查方法。即以功能驗證后的HDL設計為參考,對比綜合后的網表功能,驗證它們是否在功能上存在等價性。

常用工具:Synopsys的Formality。

審核編輯:劉清

-

集成電路

+關注

關注

5365文章

11159瀏覽量

358339 -

數字信號處理

+關注

關注

15文章

539瀏覽量

45690 -

數字IC

+關注

關注

1文章

37瀏覽量

12414

原文標題:一圖懂!數字IC設計前端設計流程

文章出處:【微信號:于博士Jacky,微信公眾號:于博士Jacky】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【書籍評測活動NO.40】數字IC設計入門,多角度透視芯片設計

VSP2560/62/66數字相機混合信號處理IC數據表

過電壓和過電流保護IC和Li+充電器前端保護IC bq2431x數據表

半導體IC設計是什么?IC設計和芯片設計區別

fpga和數字ic區別 fpga和plc區別

數字IC設計入門經典書籍合集推薦

ic是什么電子器件 ic指的是哪些元器件

數字IC與模擬IC的架構差異

數字ic測試系統有什么特點?如何助力車載mcu芯片測試?

ADTR1007: 6千兆赫至18千兆赫,前端IC數據表 ADI

數字IC與數字IC前端設計

數字IC與數字IC前端設計

評論