這篇文章講述了如何用工具提高效率的方法,適用程度因人而異。

Situation:在對FPGA 設計進行最初步的系統規劃的時候,需要進行模塊劃分,模塊接口定義等工作。通常,我們起初會在紙上進行設計,到了一定階段的定稿可能會輸入Visio 等工具,方便在Team 內部交流和審閱。雖然在紙上我們可以很隨意地書寫,而用紙畫的不方便就在于,如果想對某一個模塊進行一些改動或者重畫模塊,那么常常因為留出的空余紙張不夠,而導致拿一張新的白紙重新畫一遍,比較浪費時間。對于電子化的Visio 來說,方便修改是好處,但他不是專為設計FPGA 系統而設計的,添加輸入輸出端口沒那么方便,也不會根據定義的模塊自動生成HDL文件。

HDLQuestion:我們能不能使用更好軟件進行系統規劃呢?

Solution:答案是可以的。下面以ISE 10.1 為例作說明:

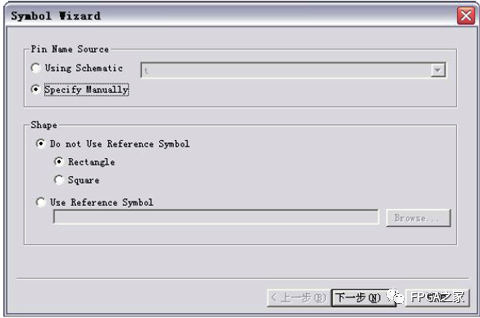

1) 畫一個空模塊,僅定義端口 - 新建Schematic,選擇Tools -> Symbol Wizard,里面可以定義Symbol名和端口屬性。完成后生成sym 格式的Symbol。如果端口是一個bus,那么可以用A(4:0) 的形式。

2) 將Symbol 添加到原理圖 - 在Schematic 的Symbol 頁面,選擇Categories 為工程文件夾,在Symbols列表中就可以看到剛剛新建的Symbol。將它添加到原理圖中。

3) 重復1-2 步驟,建立所有Symbol,并連接端口。如果需要修改連線的名字或者模塊的例化名,可以選擇需要修改名字的元件然后按右鍵--> Object Properties --> 在Name/InstName 窗格中填入需要的名字。

4) 如需修改Symbol,可以直接在sym 文件中修改 - 可以按右鍵-> Add -> Pin 等等添加,也可以Copy已存在的Pin,然后改變PinName。但是ISE10.1 的Symbol Editor 對Add Pin 有一些Bug。因此在UltraEditor打開這個sym 文件,在里面修改可能是更好的辦法。sym 文件格式很易懂。改變 Symbol 端口后需要UpdateSchematic。在點到Schematic 后會自動彈出Update 對話框。

5) 生成原理圖對應的HDL 文件 - 點擊"Sources in Project" 列表中的sch 文件,在"Process" 窗口選擇"View HDL Functional Model"。這樣會自動生成Schematic 對應的HDL 文件,其中例化了上面的各個模塊。要改變HDL文件類型,可以改變Project 屬性中的"Generated Simulation Language" 屬性。

6) 生成Symbol 對應的HDL 文件 - 在打開一個sym 文件時,選擇Tools -> Generate HDL Template from Symbol。此時可以選擇生成VHDL 還是Verilog 的文件。

至此,我們已經生成了頂層文件和待開發的子模塊文件,我們已經可以在它的基礎上進行開發了。在開發過程中我們可能還會碰到這些問題:

1. 我想把設計圖打印下來- 除了ISE 自帶的打印功能外,要打印好看的圖紙,還可以使用Synplify Pro或PlanAhead。由于以上流程生成的代碼都是可綜合的,帶有端口信息的HDL 會被綜合工具認為是一個blackbox的wrapper,因此我們可以用ISE 或Synplify 將這些代碼綜合,綜合工具會生成比較好看的綜合模塊圖(RTL Schematic)。除了可以用ISE 和Synplify 打開這些綜合網表產生RTL Schematic 之外,也可以用PlanAhead 打開綜合網表,它的Schematic 顯示功能更為強大。

2. 我要修改某些模塊的端口,并添加連線修改模塊端口是否還需要在原來的Schematic 上編輯修改呢?這是仁者見仁智者見智的問題了。我個人在生成了帶端口信息的HDL 后還是偏好修改HDL --> 綜合 --> 在PlanAhead 中產生需要的連接圖 --> 打印 --> 在打印稿上繼續思考寫寫劃劃 --> 繼續修改HDL 這樣的流程。

5.3.綜合和仿真技巧

作者:田耘/云創工作室

5.3.1 綜合工具XST的使用

所謂綜合,就是將HDL語言、原理圖等設計輸入翻譯成由與、或、非門和RAM、觸發器等基本邏輯單元的邏輯連接( 網表),并根據目標和要求( 約束條件) 優化所生成的邏輯連接,生成EDF 文件。XST 內嵌在ISE 3 以后的版本中,并且在不斷完善。此外,由于XST 是賽靈思公司自己的綜合工具,對于部分賽靈思芯片獨有的結構具有更好的融合性。

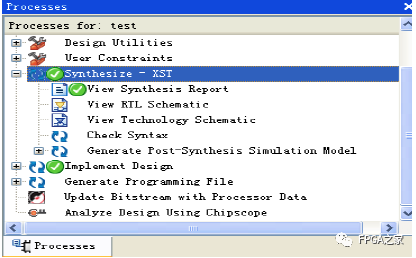

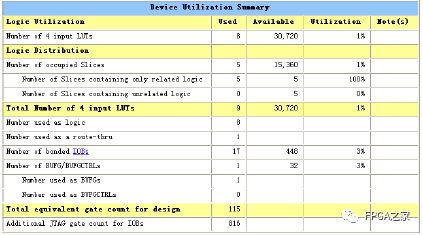

完成了輸入、仿真以及管腳分配后就可以進行綜合和實現了。在過程管理區雙擊Synthesize-XST,如圖5-1所示,就可以完成綜合,并且能夠給出初步的資源消耗情況。圖5-2 給出了模塊所占用的資源。

圖5-1 設計綜合窗口

圖5-2 綜合結果報告

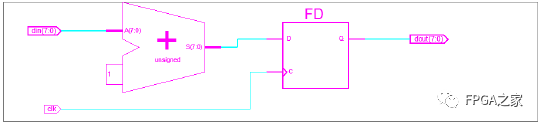

綜合可能有3 種結果:如果綜合后完全正確,則在Synthesize-XST 前面有一個打鉤的綠色小圈圈;如果有警告,則出現一個帶感嘆號的黃色小圓圈;如果有錯誤,則出現一個帶叉的紅色小圈圈。綜合完成之后,可以通過雙擊View RTL Schematics 來查看RTL 級結構圖,察看綜合結構是否按照設計意圖來實現電路。ISE 會自動調用原理圖編輯器ECS 來瀏覽RTL 結構。對于一個計數器,其RTL 結構圖如圖5-3 所示,綜合結果符合設計者的意圖,調用了加法器和寄存器來完成邏輯。

圖5-3 經過綜合后的RTL級結構圖

2.綜合參數的設置

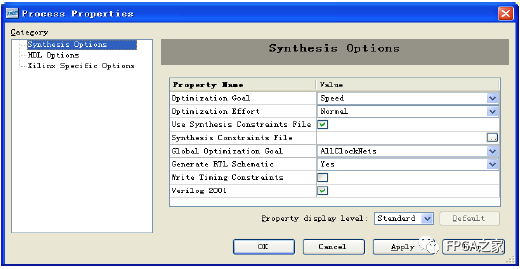

一般在使用XST 時,所有的屬性都采用默認值。其實XST 對不同的邏輯設計可提供豐富、靈活的屬性配置。下面對ISE9.1 中內嵌的XST 屬性進行說明。打開ISE 中的設計工程,在過程管理區選中“Synthesis –XST”并單擊右鍵,彈出界面如圖5-4 所示。

圖5-4 綜合選項

由圖5-4 可以看出,XST 配置頁面分為綜合選項(Synthesis Options)、HDL 語言選項(HDL Options) 以及賽靈思特殊選項(Xilinx Specific Options) 等三大類,分別用于設置綜合的全局目標和整體策略、HDL 硬件語法規則以及賽靈思特有的結構屬性。

1) 綜合選項參數

綜合參數配置界面如圖5-4 所示,包括8 個選項,具體如下所列:

【Optimization Goal】:優化的目標。該參數決定了綜合工具對設計進行優化時,是以面積還是以速度作為優先原則。面積優先原則可以節省器件內部的邏輯資源,即盡可能地采用串行邏輯結構,但這是以犧牲速度為代價的。而速度優先原則保證了器件的整體工作速度,即盡可能地采用并行邏輯結構,但這樣將會浪費器件內部大量的邏輯資源,因此,它是以犧牲邏輯資源為代價的。

【Optimization Effort】:優化器努力程度。這里有【normal】和【high】兩種選擇方式。對于【normal】,優化器對邏輯設計僅僅進行普通的優化處理,其結果可能并不是最好的,但是綜合和優化流程執行地較快。如果選擇【high】,優化器對邏輯設計進行反復的優化處理和分析,并能生成最理想的綜合和優化結果,在對高性能和最終的設計通常采用這種模式;當然在綜合和優化時,需要的時間較長。

【Use Synthesis Constraints File】:使用綜合約束文件。如果選擇了該選項,那么綜合約束文件XCF 有效。

【Synthesis Constraints File】:綜合約束文件。該選項用于指定XST 綜合約束文件XCF 的路徑。

【Global Optimization Goal】:全局優化目標。可以選擇的屬性包括有【AllClockNets】、【Inpad To

Outpad】、【Offest In Before】、【Offest Out After】、【Maximm Delay】。該參數僅對FPGA 器件有效,可用于選擇所設定的寄存器之間、輸入引腳到寄存器之間、寄存器到輸出引腳之間,或者是輸入引腳到輸出引腳之間邏

輯的優化策略。

【Generate RTL Schematic】:生成寄存器傳輸級視圖文件。該參數用于將綜合結果生成RTL 視圖。

【Write Timing Constraints】:寫時序約束。該參數僅對FPGA 有效,用來設置是否將HDL 源代碼中用于控制綜合的時序約束傳給NGC 網表文件,該文件用于布局和布線。

【Verilog 2001】:選擇是否支持Verilog 2001 版本。

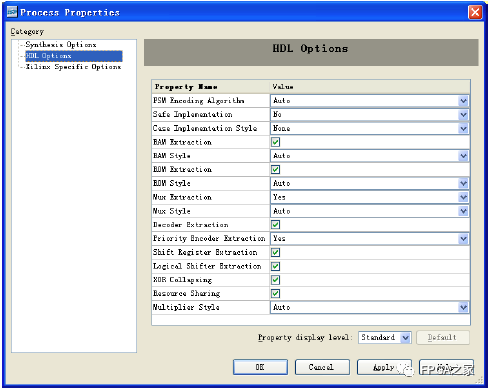

HDL語言選項

HDL 語言選項的配置界面如圖5-5 所示,包括16 個選項,具體如下所列:

圖5-5 HDL語言選項的配置界面選項

【FSM Encoding Algorithm】:有限狀態機編碼算法。該參數用于指定有限狀態機的編碼方式。選項有【Auto】、

【One-Hot】、【Compact】、【Sequential】、【Gray】、【Johnson】、【User】、【Speed1】、【None】編碼方式,默認為【Auto】編碼方式。

【Safe Implementation】:將添加安全模式約束來實現有限狀態機,將添加額外的邏輯將狀態機從無效狀態

調轉到有效狀態,否則只能復位來實現,有【Yes】、【No】兩種選擇,默認為【No】。

【Case Implementation Sytle】:條件語句實現類型。該參數用于控制XST 綜合工具解釋和推論Verilog 的

條件語句。其中選項有【None】、【Full】、【Parallel】、【Full-Parallel】,默認為【None】。對于這四種選項,區別如下:(1)【None】,XST 將保留程序中條件語句的原型,不進行任何處理;(2)【Full】,XST 認為條件語句是完整的,避免鎖存器的產生;(3)【Parallel】,XST 認為在條件語句中不能產生分支,并且不使用優先級編碼器;(4)【Full-Parallel】,XST 認為條件語句是完整的,并且在內部沒有分支,不使用鎖存器和優先級編碼器。

【RAM Extraction】:存儲器擴展。該參數僅對FPGA 有效,用于使能和禁止RAM 宏接口。默認為允許使用RAM 宏接口。

【RAM Style】:RAM 實現類型。該參數僅對FPGA 有效,用于選擇是采用塊RAM 還是分布式RAM 來作為RAM 的實現類型。默認為【Auto】。

【ROM Extraction】:只讀存儲器擴展。該參數僅對FPGA 有效,用于使能和禁止只讀存儲器ROM 宏接口。默認為允許使用ROM 宏接口。

【ROM Style】:ROM 實現類型。該參數僅對FPGA 有效,用于選擇是采用塊RAM 還是分布式RAM 來作為ROM 的實現和推論類型。默認為【Auto】。

【Mux Extraction】:多路復用器擴展。該參數用于使能和禁止多路復用器的宏接口。根據某些內定的算法,對于每個已識別的多路復用/ 選擇器,XST 能夠創建一個宏,并進行邏輯的優化。可以選擇【Yes】、【No】和【Force】

中的任何一種,默認為【Yes】。

【Mux Style】:多路復用實現類型。該參數用于胃宏生成器選擇實現和推論多路復用/ 選擇器的宏類型。可以選擇【Auto】、【MUXF】和【MUXCY】中的任何一種,默認為【Auto】。

【Decoder Extraction】:譯碼器擴展。該參數用于使能和禁止譯碼器宏接口,默認為允許使用該接口。

【Priority Encoder Extraction】:優先級譯碼器擴展。該參數用于指定是否使用帶有優先級的編碼器宏單元。

【Shift Register Extraction】:移位寄存器擴展。該參數僅對FPGA 有效,用于指定是否使用移位寄存器宏單元。默認為使能。

【Logical Shifter Extraction】:邏輯移位寄存器擴展。該參數僅對FPGA 有效,用于指定是否使用邏輯移位寄存器宏單元。默認為使能。

【XOR Collapsing】:異或邏輯合并方式。該參數僅對FPGA 有效,用于指定是否將級聯的異或邏輯單元合并成一個大的異或宏邏輯結構。默認為使能。

【Resource Sharing】:資源共享。該參數用于指定在XST 綜合時,是否允許復用一些運算處理模塊,如加法器、減法器、加/ 減法器和乘法器。默認為使能。如果綜合工具的選擇是以速度為優先原則的,那么就不考慮資源共享。

【Multiplier Style】:乘法器實現類型。該參數僅對FPGA 有效,用于指定宏生成器使用乘法器宏單元的方式。選項有【Auto】、【Block】、【LUT】和【Pipe_LUT】。默認為【Auto】。選擇的乘法器實現類型和所選擇的器件有關。

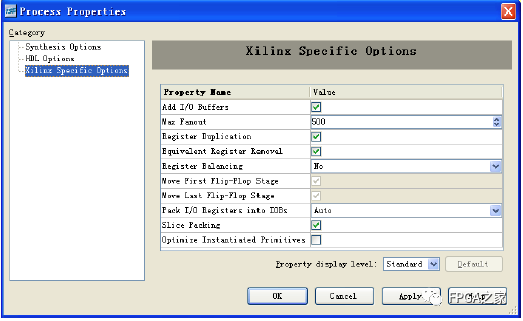

2) 賽靈思特殊選項

賽靈思特殊選項用于將用戶邏輯適配到賽靈思芯片的特殊結構中,不僅能節省資源,還能提高設計的工作頻率,其配置界面如圖5-6 所示,包括10 個配置選項,具體如下所列。

圖5-6 賽靈思指定的選項

【Add I/O Buffers】:插入I/O 緩沖器。該參數用于控制對所綜合的模塊是否自動插入I/O 緩沖器。默認為自動插入。

【Max Fanout】:最大扇出數。該參數用于指定信號和網線的最大扇出數。這里扇出數的選擇與設計的性能有直接的關系,需要用戶合理選擇。

【Register Duplication】:寄存器復制。該參數用于控制是否允許寄存器的復制。對于高扇出和時序不能滿足要求的寄存器進行復制,可以減少緩沖器輸出的數目以及邏輯級數,改變時序的某些特性,提高設計的工作頻率。默認為允許寄存器復制。

【Equivalent Register Removal】:等效寄存器刪除。該參數用于指定是否把寄存器傳輸級功能等效的寄存器刪除,這樣可以減少寄存器資源的使用。如果某個寄存器是用賽靈思的硬件原語指定的,那么就不會被刪除。默認為使能。

【Register Balancing】:寄存器配平。該參數僅對FPGA 有效,用于指定是否允許平衡寄存器。可選項有【No】、【Yes】、【Forward】和【Backward】。采用寄存器配平技術,可以改善某些設計的時序條件。其中【Forward】

為前移寄存器配平,【Backward】為后移寄存器配平。采用寄存器配平后,所用到的寄存器數就會相應地增減。默認為寄存器不配平。

【Move First Flip-Flop Stage】:移動前級寄存器。該參數僅對FPGA 有效,用于控制在進行寄存器配平時,是否允許移動前級寄存器。如果【Register Balancing】的設置為【No】,那么該參數的設置無效。

【Move Last Flip-Flop Stage】:移動后級寄存器。該參數僅對FPGA 有效,用于控制在進行寄存器配平時,是否允許移動后級寄存器。如果【Register Balancing】的設置為【No】,那么該參數的設置無效。

【Pack I/O Registers into IOBs】:I/O 寄存器置于輸入輸出塊。該參數僅對FPGA 有效,用于控制是否將邏輯設計中的寄存器用IOB 內部寄存器實現。在賽靈思系列FPGA 的IOB 中分別有輸入和輸出寄存器。如果將設計中的第一級寄存器或最后一級寄存器用IOB 內部寄存器實現,那么就可以縮短IO 引腳到寄存器之間的路徑,這通常可以縮短大約1~2ns 的傳輸時延。默認為【Auto】。

【Slice Packing】:優化Slice 結構。該參數僅對FPGA 有效,用于控制是否將關鍵路徑的查找表邏輯盡量配置在同一個Slice 或者CLB 模塊中,由此來縮短LUT 之間的布線。這一功能對于提高設計的工作頻率、改善時序特性是非常有用的。默認為允許優化Slice 結構。

【Optimize Instantiated Primitives】:優化已例化的原語。該參數控制是否需要優化在HDL 代碼中已例化的原語。默認為不優化。

在代碼編寫完畢后,需要借助于測試平臺來驗證所設計的模塊是否滿足要求。ISE 提供了兩種測試平臺的建立方法,一種是使用HDL Bencher 的圖形化波形編輯功能編寫,另一種就是利用HDL 語言,相對于前者使用簡單、功能強大。下面介紹基于Verilog 語言建立測試平臺的方法。

首先在工程管理區將“Sources for”設置為Behavioral Simulation,在任意位置單擊鼠標右鍵,并在彈出的菜單中選擇“New Source”命令,然后選中“Verilog Test Fixture”類型,輸入文件名為“test_test”,再點擊“Next”進入下一頁。這時,工程中所有Verilog Module 的名稱都會顯示出來,設計人員需要選擇要進行測試的模塊。

用鼠標選中test,點擊“Next”后進入下一頁,直接點擊“Finish”按鍵,ISE 會在源代碼編輯區自動顯示測試模塊的代碼:

`timescale 1ns / 1ps

module test_test_v;

// Inputs

reg clk;

reg [7:0] din;

// Outputs

wire [7:0] dout;

// Instantiate the Unit Under Test (UUT)

test uut (

.clk(clk),

.din(din),

.dout(dout)

);

initial begin

// Initialize Inputs

clk = 0;

din = 0;

// Wait 100 ns for global reset to finish

#100;

// Add stimulus here

end

endmodule

由此可見,ISE 自動生成了測試平臺的完整架構,包括所需信號、端口聲明以及模塊調用的完成。所需的工作就是在initial…end 模塊中的“// Add stimulus here”后面添加測試向量生成代碼。添加的測試代碼如下:

forever begin

#5;

clk = !clk;

if(clk == 1)

din = din + 1;

else

din = din;

end

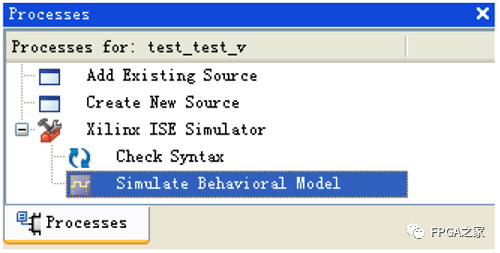

完成測試平臺后。在工程管理區將“Sources for”選項設置為Behavioral Simulation,這時在過程管理區會顯示與仿真有關的進程,如圖5-7 所示。

圖5-7 仿真過程示意圖

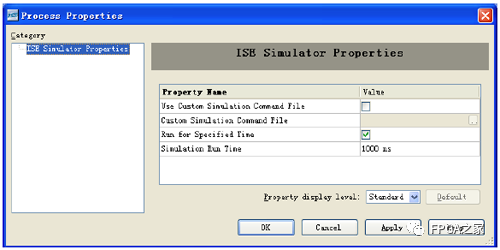

選中圖5-7 中Xilinx ISE Simulator 下的Simulate Behavioral Model 項,點擊鼠標右鍵,選擇彈出菜單的Properties項,會彈出如圖5-8 所示的屬性設置對話框,最后一行的Simulation Run Time 就是仿真時間的設置,可將其修改為任意時長,本例采用默認值。

圖5-8 仿真屬性設置對話框

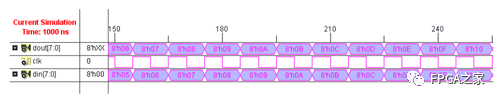

仿真參數設置完后,就可以進行仿真了,直接雙擊ISE Simulator 軟件中的Simulate Behavioral Model,則ISE 會自動啟動ISE Simulator 軟件,并得到如圖5-9所示的仿真結果,從中可以看到設計達到了預計目標。

-

FPGA設計

+關注

關注

9文章

428瀏覽量

26487 -

接口

+關注

關注

33文章

8504瀏覽量

150847 -

HDL

+關注

關注

8文章

327瀏覽量

47341

原文標題:FPGA開發全攻略——ISE基本操作

文章出處:【微信號:FPGA研究院,微信公眾號:FPGA研究院】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

明德揚視頻分享點撥FPGA課程--第二十章??提高效率技巧

如何使用UCC28056優化過渡模式PFC設計來提高效率和待機功耗?

keil5提高效率的技巧

卡套管的使用有助于提高效率并達到更合格的標準

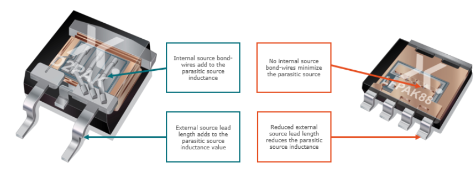

LFPAK88是提高效率的捷徑

NIKKEI邏輯整合Brocade SAN以提高效率和安全性

提高效率的DC電源模塊設計技巧

如何用ISE工具提高效率

如何用ISE工具提高效率

評論