雖然比較器的概念很簡(jiǎn)單,但在實(shí)現(xiàn)過程中會(huì)有幾個(gè)常見的設(shè)計(jì)挑戰(zhàn)。為了應(yīng)對(duì)這些挑戰(zhàn),本文將介紹設(shè)計(jì)人員為實(shí)現(xiàn)出色的比較器性能而必須應(yīng)對(duì)的三個(gè)最常見設(shè)計(jì)注意事項(xiàng) - 從顫振開始。

什么是顫振?

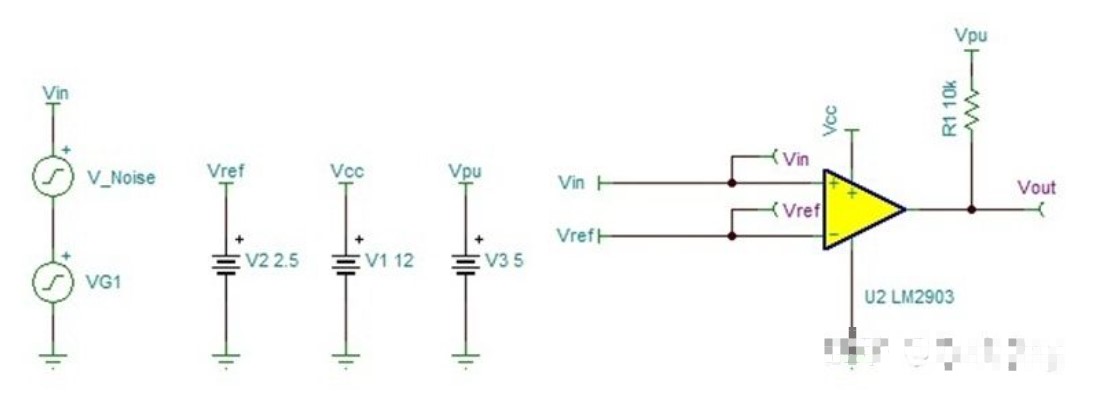

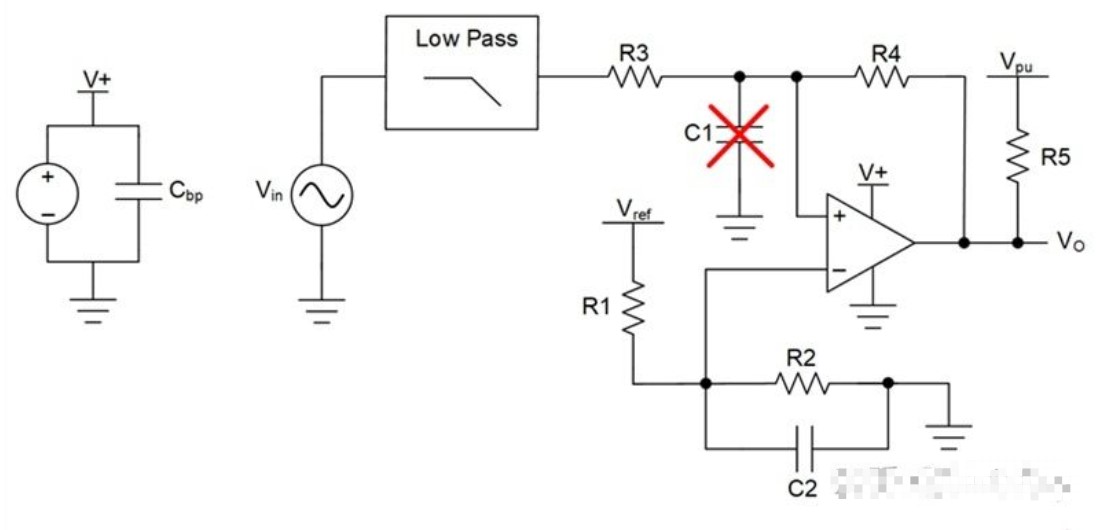

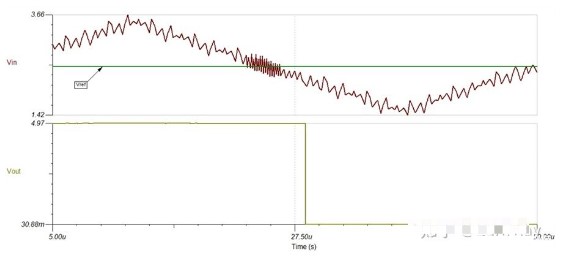

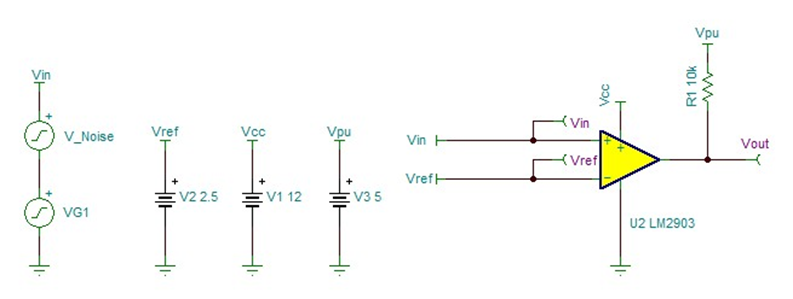

為了演示顫振現(xiàn)象,將 LM2903 雙路差分比較器設(shè)置為同相配置(圖 1),將噪聲添加到以基準(zhǔn)電壓 (VREF) 為中心的 1V 峰峰值三角波中。當(dāng)輸入電壓 (VIN) 接近 IN– 上的基準(zhǔn)電壓時(shí),會(huì)出現(xiàn)多個(gè)快速轉(zhuǎn)換,如圖 2 所示。

圖 1:同相比較器設(shè)置

圖 2:比較器顫振

這些快速轉(zhuǎn)換有時(shí)會(huì)被誤認(rèn)為是振蕩;然而,該行為實(shí)際上稱為顫振。顫振不代表器件存在缺陷;這是正常行為。從比較器的角度來(lái)看,它看到的是信號(hào)變得高于和低于基準(zhǔn)閾值。即使是基準(zhǔn)附近非常輕微的變化也會(huì)導(dǎo)致輸出進(jìn)入轉(zhuǎn)換狀態(tài)。比較器的響應(yīng)時(shí)間相對(duì)較短,只要信號(hào)變化處于其最大切換頻率以內(nèi),它就會(huì)改變狀態(tài)。

顫振的原因和影響

顫振的主要原因是系統(tǒng)中存在的噪聲,該噪聲的來(lái)源可能有多個(gè),包括輸入、VREF 、電源、元件、原型設(shè)計(jì)板 - 甚至是比較器本身。甚至僅僅是比較器的噪聲就可能引起顫振,此時(shí)輸入端連接在一起以獲得大約 0mV 的內(nèi)部失調(diào)電壓 (VOS) 。無(wú)論噪聲源如何,比較器的輸出都會(huì)出現(xiàn)顫振,因?yàn)檩斎腚妷簳?huì)快速、隨機(jī)、連續(xù)地高于和低于基準(zhǔn)電壓。

如果不對(duì)輸出上的顫振加以抑制,這會(huì)成為一個(gè)嚴(yán)重的問題。不必要的輸出狀態(tài)轉(zhuǎn)換可能會(huì)向 FET 開關(guān)等下游器件提供錯(cuò)誤信息并對(duì)其施加錯(cuò)誤的控制,從而導(dǎo)致不穩(wěn)定的系統(tǒng)行為并可能導(dǎo)致系統(tǒng)無(wú)效。例如,顫振可能會(huì)導(dǎo)致控制 DC/DC 轉(zhuǎn)換器使能引腳的比較器反復(fù)對(duì)系統(tǒng)進(jìn)行上電和斷電。此外,電池電壓或溫度傳感器電壓等緩慢移動(dòng)的信號(hào)更容易受到顫振的影響,因?yàn)樾盘?hào)緩慢地越過基準(zhǔn),從而可能會(huì)因噪聲而導(dǎo)致更多越過基準(zhǔn)的情況。這可能會(huì)意外地激活和停用欠壓或過壓以及溫度保護(hù)電路。

顫振解決方案

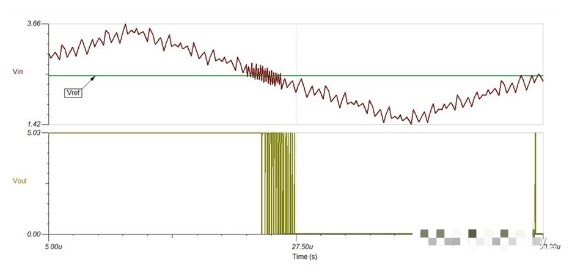

解決顫振的方法主要有兩種,每種方法都有相應(yīng)的子集選項(xiàng)。第一個(gè)選項(xiàng)是通過正反饋實(shí)現(xiàn)外部遲滯。外部遲滯可以有效地增加高于和低于基準(zhǔn)的失調(diào)電壓閾值。圖 3 顯示了具有外部遲滯的同相配置下的比較器及其傳輸特性曲線。

圖 3:具有外部遲滯的同相比較器

另一種消除顫振的方法是使用具有集成或可變遲滯的比較器,例如 TLV7012。集成遲滯還可以提供額外的優(yōu)勢(shì),即通過消除布局中的元件來(lái)節(jié)省空間受限的印刷電路板上的空間。

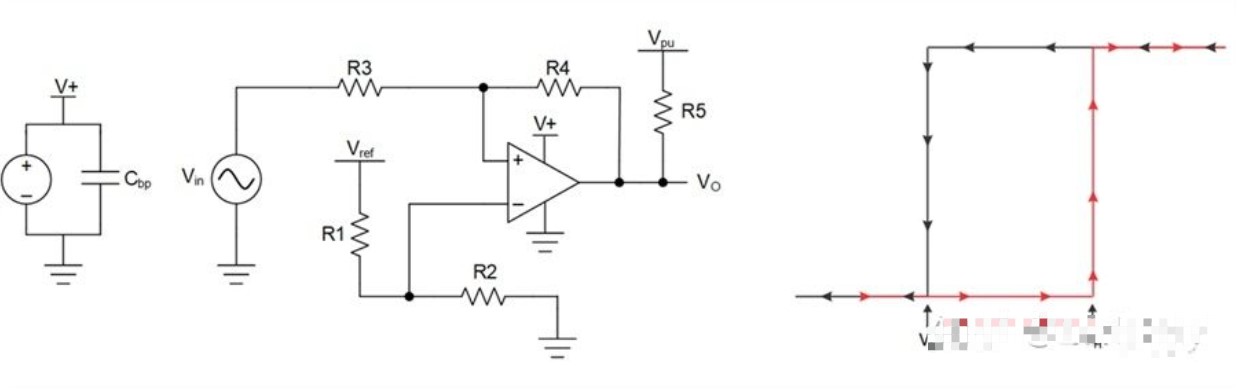

例如,TLV3603 和 TLV3605 具有用于提供可調(diào)內(nèi)部遲滯的引腳。利用 LE/HYS 引腳(參見圖 4)功能,可實(shí)現(xiàn)可變遲滯,具體取決于連接在該引腳和發(fā)射極電源電壓 (VEE) 之間的電阻器值,其中減小電阻會(huì)將遲滯增大至某個(gè)點(diǎn)。如果芯片提供的遲滯不夠大(大于系統(tǒng)中存在的噪聲),仍然可以實(shí)現(xiàn)外部遲滯。

圖 4:VHYST(毫伏)與 RHYST(千歐)之間的關(guān)系

對(duì)于直流精度至關(guān)重要的高速系統(tǒng),應(yīng)使用反饋電容器而非電阻器來(lái)提供短期遲滯,從而在不影響閾值電壓的情況下實(shí)現(xiàn)交流遲滯。

減小顫振可能性的第二個(gè)選項(xiàng)是對(duì)輸入信號(hào)、基準(zhǔn)信號(hào)或兩者進(jìn)行濾波。適當(dāng)?shù)乩@過電源也將有助于盡可能減小大電流尖峰的干擾。對(duì)輸入進(jìn)行濾波的缺點(diǎn)是會(huì)造成信號(hào)延遲,從而可能違反嚴(yán)格的系統(tǒng)時(shí)序要求。不過,對(duì)輸入進(jìn)行濾波可以在不改變狀態(tài)轉(zhuǎn)換的電壓閾值的情況下消除顫振。

下面的圖 5 顯示了一種可能的濾波方案,它與遲滯相結(jié)合,以消除顫振。注意 C1 是如何被劃掉的,因?yàn)樵趯?shí)現(xiàn)正反饋時(shí)向同相節(jié)點(diǎn)施加電容可能會(huì)導(dǎo)致反饋發(fā)生延遲并可能完全將其消除。建議在布局允許的情況下盡可能靠近該引腳放置任何旁路或?yàn)V波電容器,以盡可能提高效率。通過在不同的十倍程范圍內(nèi)使用多個(gè)旁路電容器(例如,1μF、100nF 和 100pf),可以在整個(gè)頻率范圍內(nèi)提供出色的降噪效果。

圖 5:具有外部遲滯和濾波的同相比較器

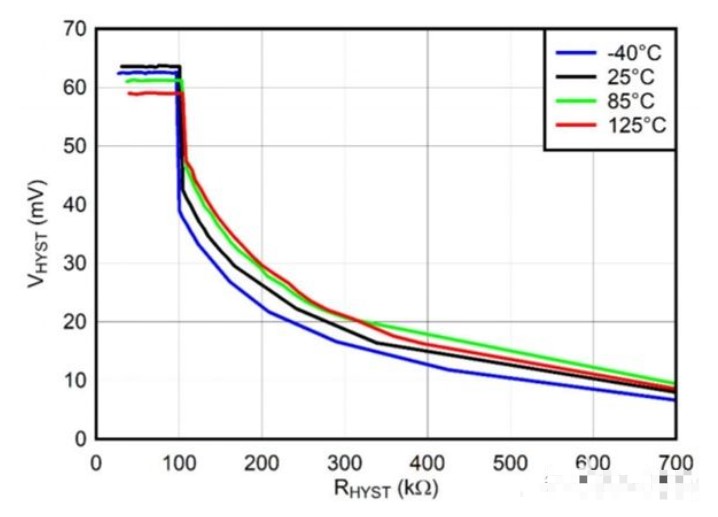

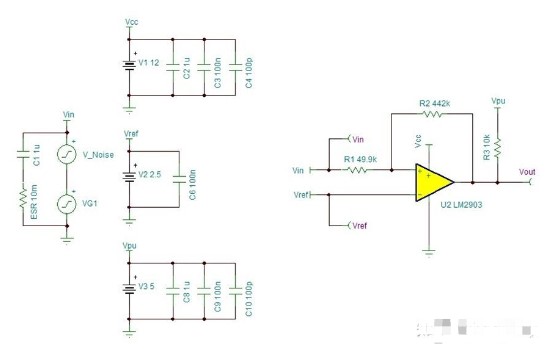

圖 6 和圖 7 顯示了應(yīng)用遲滯、濾波和適當(dāng)旁路后產(chǎn)生的波形以及電路配置。使用“具有遲滯功能的同相比較器電路”中的公式以及選擇的值 R1=100k?、R5=10k?、VHYST=500mV、VO(max)=5V、VO(min)=110mV 和 VREF=2.5,計(jì)算得到的值為 R2=100k?、R3=49.9k? 和 R4=442k?。請(qǐng)注意,所有電阻器值都四舍五入到最接近的 1% 標(biāo)準(zhǔn)電阻器值。

圖 6:已解決比較器顫振

圖 7:具有外部遲滯和濾波設(shè)置的同相比較器

結(jié)語(yǔ)

為了提高抗噪(以及隨之而來(lái)的顫振)能力,可能無(wú)法實(shí)現(xiàn)某些時(shí)序和精度規(guī)格。實(shí)現(xiàn)濾波或遲滯可以提高系統(tǒng)性能,但建議同時(shí)實(shí)施這兩者,以盡可能地減少顫振。找元器件現(xiàn)貨上唯樣商城請(qǐng)記住,實(shí)現(xiàn)遲滯會(huì)改變閾值電壓,因此應(yīng)適當(dāng)?shù)剡x擇它們以反映系統(tǒng)的要求。還要注意濾波如何影響系統(tǒng)的時(shí)序限制。

抗噪是每個(gè)系統(tǒng)的一個(gè)重要方面,有助于盡可能地降低比較器干擾并減少不必要的行為。在下一部分中,我們將討論輸入共模電壓范圍。

審核編輯:劉清

-

比較器

+關(guān)注

關(guān)注

14文章

1636瀏覽量

107103

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

什么是顫振?解決比較器顫振的方法有哪幾種

TLE7242G顫振疊加不進(jìn)去,設(shè)置寄存器沒有反應(yīng)

大跨度橋梁非線性顫振和抖振時(shí)程分析

基于嵌入式系統(tǒng)的切削顫振在線監(jiān)測(cè)技術(shù)研究

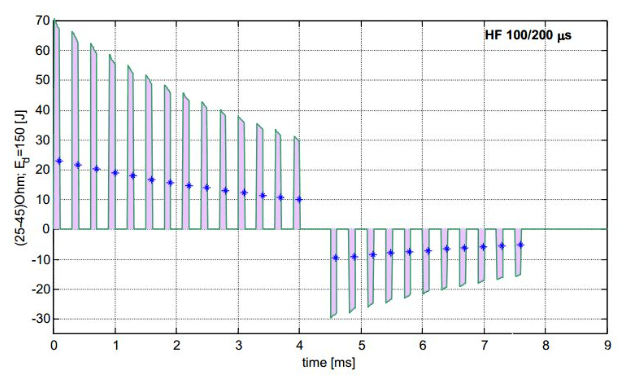

心臟除顫器的原理

飛行試驗(yàn)顫振數(shù)據(jù)實(shí)時(shí)監(jiān)控系統(tǒng)

基于反演滑模的二元機(jī)翼顫振控制

振幅對(duì)顫振球磨機(jī)粉磨效率的影響研究

科普|除顫器類型及如何測(cè)試除顫儀

解決比較器的主要挑戰(zhàn):顫振

解決比較器的主要挑戰(zhàn):顫振

評(píng)論