解決比較器的主要挑戰:顫振

比較器是幾乎在每個應用中都可以找到的基本模擬元件。描述比較器的一種方式是它們是 1 位 ADC:比較器有兩個輸入端,其中一個通常用作電壓基準,另一個用作輸入電壓信號。根據哪個輸入端是基準以及輸入電壓是多少,比較器輸出將切換為高電平或低電平。這些元件用途廣泛,特別是在混合信號和控制應用中,例如過壓和欠壓檢測以及溫度傳感。

雖然比較器的概念很簡單,但在實現過程中會有幾個常見的設計挑戰。為了應對這些挑戰,本文將介紹設計人員為實現出色的比較器性能而必須應對的三個最常見設計注意事項 - 從顫振開始。

什么是顫振?

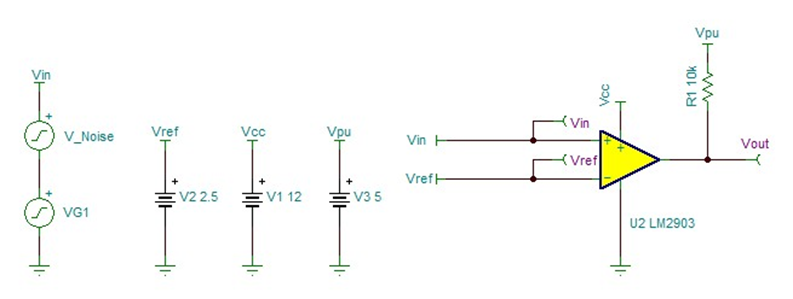

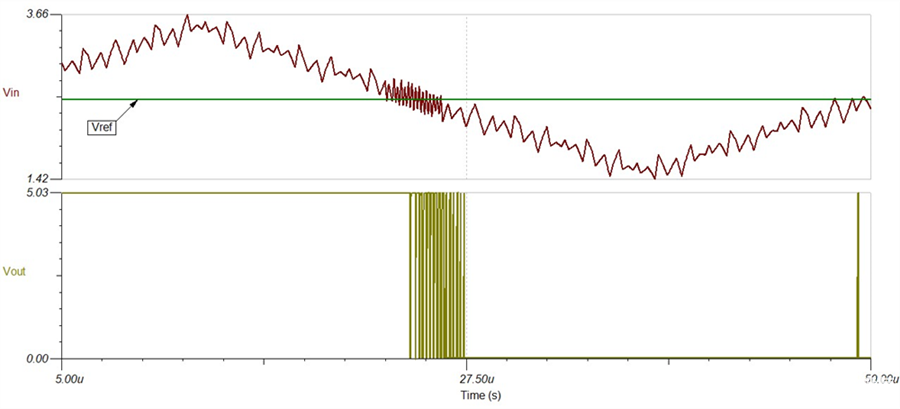

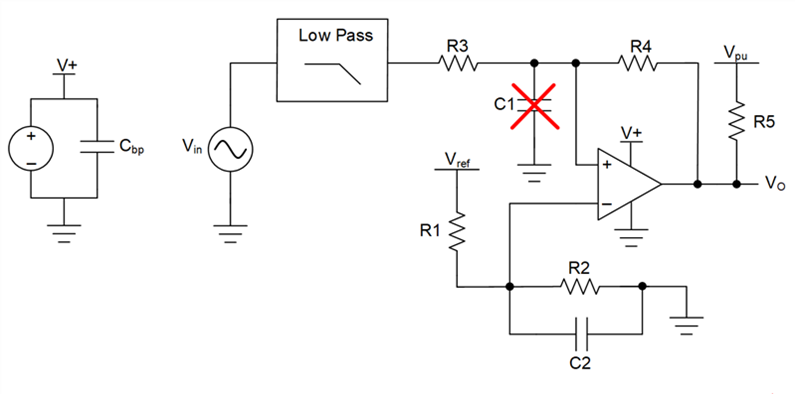

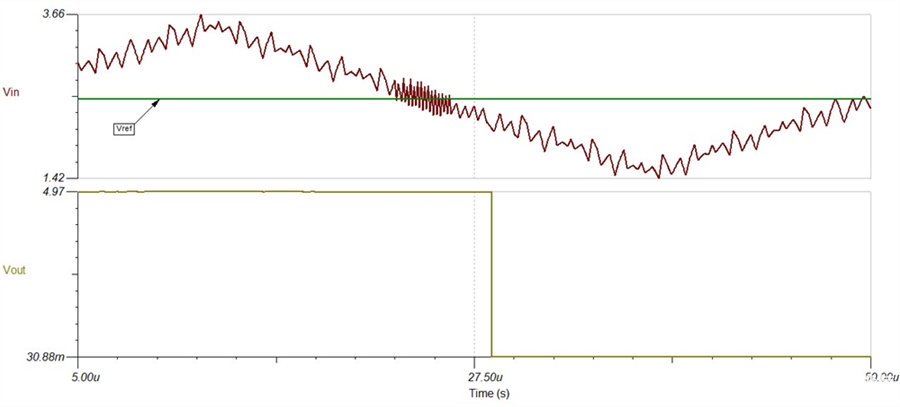

為了演示顫振現象,將 LM2903 雙路差分比較器設置為同相配置(圖 1),將噪聲添加到以基準電壓 (VREF) 為中心的 1V 峰峰值三角波中。當輸入電壓 (VIN) 接近 IN– 上的基準電壓時,會出現多個快速轉換,如圖 2 所示。

圖 1:同相比較器設置

圖 2:比較器顫振

這些快速轉換有時會被誤認為是振蕩;然而,該行為實際上稱為顫振。顫振不代表器件存在缺陷;這是正常行為。從比較器的角度來看,它看到的是信號變得高于和低于基準閾值。即使是基準附近非常輕微的變化也會導致輸出進入轉換狀態。比較器的響應時間相對較短,只要信號變化處于其最大切換頻率以內,它就會改變狀態。

顫振的原因和影響

顫振的主要原因是系統中存在的噪聲,該噪聲的來源可能有多個,包括輸入、VREF 、電源、元件、原型設計板 - 甚至是比較器本身。甚至僅僅是比較器的噪聲就可能引起顫振,此時輸入端連接在一起以獲得大約 0mV 的內部失調電壓 (VOS) 。無論噪聲源如何,比較器的輸出都會出現顫振,因為輸入電壓會快速、隨機、連續地高于和低于基準電壓。

如果不對輸出上的顫振加以抑制,這會成為一個嚴重的問題。不必要的輸出狀態轉換可能會向 FET 開關等下游器件提供錯誤信息并對其施加錯誤的控制,從而導致不穩定的系統行為并可能導致系統無效。例如,顫振可能會導致控制 DC/DC 轉換器使能引腳的比較器反復對系統進行上電和斷電。此外,電池電壓或溫度傳感器電壓等緩慢移動的信號更容易受到顫振的影響,因為信號緩慢地越過基準,從而可能會因噪聲而導致更多越過基準的情況。這可能會意外地激活和停用欠壓或過壓以及溫度保護電路。

顫振解決方案

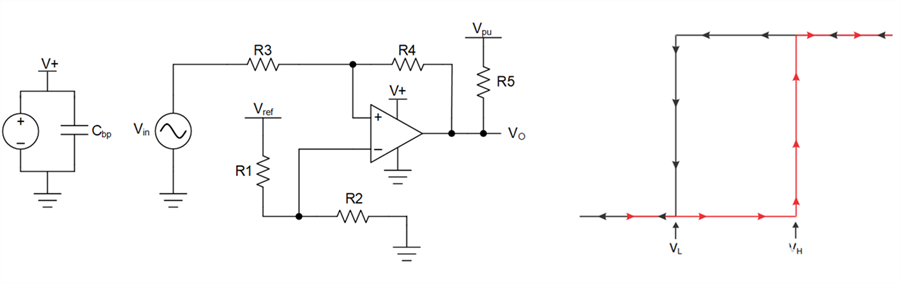

解決顫振的方法主要有兩種,每種方法都有相應的子集選項。第一個選項是通過正反饋實現外部遲滯。外部遲滯可以有效地增加高于和低于基準的失調電壓閾值。圖 3 顯示了具有外部遲滯的同相配置下的比較器及其傳輸特性曲線。

圖 3:具有外部遲滯的同相比較器

另一種消除顫振的方法是使用具有集成或可變遲滯的比較器,例如 TLV7012。集成遲滯還可以提供額外的優勢,即通過消除布局中的元件來節省空間受限的印刷電路板上的空間。

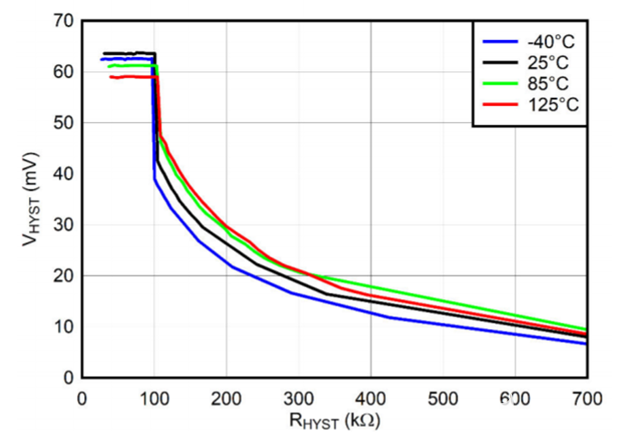

例如,TLV3603 和 TLV3605 具有用于提供可調內部遲滯的引腳。利用 LE/HYS 引腳(參見圖 4)功能,可實現可變遲滯,具體取決于連接在該引腳和發射極電源電壓 (VEE) 之間的電阻器值,其中減小電阻會將遲滯增大至某個點。如果芯片提供的遲滯不夠大(大于系統中存在的噪聲),仍然可以實現外部遲滯。

圖 4:VHYST(毫伏)與 RHYST(千歐)之間的關系

對于直流精度至關重要的高速系統,應使用反饋電容器而非電阻器來提供短期遲滯,從而在不影響閾值電壓的情況下實現交流遲滯。

減小顫振可能性的第二個選項是對輸入信號、基準信號或兩者進行濾波。適當地繞過電源也將有助于盡可能減小大電流尖峰的干擾。對輸入進行濾波的缺點是會造成信號延遲,從而可能違反嚴格的系統時序要求。不過,對輸入進行濾波可以在不改變狀態轉換的電壓閾值的情況下消除顫振。 買電子元器件現貨上唯樣商城

下面的圖 5 顯示了一種可能的濾波方案,它與遲滯相結合,以消除顫振。注意 C1 是如何被劃掉的,因為在實現正反饋時向同相節點施加電容可能會導致反饋發生延遲并可能完全將其消除。建議在布局允許的情況下盡可能靠近該引腳放置任何旁路或濾波電容器,以盡可能提高效率。通過在不同的十倍程范圍內使用多個旁路電容器(例如,1μF、100nF 和 100pf),可以在整個頻率范圍內提供出色的降噪效果。

圖 5:具有外部遲滯和濾波的同相比較器

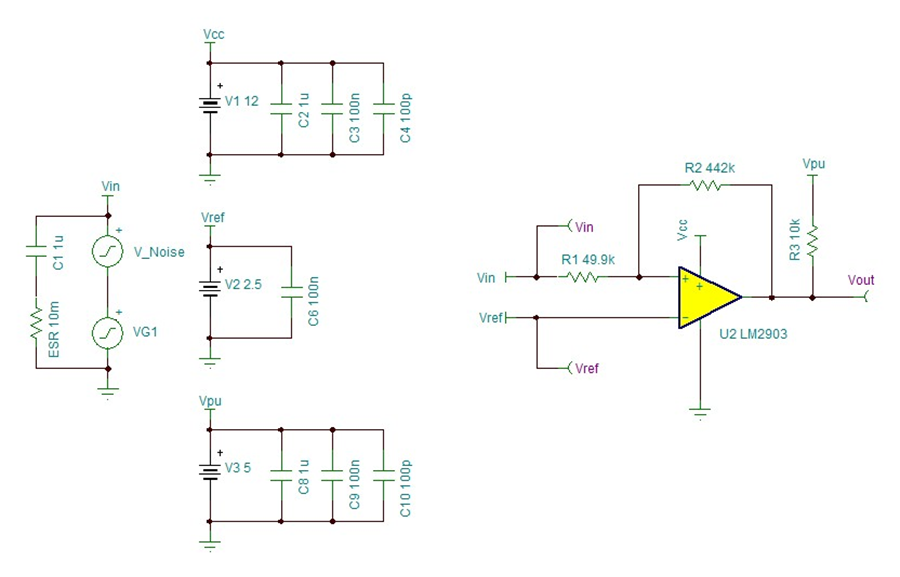

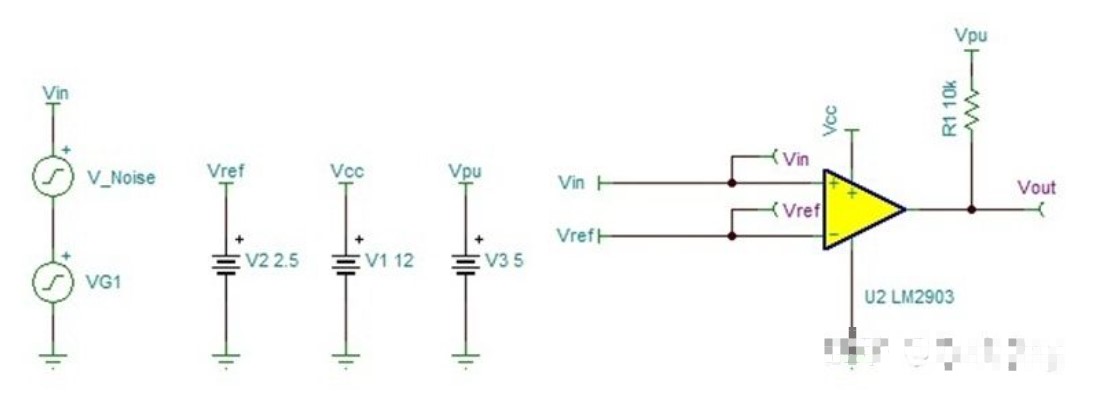

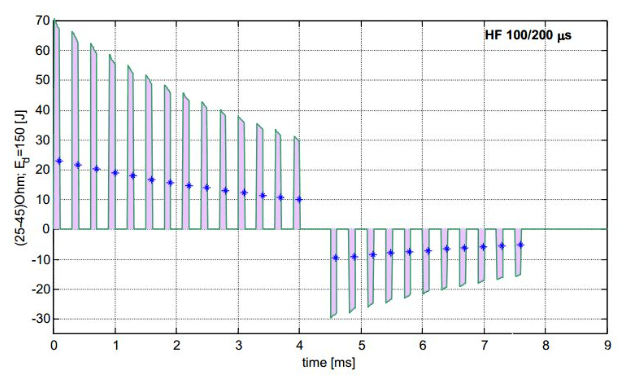

圖 6 和圖 7 顯示了應用遲滯、濾波和適當旁路后產生的波形以及電路配置。使用“具有遲滯功能的同相比較器電路”中的公式以及選擇的值 R1=100k?、R5=10k?、VHYST=500mV、VO(max)=5V、VO(min)=110mV 和 VREF=2.5,計算得到的值為 R2=100k?、R3=49.9k? 和 R4=442k?。請注意,所有電阻器值都四舍五入到最接近的 1% 標準電阻器值。

圖 6:已解決比較器顫振

圖 7:具有外部遲滯和濾波設置的同相比較器

結語

為了提高抗噪(以及隨之而來的顫振)能力,可能無法實現某些時序和精度規格。實現濾波或遲滯可以提高系統性能,但建議同時實施這兩者,以盡可能地減少顫振。請記住,實現遲滯會改變閾值電壓,因此應適當地選擇它們以反映系統的要求。還要注意濾波如何影響系統的時序限制。

抗噪是每個系統的一個重要方面,有助于盡可能地降低比較器干擾并減少不必要的行為。在下一部分中,我們將討論輸入共模電壓范圍。

審核編輯 黃昊宇

-

比較器

+關注

關注

14文章

1636瀏覽量

107103 -

顫振數據

+關注

關注

0文章

2瀏覽量

5628

發布評論請先 登錄

相關推薦

TLE7242G顫振疊加不進去,設置寄存器沒有反應

大跨度橋梁非線性顫振和抖振時程分析

基于嵌入式系統的切削顫振在線監測技術研究

飛行試驗顫振數據實時監控系統

基于反演滑模的二元機翼顫振控制

振幅對顫振球磨機粉磨效率的影響研究

解決比較器的主要挑戰:顫振

解決比較器的主要挑戰:顫振

評論