HDLBits: 在線學習 SystemVerilog(九)-Problem 36-42

HDLBits 是一組小型電路設計習題集,使用 Verilog/SystemVerilog 硬件描述語言 (HDL) 練習數字硬件設計~

縮略詞索引:

SV:SystemVerilog

今天的幾道題主要是補充SV的一些補充語法練習。

Problem 36-Conditional

這道題主要是考察條件(三元)運算符的用法,具體詳見《SystemVerilog-條件(三元)運算符》!

題目說明

給定四個無符號數,請找出最小值。無符號數可以與標準比較運算符(a < b)進行比較。使用條件運算符描述一個兩路的最小值電路,然后組合它來創建一個4路最小電路。可能需要一些線向量作為中間結果。

模塊端口聲明

moduletop_module( input[7:0]a,b,c,d, output[7:0]min);

題目解析

這個題目重點是靈活使用三元運算符,因為這個語法比較簡單,所以大家注意一下使用方式即可~

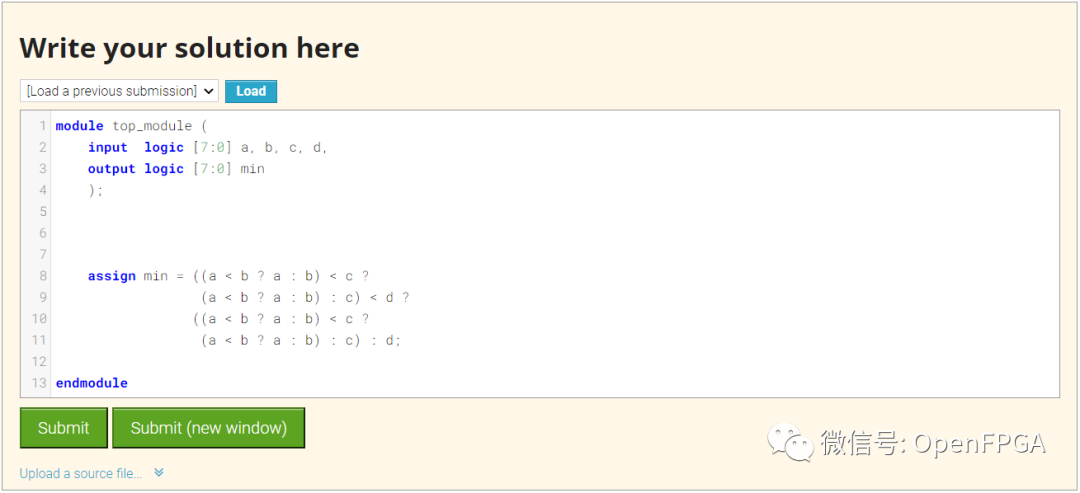

moduletop_module( inputlogic[7:0]a,b,c,d, outputlogic[7:0]min ); assignmin=((a

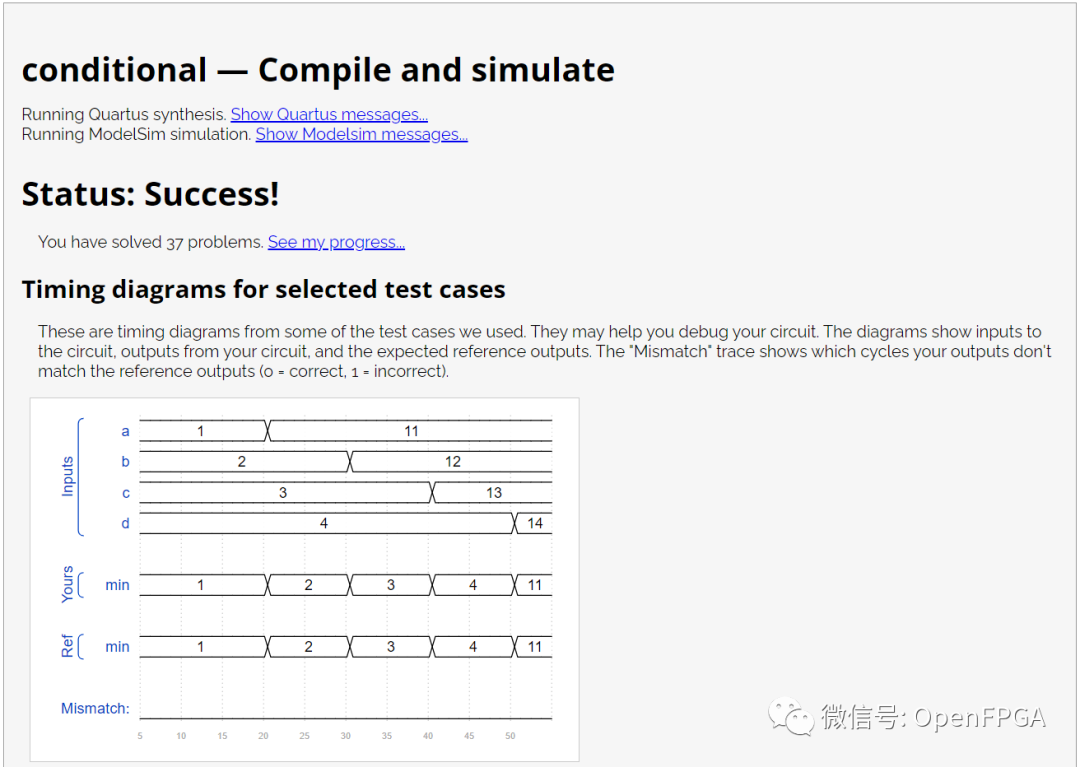

點擊Submit,等待一會就能看到下圖結果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網站會對比這兩個波形,一旦這兩者不匹配,仿真結果會變紅。

這一題就結束了。

Problem 37-Reduction

這題是考察歸約運算符,本來想在SV系列文章里寫的,這次作為一個專題在下面一篇文章中。

題目說明

當通過不完善的通道傳輸數據時,奇偶校驗通常用作檢測錯誤的簡單方法。創建一個電路,計算 8 位字節的奇偶校驗位(將向該字節添加第9位)。 我們將使用偶校驗,其中奇偶校驗位只是所有8個數據位的XOR。

模塊端口聲明

moduletop_module( input[7:0]in, outputparity);

題目解析

這道題難度不大核心代碼只有一行。

簡單解答

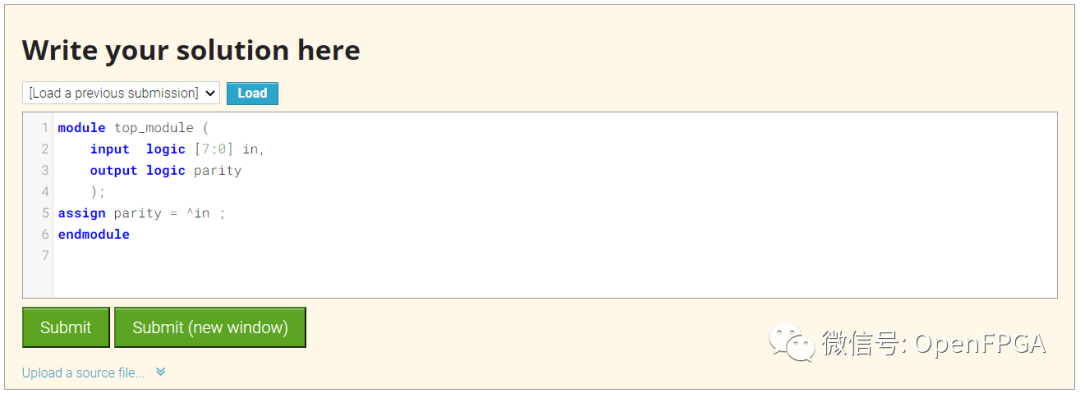

moduletop_module( inputlogic[7:0]in, outputlogicparity ); assignparity=^in; endmodule

點擊Submit,等待一會就能看到下圖結果:

注意圖中的無波形。

這一題就結束了。

Problem 38-Gates100

題目說明

構建具有100個輸入的組合電路。

電路一共有3個輸出:

模塊端口聲明

moduletop_module( input[99:0]in, outputout_and, outputout_or, outputout_xor );

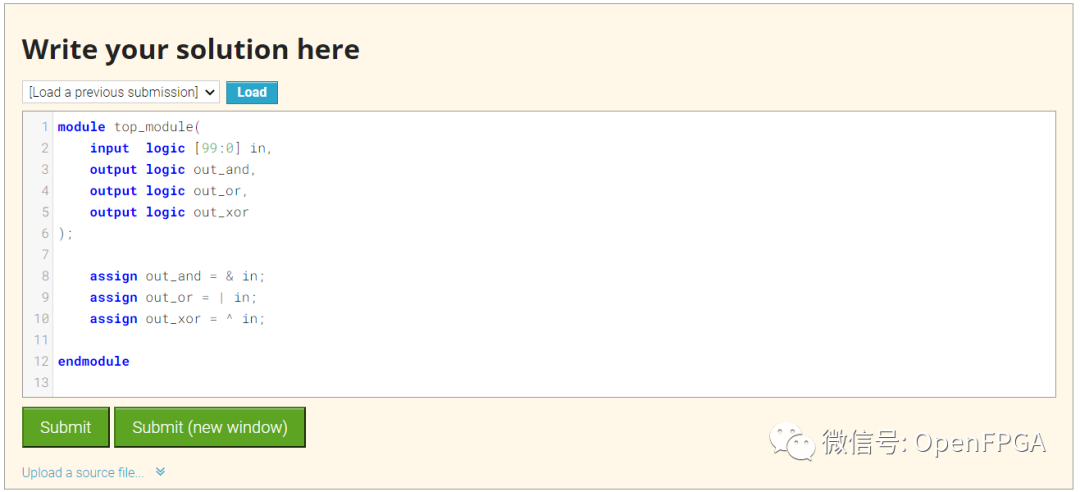

題目解析

上一個問題已經說過歸約運算符了,這道題肯定也是類似解答思路,應該很簡單吧~~~

moduletop_module( inputlogic[99:0]in, outputlogicout_and, outputlogicout_or, outputlogicout_xor ); assignout_and=∈ assignout_or=|in; assignout_xor=^in; endmodule

點擊Submit,等待一會就能看到下圖結果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網站會對比這兩個波形,一旦這兩者不匹配,仿真結果會變紅。

這一題就結束了。

Problem 39-Vector100r

題目說明

給了一個長度是100的向量,請把它翻轉輸出一下。

提示:for循環(組合always塊或者generate塊)在這里很有用。 這道題中,因為不需要模塊實例化(必須使用generate塊),建議使用always塊。

模塊端口聲明

moduletop_module( input[99:0]in, output[99:0]out );

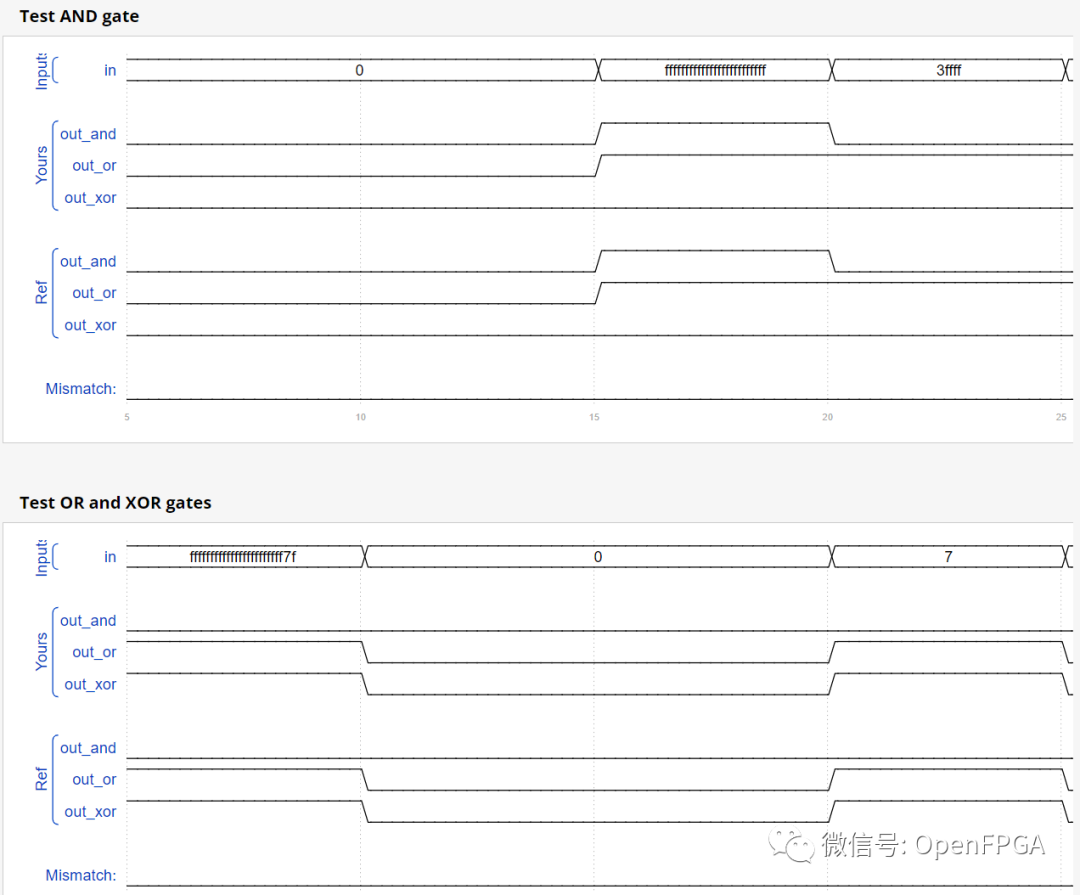

題目解析

提示中已經暗示了使用for循環,所以我們就按照always...for...使用即可。

moduletop_module( inputlogic[99:0]in, outputlogic[99:0]out ); varintegeri; always_combbegin for(i=0;i<=?99;?i?=?i?+?1)begin ????????????out[i]?=?in[99?-?i]; ????????end ????end endmodule

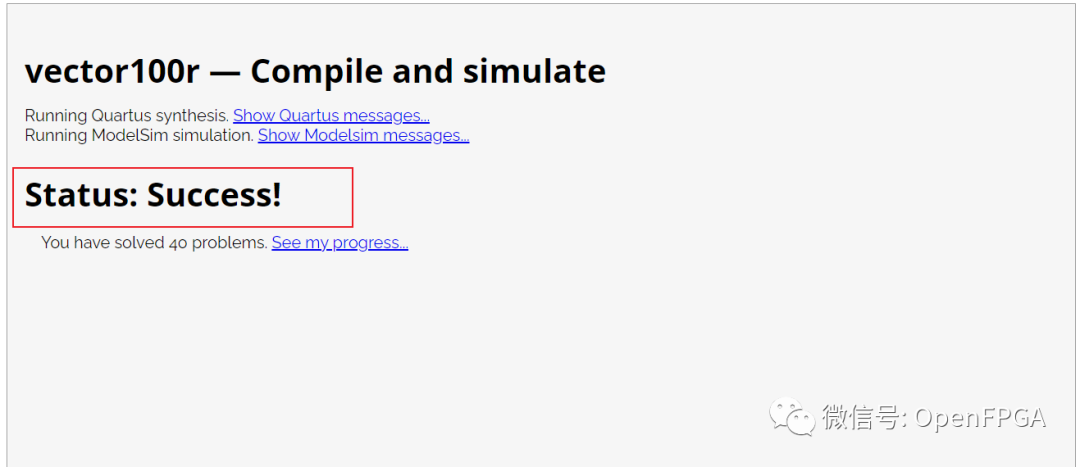

點擊Submit,等待一會就能看到下圖結果:

注意圖中無波形。

這一題就結束了。

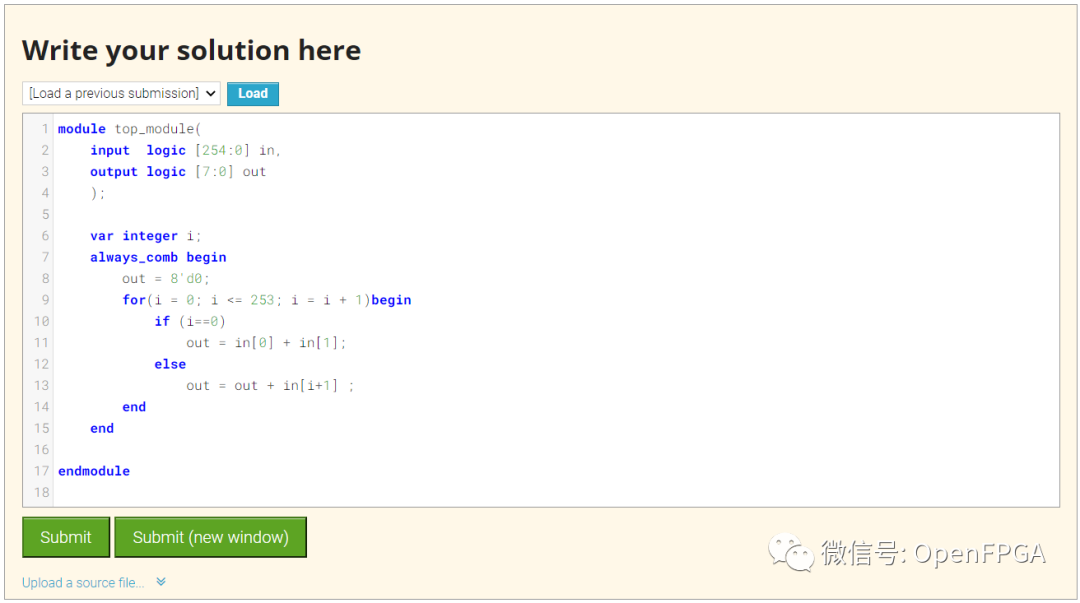

Problem 40-Popcount255

題目說明

老生常談的題目了,設計電路來計算輸入矢量中‘1’的個數,題目要求建立一個255bit輸入的矢量來判斷輸入中‘1’的個數。

提示:重復工作量建議使用for~

模塊端口聲明

moduletop_module( input[254:0]in, output[7:0]out);

題目解析

這個題目的爭論點在怎么減少邏輯量,目前沒什么好思路,但是可以增加運行速度,那就是分類冶制。

moduletop_module( input[254:0]in, outputreg[7:0]out ); always@(*)begin//Combinationalalwaysblock out=0; for(inti=0;i<255;i++) ???out?=?out?+?in[i]; ?end ? endmodule

點擊Submit,等待一會就能看到下圖結果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網站會對比這兩個波形,一旦這兩者不匹配,仿真結果會變紅。

這一題就結束了。

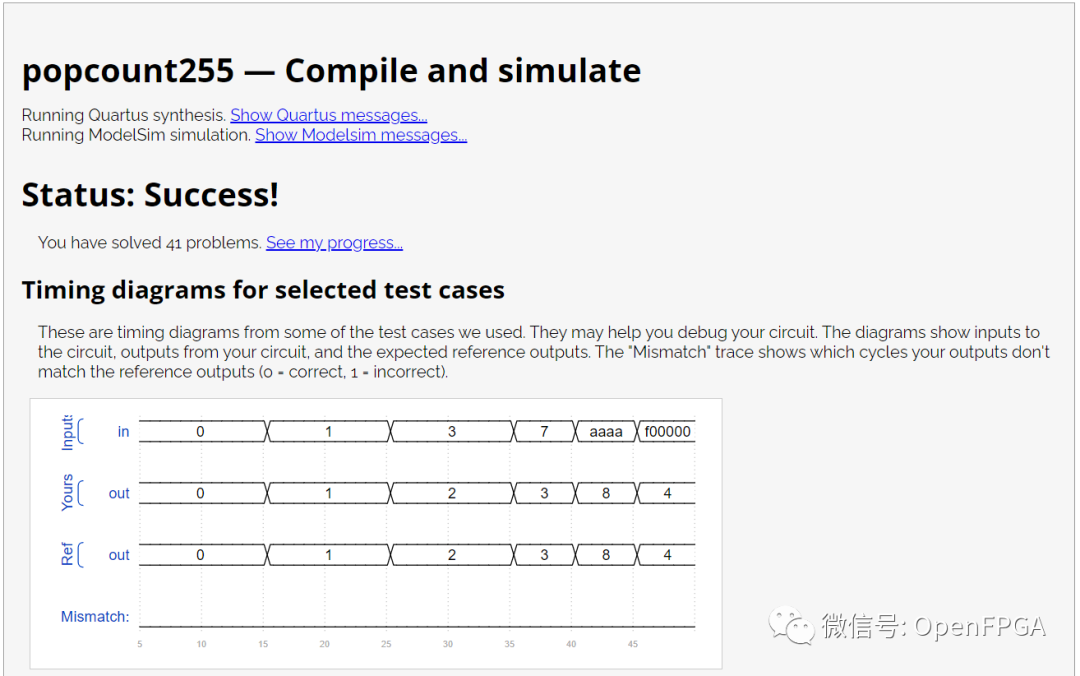

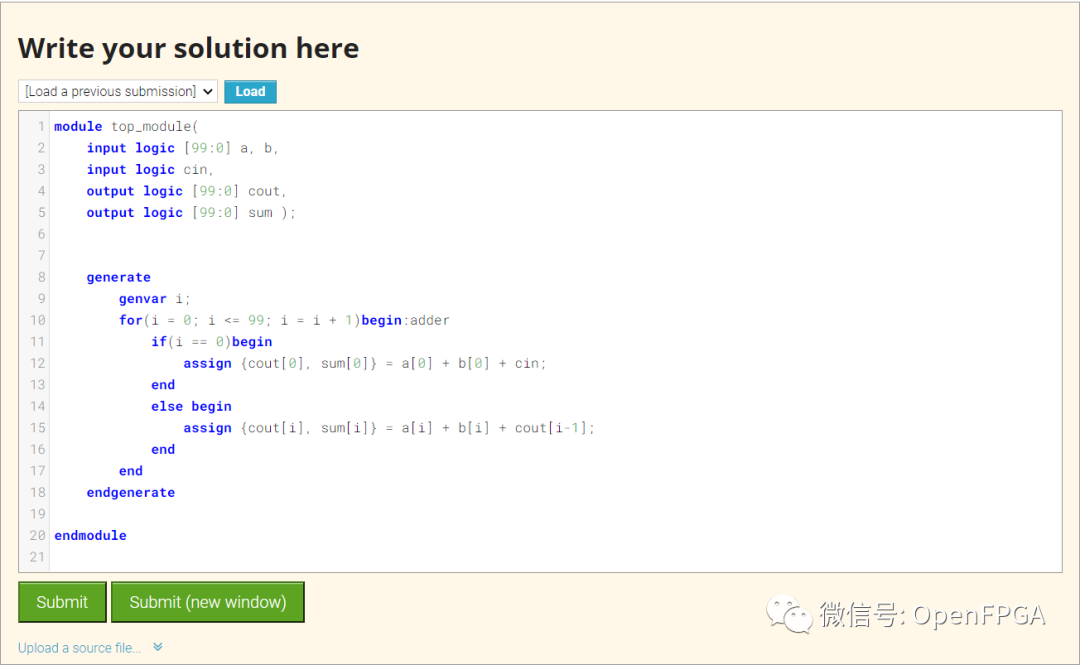

Problem 41-Adder100i

題目說明

通過實例化 100 個全加器來創建一個 100 位二進制波紋進位加法器。加法器將兩個 100 位數字和一個進位相加,輸出為sum與cout,還要輸出紋波進位加法器中每個全加器的進位。cout[99] 是最后一個全加器的最終進位,也是通常看到的進位。

模塊端口聲明

moduletop_module( input[99:0]a,b, inputcin, output[99:0]cout, output[99:0]sum);

題目解析

這個題目簡單的用法就是generate...for,最近在整理這方面知識,在這篇文章發出來之前應該已經發布,詳見《【Verilog我思我用】-generate》。

moduletop_module( inputlogic[99:0]a,b, inputlogiccin, outputlogic[99:0]cout, outputlogic[99:0]sum); generate genvari; for(i=0;i<=?99;?i?=?i?+?1)begin:adder ?????????if(i?==?0)begin ?????????????assign?{cout[0],?sum[0]}?=?a[0]?+?b[0]?+?cin; ????????????end ????????????else?begin ?????????????assign?{cout[i],?sum[i]}?=?a[i]?+?b[i]?+?cout[i-1]; ????????????end????????? ????????end ????endgenerate endmodule

點擊Submit,等待一會就能看到下圖結果:

注意圖中是無波形的。

這一題就結束了。

Problem 42-Bcdadd100

題目說明

本題已經提供了一個名為bcd_fadd的BCD一位全加器,他會添加兩個BCD數字和一個cin,并產生一個cout和sum。

modulebcd_fadd{ input[3:0]a, input[3:0]b, inputcin, outputcout, output[3:0]sum);

我們需要實例化100個bcd_fadd來實現100位的BCD進位加法器。該加法器應包含兩個100bit的BCD碼和一個cin, 輸出產生sum 和 cout。

模塊端口聲明

moduletop_module( input[399:0]a,b, inputcin, outputcout, output[399:0]sum);

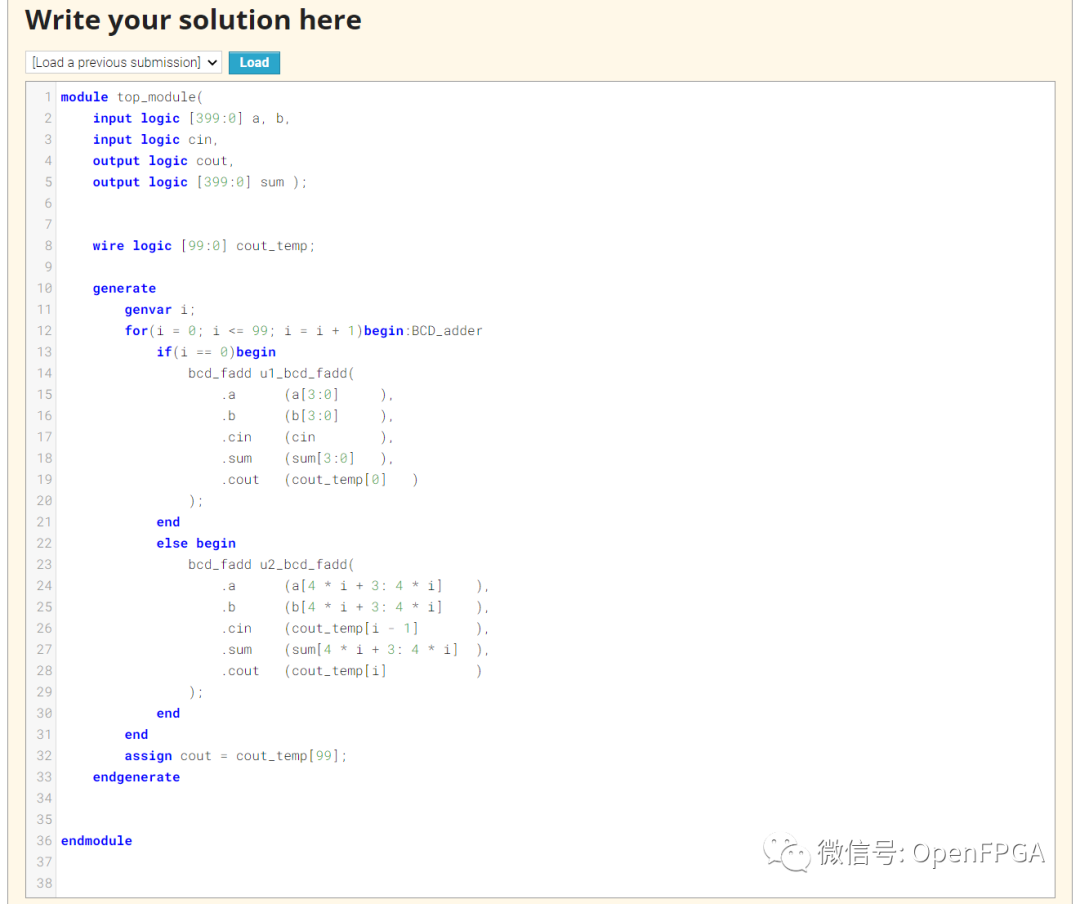

題目解析

這個題目也是在鞏固generate用法,建議自己完成并思考。

moduletop_module( inputlogic[399:0]a,b, inputlogiccin, outputlogiccout, outputlogic[399:0]sum); wirelogic[99:0]cout_temp; generate genvari; for(i=0;i<=?99;?i?=?i?+?1)begin:BCD_adder ????????????if(i?==?0)begin ????????????????bcd_fadd?u1_bcd_fadd( ????????????????????.a??(a[3:0]??), ????????????????????.b??(b[3:0]??), ????????????????????.cin?(cin??), ????????????????????.sum?(sum[3:0]?), ????????????????????.cout?(cout_temp[0]?) ????????????????); ????????????end ????????????else?begin ????????????????bcd_fadd?u2_bcd_fadd( ????????????????????.a??(a[4?*?i?+?3:?4?*?i]?), ????????????????????.b??(b[4?*?i?+?3:?4?*?i]?), ????????????????????.cin?(cout_temp[i?-?1]???????), ????????????????????.sum?(sum[4?*?i?+?3:?4?*?i]??), ????????????????????.cout?(cout_temp[i]???????????) ????????????????); ????????????end ????????end ????????assign?cout?=?cout_temp[99]; ????endgenerate ???????????????????? endmodule

點擊Submit,等待一會就能看到下圖結果:

注意圖中的無波形。

這一題就結束了。

總結

今天的幾道題就結束了,整體屬于加強練習的過程,適合獨立完成,加強理解。

審核編輯:彭靜

-

電路設計

+關注

關注

6665文章

2427瀏覽量

203306 -

硬件

+關注

關注

11文章

3252瀏覽量

66113 -

運算符

+關注

關注

0文章

172瀏覽量

11064

原文標題:HDLBits: 在線學習 SystemVerilog(九)-Problem 36-42

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

C運算符的優先級和結合性詳細解決

淺析MySQL中的各類運算符

如何靈活使用三元運算符

如何靈活使用三元運算符

評論