FPGA項目開發(fā)之 7 系列 FPGA IDELAY2 / ODELAY2

IO 靈活性是FPGA 最大的優(yōu)點之一。如果我們設(shè)計的 PCB 信號走線不完美,IO的靈活性使我們能夠?qū)R進入設(shè)備的高速數(shù)據(jù),幫助我們擺脫困境。

設(shè)備 IO 結(jié)構(gòu)中一個經(jīng)常被忽視的功能是 IDELAY2 和 ODELAY2 原語。這些原語為開發(fā)人員提供了一個由 32 個抽頭組成的可編程延遲線,可提供可調(diào)節(jié)或固定的延遲。

實際可用的原語取決于我們正在使用的 IO bank 的類型。High Performance IO (HP IO) 為用戶提供 IDELAY2 和 ODELAY2 原語,而 High-Range IO (HR IO) 僅提供 IDELAY2 原語。

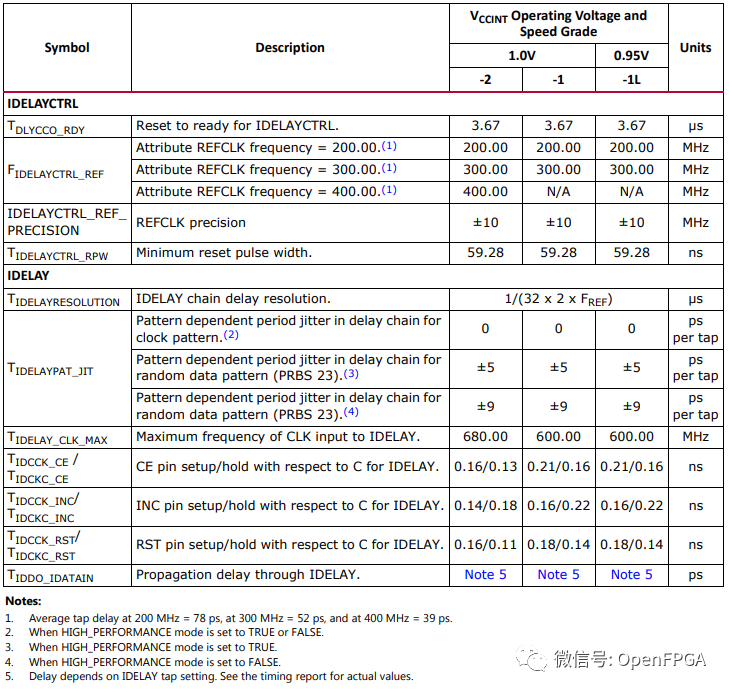

我們可以同時使用 IDELAY 和 ODELAY 來消除信號之間的小延遲。抽頭之間的分辨率取決于FPGA的時鐘頻率和速度等級,7 系列 AC/DC 數(shù)據(jù)表如下所示:

當我們提供 200 MHz 參考時鐘時,每個抽頭增量都會將延遲增加 78 ps。這意味著總延遲約為 2.469 ns。

IDELAY 和 ODELAY 原語可以在四種模式下運行:

FIXED——延遲在此模式下是固定的,不能在運行時更改。

VARIABLE – 這是一個可變延遲,其中抽頭值可以使用簡單的界面增加或減少。

VAR_LOAD – 與變量模式類似,可以通過輸入向量設(shè)置抽頭延遲。

VAR_LOAD_PIPE – 這與 VAR_LOAD 類似,但是可以流水線化未來的延遲。

IDELAY2 模塊能夠延遲來自邏輯結(jié)構(gòu)或 IO 輸入的信號。

現(xiàn)在讓我們看下如何在應用程序中實現(xiàn) IDELAY 功能,并創(chuàng)建一個不同模式下的實例。

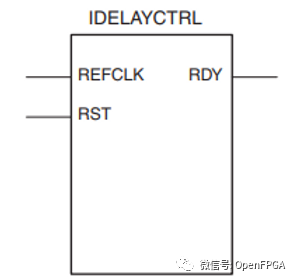

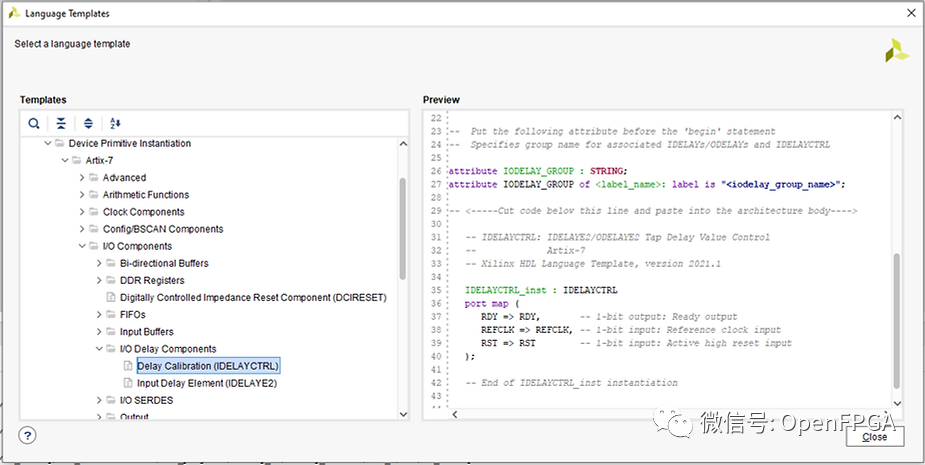

要開始使用 IDELY 或 ODELAY,我們需要實現(xiàn)一個 IDELAYCNTRL 模塊。該模塊不斷校準其區(qū)域內(nèi)的各個延遲抽頭。該模塊非常簡單,需要參考時鐘和復位,RDY 輸出低時表示 IDELAYCNTRL 模塊需要復位。

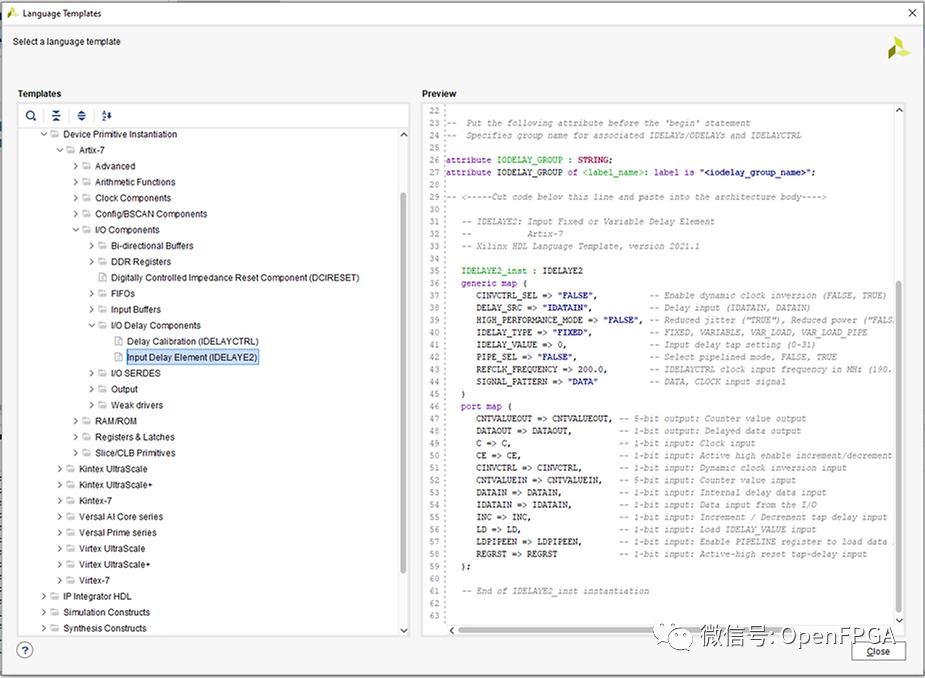

這些可以使用 Vivado 文本編輯器中提供的語言模板來實例化我們需要的模塊。

我們也可以使用相同的語言模板來實例化 IDELAYCNTRL2。我們將要演示的設(shè)計將使用一個 IDELAYCNTRL 和兩個 IDELAY2 原語。這就能測試不同配置 IDELAY2 時信號延遲之間的差異。

兩個 IDELAY2 原語都將以 VAR_LOAD 模式運行。允許使用 CNTVALUEIN 和簡單的 CE 和 INC 信號接口調(diào)整抽頭延遲。

測試平臺將執(zhí)行以下步驟:

重置 IDELAYCNTRL。

將兩個輸入信號 IDELAY2 設(shè)置為 0 延遲。

設(shè)置兩個 IDELAY 延遲 2,將兩個信號。

將第二個 IDELAY2 延遲增加 1 ,同時將第一個 IDELAY 保留為 2。

將第二個 IDELAY2 減 1 ,讓兩者具有相同的延遲。

將第二個 IDELAY2 設(shè)置為具有 31 的最大可能延遲。

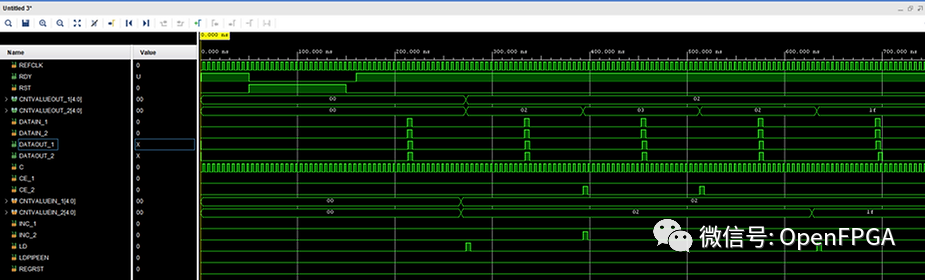

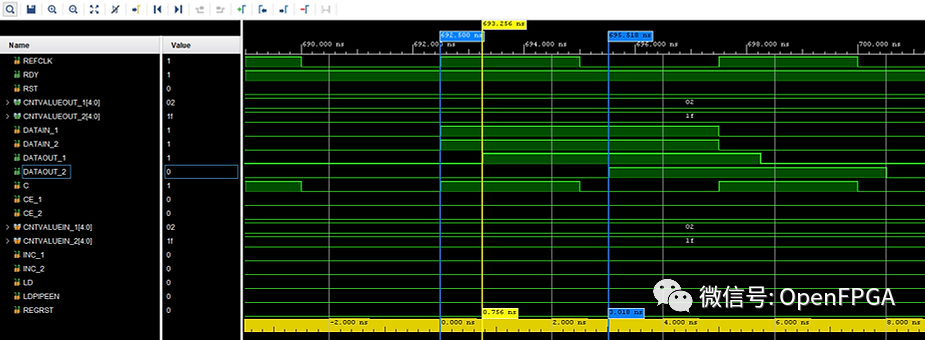

可以在下面看到整體仿真延遲比較小,無法看到該級別延遲的影響。然而,隨著仿真執(zhí)行不同的測試,我們將看到控制信號和抽頭值發(fā)生變化。

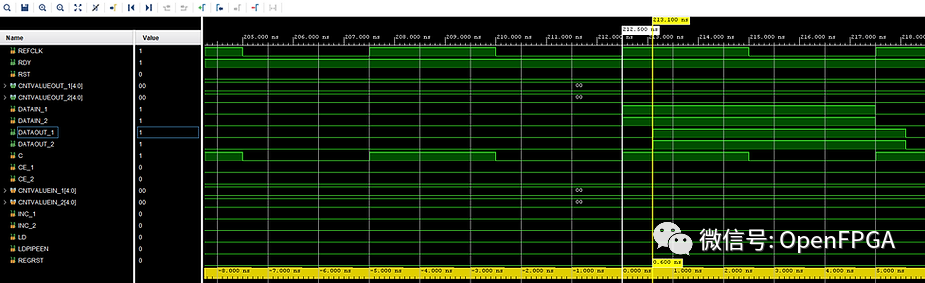

測試一的波形如下所示。盡管沒有計算延遲,但輸入信號和輸出信號之間存在大約 60 ps 的延遲。

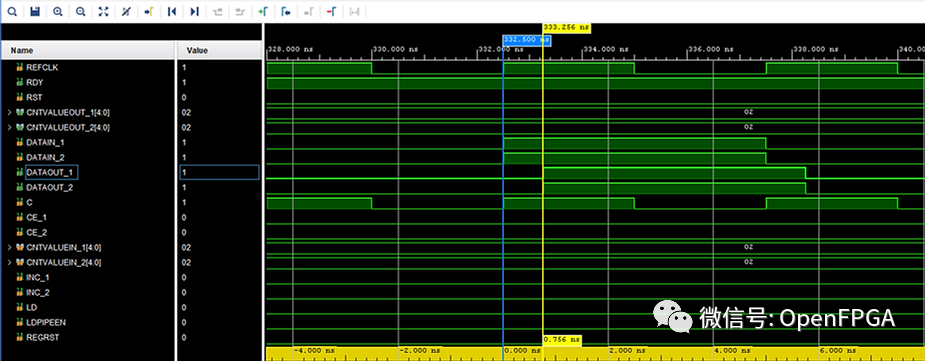

當延遲設(shè)置為 2 時,延遲為 756 ns,即 156 ps(兩個 78 ps 的抽頭延遲)加上原來的 0.6 ns 延遲。

第三個測試顯示信號一和信號二之間有 78 ps 的延遲。對應于接頭設(shè)置的差異,這也顯示在計數(shù)值輸出信號上。

第四個測試將兩個信號路徑設(shè)置為具有相同的延遲。測試三和四演示了簡單的遞增和遞減接口是如何工作的。我們啟用 IDELAY2,并根據(jù) INC 的狀態(tài),增加或減少抽頭延遲。如果 INC 設(shè)置為與 CE 一致,則增加抽頭延遲,否則減少抽頭延遲。

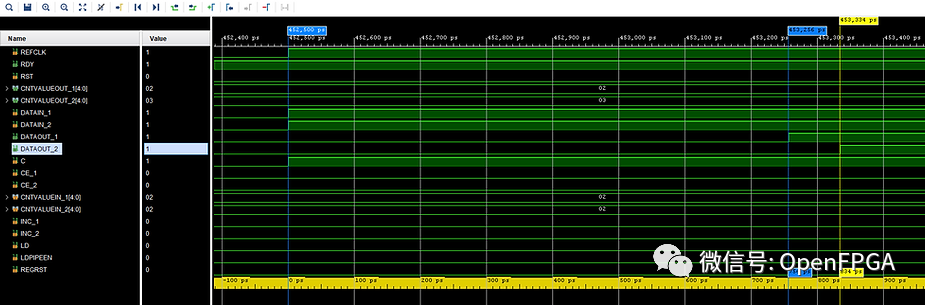

最后的測試將第二個信號路徑設(shè)置為最大延遲。在這里可以看到信號 2 延遲了 3.018 ns。這是2.469 ns 的抽頭延遲加上原來的 0.6 ns。

IDELAY 在我們的工具箱中是一個非常有用的工具,它提供了對 FPGA 中的輸入信號進行細粒度對齊的能力。

-

FPGA

+關(guān)注

關(guān)注

1626文章

21671瀏覽量

601886 -

pcb

+關(guān)注

關(guān)注

4317文章

23010瀏覽量

396344 -

仿真

+關(guān)注

關(guān)注

50文章

4044瀏覽量

133422 -

應用程序

+關(guān)注

關(guān)注

37文章

3243瀏覽量

57603

原文標題:FPGA項目開發(fā)之 7 系列 FPGA IDELAY2 / ODELAY2

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

xilinx FPGA中oddr,idelay的用法詳解

如何在應用程序中實現(xiàn) IDELAY 功能

如何在ModusToolbox?中檢查和設(shè)置應用程序的內(nèi)存地址?

嵌入式應用程序中的USB 3.0鏈路共享怎么實現(xiàn)?

如何在應用程序“CyMeCube”中查看端點?

CH32F103如何在應用程序中響應中斷?

如何在應用程序中實現(xiàn)IDELAY功能并創(chuàng)建一個不同模式下的實例

FPGA高級SelectIO邏輯資源簡析

如何在linux應用程序中使用pwm捕獲?

用Delphi實現(xiàn)基于SAPI的電腦語音控制應用程序

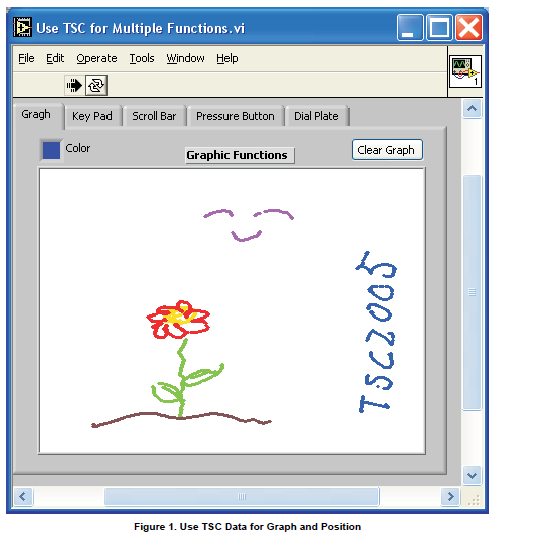

如何在軟件中實現(xiàn)TI的觸摸屏控制器提供的各種功能詳細概述

如何在應用程序中實現(xiàn) IDELAY 功能

如何在應用程序中實現(xiàn) IDELAY 功能

評論