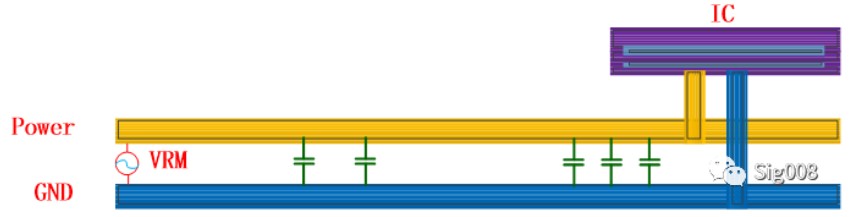

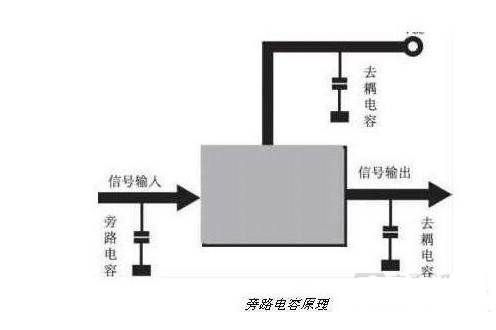

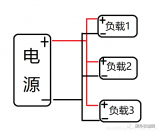

電容在PDN(power distribution network)當中的示意圖

想要知道電容如何降低PDN阻抗,首先就要知道電容自身的阻抗特性,自身寄生參數的影響。

話不多說,首先思考一下,純電容的阻抗是什么樣的?

我們可能會想到這樣一個公式:

Z=1/(2*pi*f*c)

沒錯,可是這樣不太能幫助我們理解電容在PDN中起到的作用,還不夠直觀;

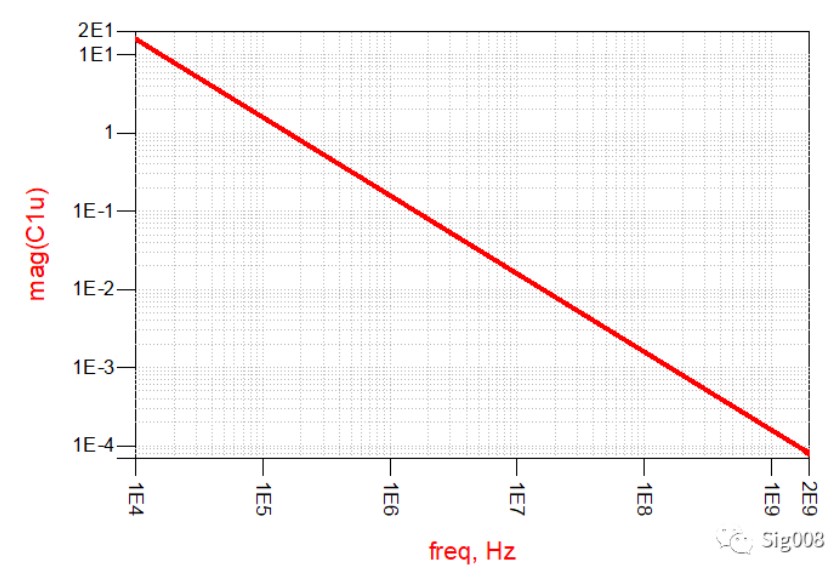

我們再思考一下,如果畫一個電容的阻抗 VS 頻率的曲線會是什么樣的呢?

如下圖:

這就是純電容的阻抗 VS 頻率曲線,在曲線中我們可以直觀的看出電容阻抗和頻率的關系;

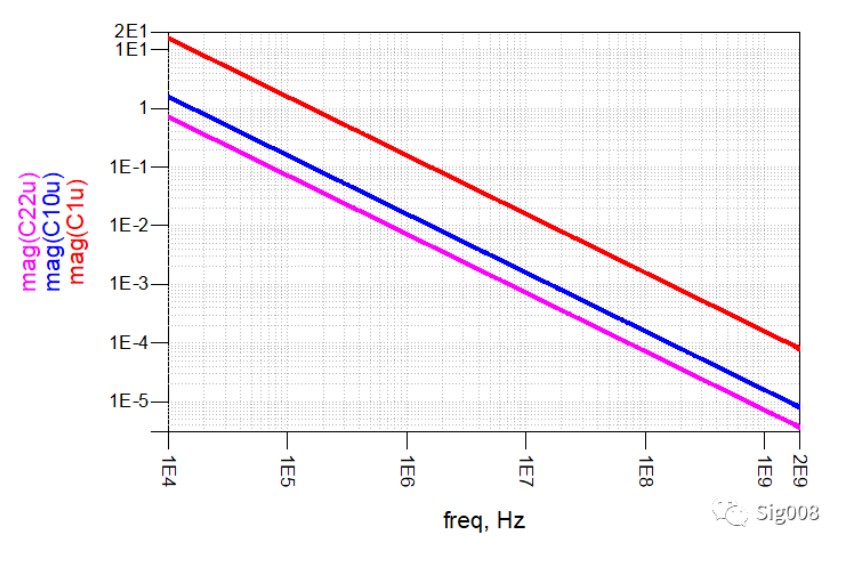

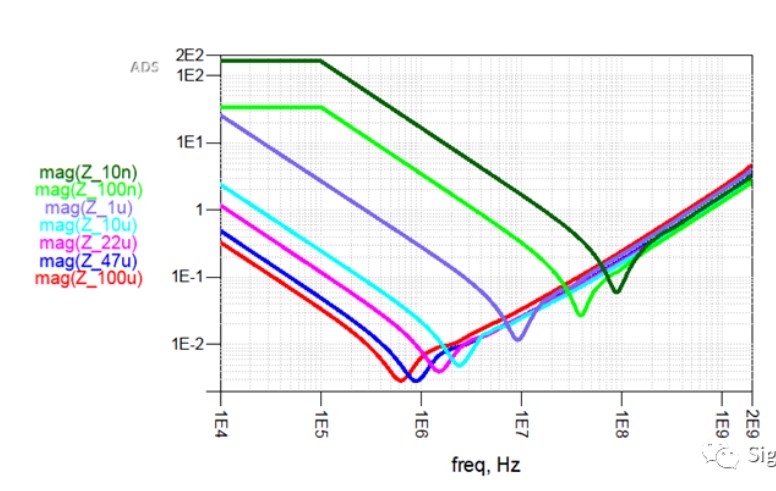

下面再來看一下不同容值電容的阻抗曲線:

容值越大,阻抗越小,整個曲線表現為整體向下平移;

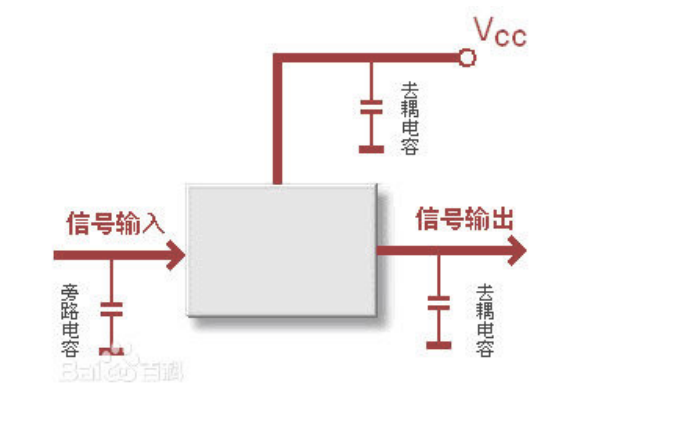

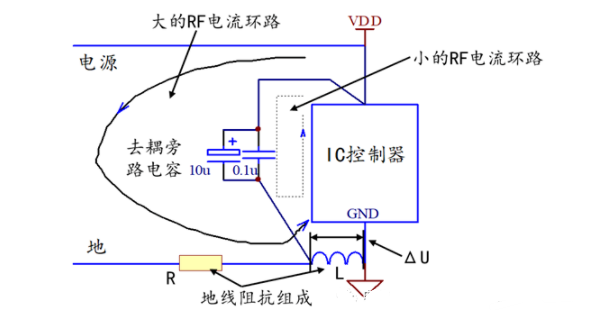

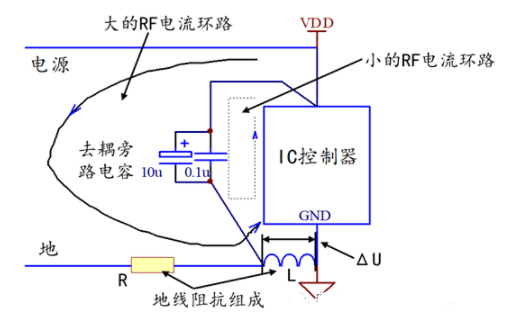

正因為電容對于高頻信號表現為低阻抗特性,因此,在PDN系統中加了很多去耦電容,但是,我們已經介紹過,電容當中還有寄生電感(ESL)和等效串聯電阻(ESR),所以我們還得研究寄生參數的影響;

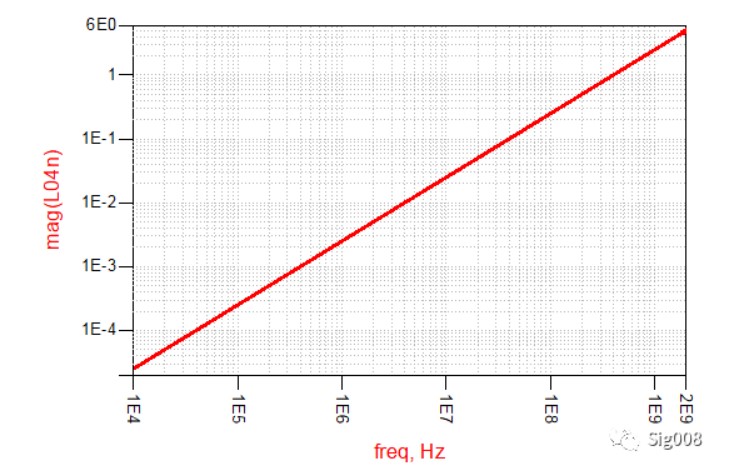

下面,我們來看一下,純電感的阻抗特性,公式如下;

Z=2*pi*L*f

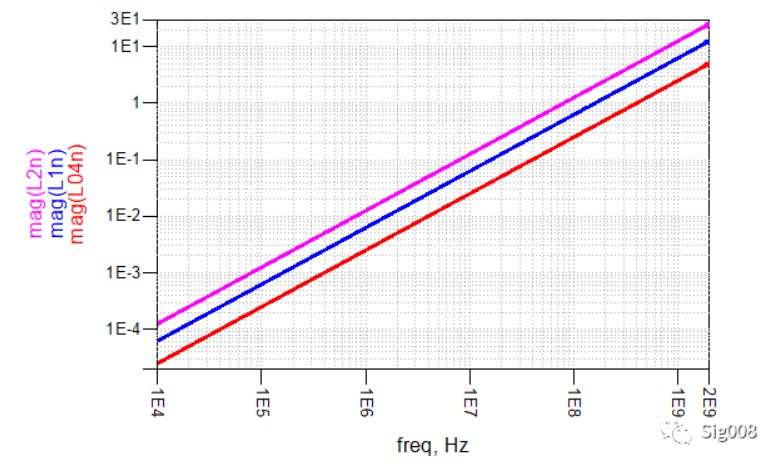

同樣,我們也看一下電感的阻抗 VS 頻率的曲線:

通過曲線,可以直觀看到,電感的阻抗隨頻率的變化關系;

下面看一下,不同電感值的阻抗曲線,相信此時大家已經有了直觀的印象,可以腦補出不同電感的曲線了:

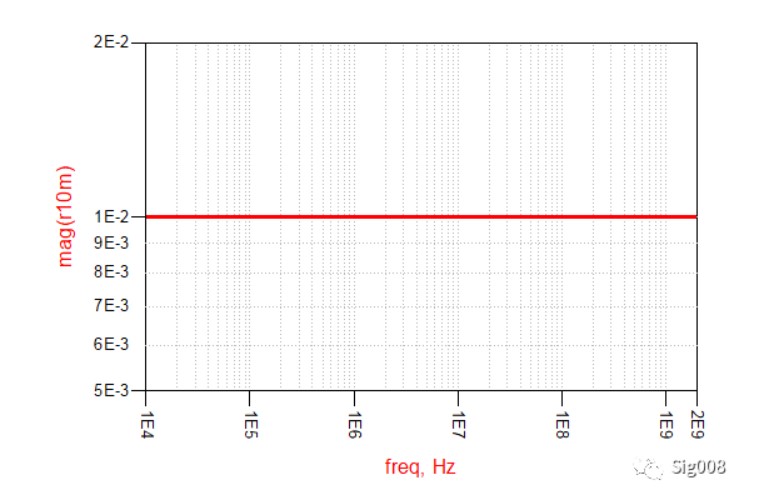

下面該電阻了,純電阻的阻抗 VS 頻率曲線如下:

這個沒什么好說的了,往下看

下面重點來了

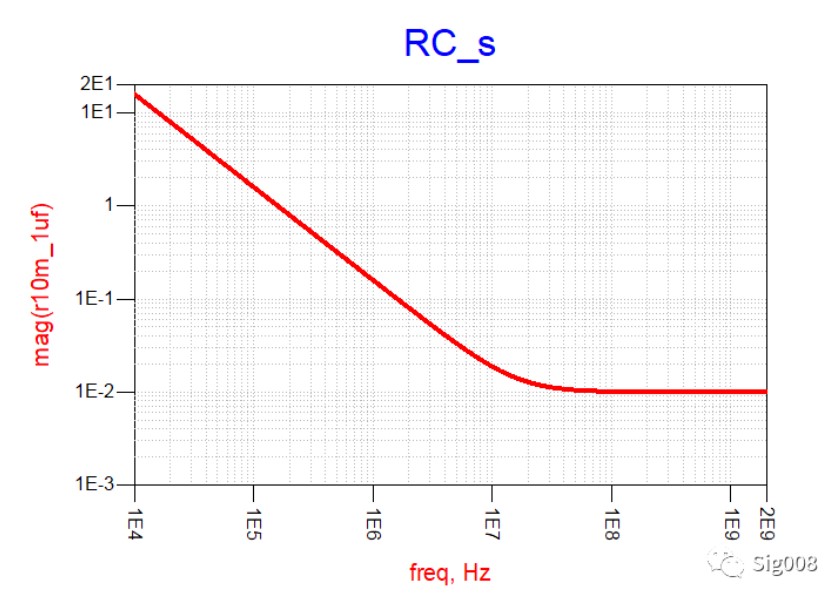

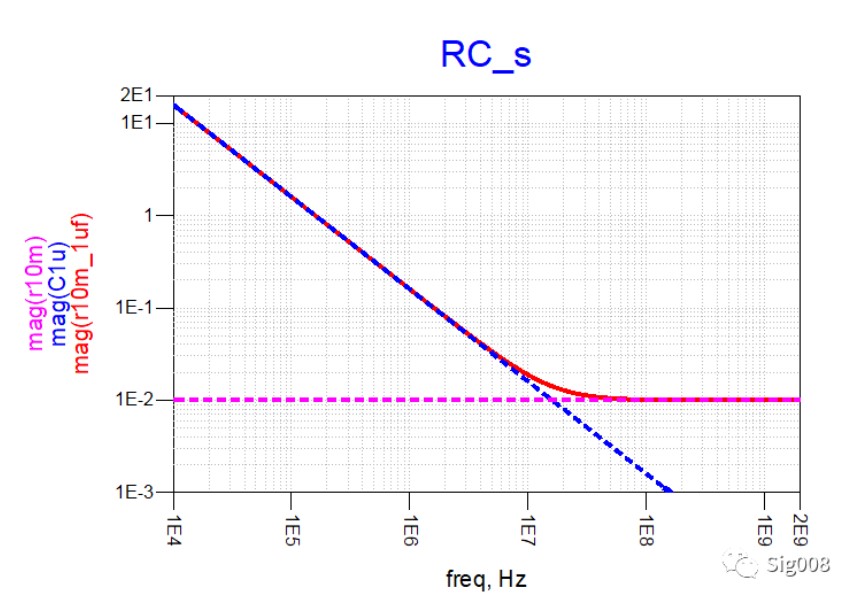

單個器件的阻抗特性知道了,那么他們串聯之后是什么樣的呢,下面請看電阻和電容串聯:

可以看到,RC串聯后,低頻部分阻抗呈現榮性,大小就是串聯電容的阻抗大小,高頻部分為阻性,大小為電阻的阻抗大小,下面請看電阻和電感串聯:

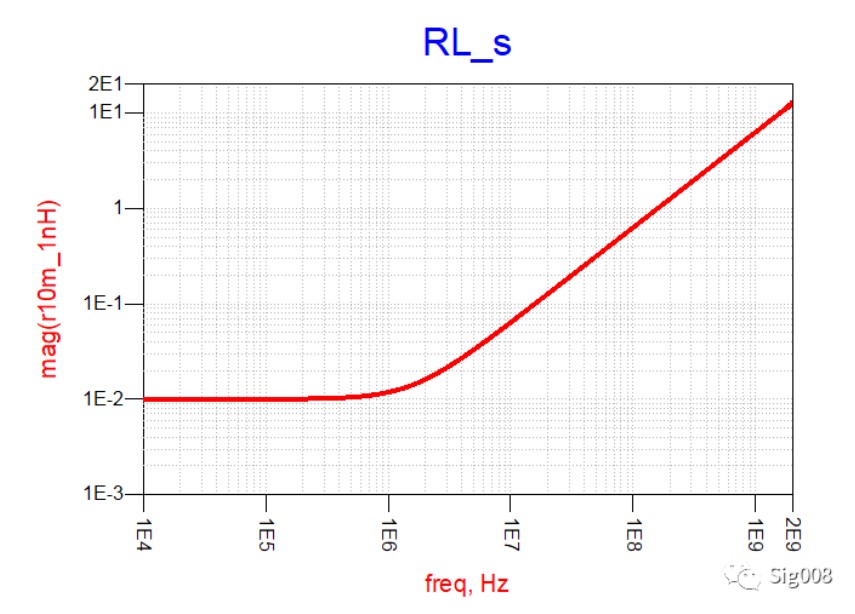

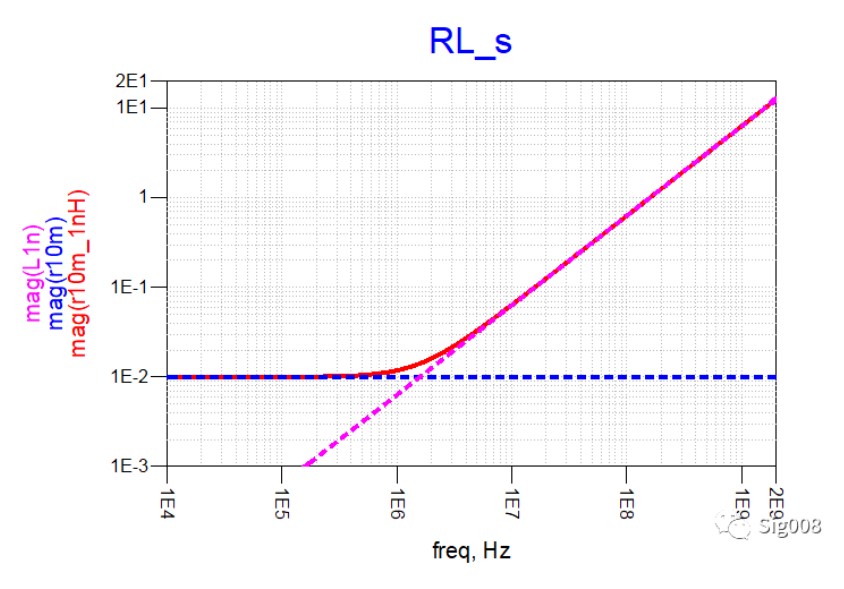

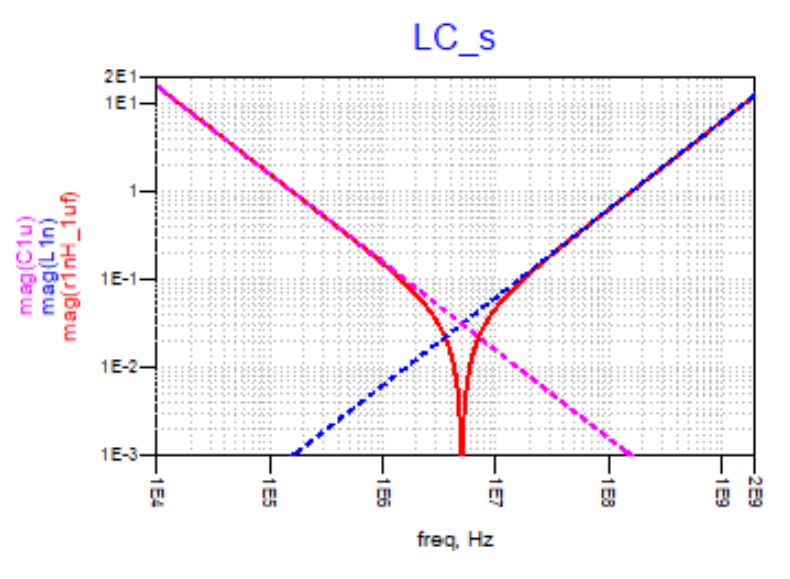

可以看到,RL串聯后,低頻部分阻抗呈現為阻性,大小為電阻的阻抗大小,高頻部分阻抗呈現感性,大小就是串聯電感的阻抗大小,下面請看電容和電感串聯:

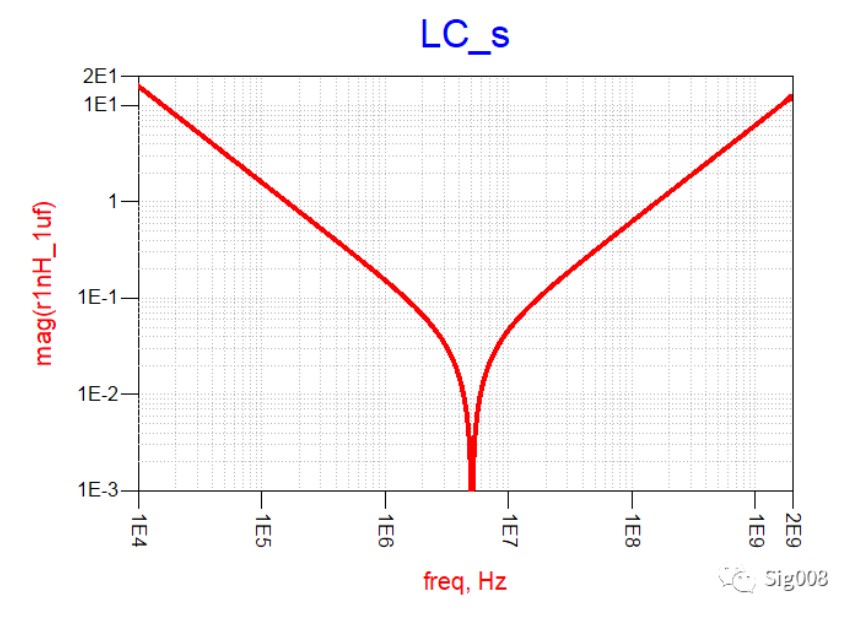

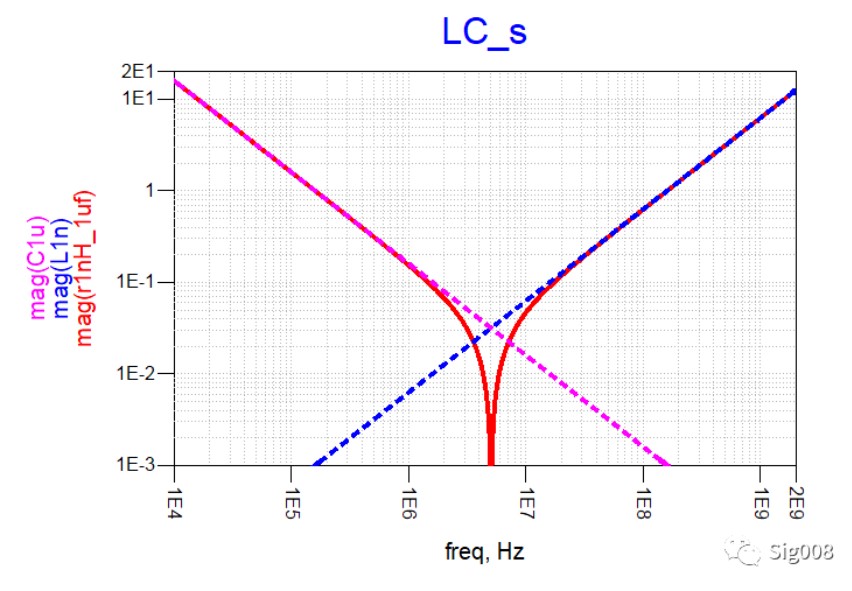

可以看到,LC串聯后,低頻部分阻抗呈現為容性,大小為電容的阻抗大小,高頻部分阻抗呈現感性,大小就是串聯電感的阻抗大小,而不同于與電阻串聯的一點就是,LC串聯會形成諧振,諧振點的頻率可以這樣計算:

在諧振點處,電容的阻抗值等于電感的阻抗值,即

Z=1/(2*pi*f*c)=2*pi*L*f

推導出f=1/(2*pi*)

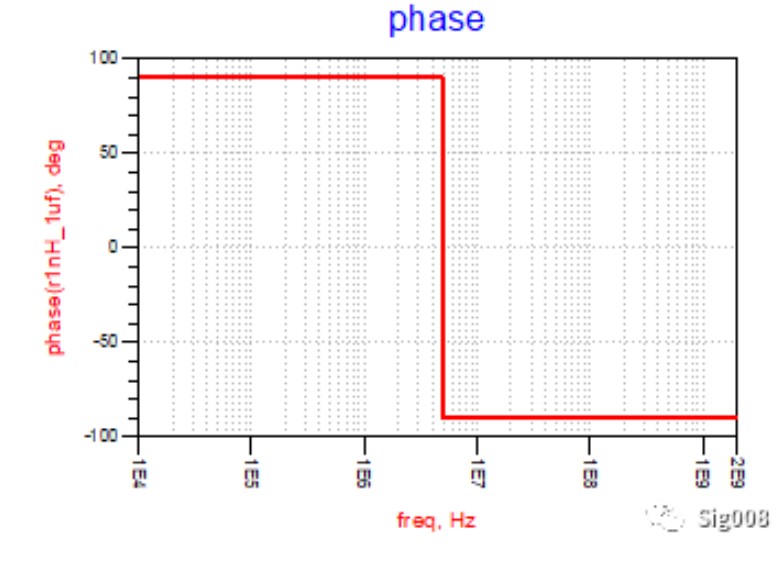

在知道了電容和電感值之后,就可以求出諧振點頻率,在此頻率之前為容性,在此頻率點之后為感性,下圖的相位就說明了這一點;

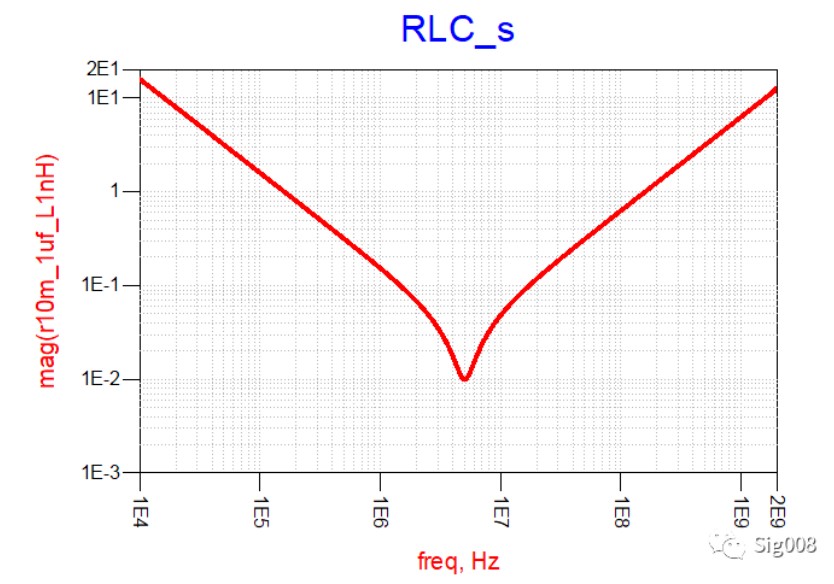

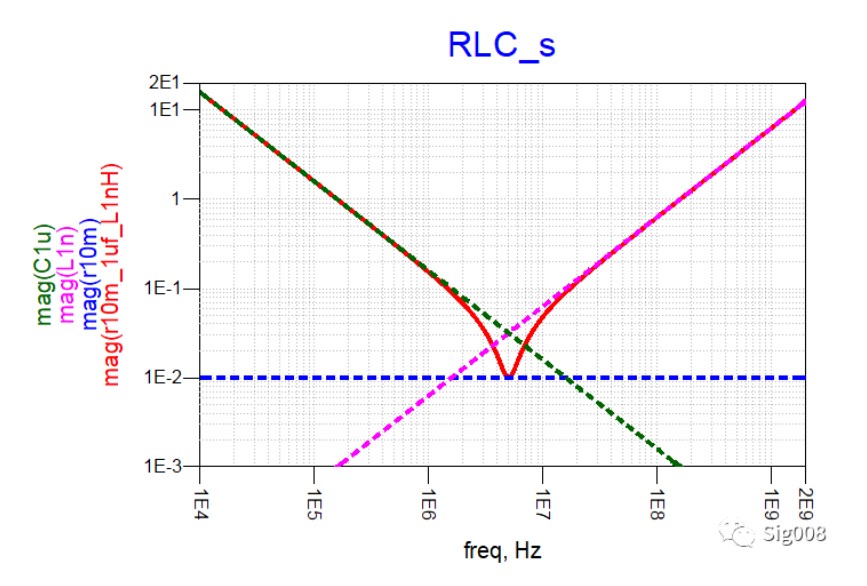

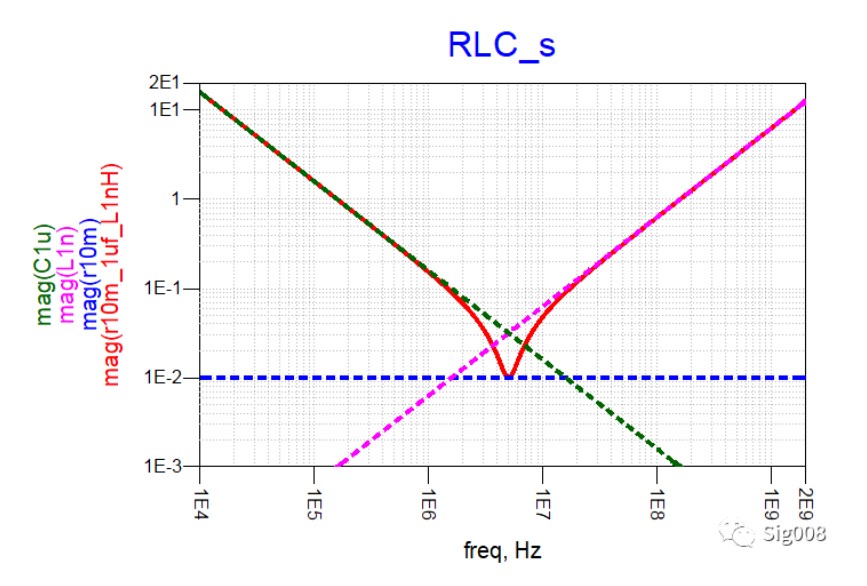

好了,以上這些是基本功,都是為了更好地了解非理想電容的阻抗特性做準備,下面請看真實電容的阻抗特性,即RLC串聯(簡單模型)

RLC串聯后的曲線和LC比較像,同樣是有一個自諧振頻點,計算方法相同,在自諧振頻點以前呈現容性,在自諧振頻點以后呈現感性,LC之間也同樣存在諧振,不同的是,此時的諧振大小是受控的,大小等于等效串聯電阻的大小;

這就是非理想電容的阻抗特性,一定要印在大腦中,正是因為電容對高頻的低阻抗特性,我們選擇電容來降低PDN阻抗,但也因為電容的寄生參數導致的在某一頻段后呈現為感性,因此要選取自諧振頻點合適的電容,下面對比幾個非理想電容的阻抗曲線,曲線來自電容廠家官方網站spice模型:

上邊就是幾組不同容值的電容阻抗曲線,從10nF到100uF,可以看到,在這個范圍內(都是貼片陶瓷電容)寄生電感基本是差不多的,而由于電容容值的不同,導致各自的自諧振頻點不同,因此在PDN中去耦時,就要選擇合適的電容;

那么電容除了自身的自諧振頻點以外,不同的電容在并聯使用時還會出現反諧振頻點,下篇文章就對相同容值電容并聯、不同容值并聯這兩種情況來看電容并聯的阻抗特性,這一特性在電容去耦時也會起到反作用,所以也是至關重要的一點。

審核編輯:劉清

-

ESR

+關注

關注

4文章

202瀏覽量

31070 -

寄生電感

+關注

關注

1文章

155瀏覽量

14588 -

PDN

+關注

關注

0文章

83瀏覽量

22687 -

電源去耦

+關注

關注

0文章

14瀏覽量

8438

發布評論請先 登錄

相關推薦

去耦電容和旁路電容的區別與聯系

看看在電源去耦應用中電容的阻抗特性

看看在電源去耦應用中電容的阻抗特性

評論