在過去 30 年中,緩沖區溢出一直是網絡傳播的攻擊中最常被利用的漏洞。考慮到緩沖區的創建方式,這并不奇怪。

下面是 C 語言中的一個示例:

步驟 1.程序員使用 malloc 函數并定義緩沖區內存量(例如 32 字節)

步驟2.返回一個指針,指示內存中緩沖區的開始

第3步。程序員在需要讀取或寫入該緩沖區時使用指針(僅)作為引用

有了指針,程序員很容易忘記分配給給定緩沖區的實際內存量。編譯器使用元數據在組裝過程中分配適當的緩沖區大小,但此元數據通常在生成時被丟棄以減少占用空間。

如果程序內或程序之間傳輸的數據隨后超出了最初定義的緩沖區大小,則該數據信息將覆蓋相鄰的內存。這可能導致內存訪問錯誤或崩潰,以及安全漏洞。

緩沖區溢出和漏洞利用

黑客可以使用堆棧緩沖區溢出將可執行文件替換為惡意代碼,從而允許他們利用堆內存或調用堆棧本身等系統資源。例如,控制流劫持利用堆棧緩沖區溢出將代碼執行重定向到正常操作中使用的位置以外的位置。

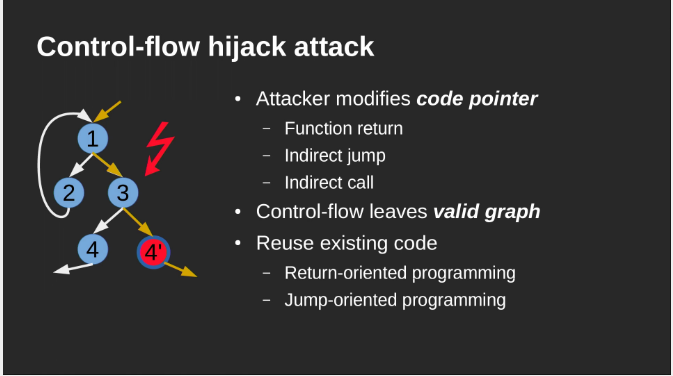

一旦負責控制流, 控制流劫持者可以修改指針和重用現有代碼, 同時也可能替換代碼。控制流的命令還允許攻擊者修改指針以用于間接調用、跳轉和函數返回,從而留下有效的圖形以向防御者隱藏其操作。

圖 1.控制流劫持是一種常見的攻擊,它利用緩沖區溢出來征用系統堆棧。

盡管動態地址空間布局隨機化 (ASLR) 機制和堆棧 Canaries 用于在代碼執行發生之前檢測和防止緩沖區溢出,但此類威脅仍然是一個挑戰。

安全性:軟件還是芯片?

ASLR 和堆棧 Canary 是基于軟件的緩沖區溢出保護機制,它們確實使攻擊者更難利用緩沖區溢出。例如,ASLR動態地重新定位內存區域,以便黑客必須有效地猜測目標組件(如基本可執行文件,庫以及堆棧和堆內存)的地址空間。不幸的是,最近的漏洞,如幽靈和崩潰泄漏來自CPU分支預測器的信息,這限制了ASLR的有效性,原因顯而易見。

另一方面,堆疊金絲雀在內存中返回指針之前插入小整數。檢查這些整數以確保它們在例程可以使用相應的返回指針之前未發生更改。盡管如此,黑客仍有可能讀取金絲雀,如果他們確定包含正確的金絲雀值,則可以簡單地覆蓋它和隨后的緩沖區而不會發生事故。此外,雖然 Canary 保護控制數據不被更改,但它們不保護指針或任何其他數據。

當然,基于軟件的安全解決方案的另一個挑戰是它們非常容易受到錯誤的影響。據估計,每1000行代碼存在15-50個錯誤,這意味著解決方案中存在的軟件越多,漏洞的數量就越多。

當解決疾病而不是緩沖區溢出的癥狀時,一種更強大的方法是在硅中實現安全性 - 雖然堆棧緩沖區溢出利用旨在操縱軟件程序,但解決此類攻擊的根本原因始于意識到處理器無法確定給定程序是否正確執行。

除了減輕軟件錯誤的影響之外,硅不能遠程更改。但是,必須對處理器或芯片IP進行編程,以便在運行時識別嘗試寫入內存或外圍設備的指令是否在執行合法或非法操作。

多佛微系統公司開發了這樣一種名為CoreGuard的技術。

運行時的硅安全性

CoreGuard 是一塊芯片 IP,可以與 RISC 處理器架構集成,以便在運行時識別無效指令。該解決方案以 RTL 形式提供,可針對各種功率和面積要求進行優化,或進行修改以支持自定義處理器擴展。

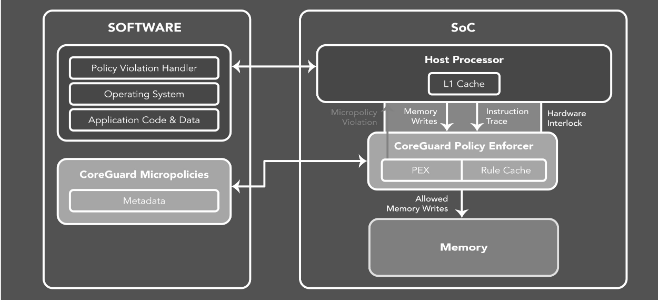

如圖 2 所示,CoreGuard 體系結構包括一個硬件互鎖,用于控制主機處理器與系統其余部分之間的所有通信。硬件互鎖將這些通信匯集到策略實施器中。

圖 2.多佛微系統的CoreGuard安全IP使用微策略和硬件聯鎖來識別和阻止無效指令,然后再執行。

另外,CoreGuard 使用稱為微策略的可更新安全規則,這些規則是用高級專有語言創建的簡單管理策略。這些規則安裝在與其他操作系統或應用程序代碼隔離的安全、不可訪問的內存區域中。CoreGuard 還在此處為通常被編譯器丟棄的應用程序元數據保留了少量內存分配,用于為系統中的所有數據和指令生成唯一標識符。這些組件在系統引導時加載。

當指令嘗試在運行時執行時,以特權模式運行的 CoreGuard 策略執行核心或主機處理器會根據定義的微策略交叉引用指令的元數據。硬件互鎖確保處理器僅向存儲器或外設輸出有效指令,從而防止無效代碼完全執行。應用程序會收到類似于被零除錯誤的策略違規通知,并通知用戶。

與主機處理器集成所需的一切,以支持指令跟蹤輸出、失速輸入、不可屏蔽中斷 (NMI) 輸入和中斷輸出。對于非芯片設計人員,多佛微系統公司最近宣布,其CoreGuard技術正在被設計到某些恩智浦處理器中。

消除攻擊類別

在緩沖區溢出的情況下,像CoreGuard這樣的技術的好處是顯而易見的。可以合并作為經常丟棄的編譯器元數據的一部分捕獲的緩沖區大小,以限制攻擊者從整個網絡操作系統堆棧的能力。更進一步,相同的原則通常可以應用于控制流劫持,因為從內存中的各個點返回可以在發生之前受到限制。

在實踐中,這種實時感知也為安全行業創造了一個新的競爭環境。通過在損壞發生之前識別錯誤或攻擊,用戶可以選擇動態重新分配內存,切換到單獨的,更安全的程序或記錄事件,同時繼續運行相同的程序。如何繼續完全取決于應用程序或業務案例的需求。

審核編輯:郭婷

-

cpu

+關注

關注

68文章

10826瀏覽量

211160 -

編譯器

+關注

關注

1文章

1618瀏覽量

49052 -

IOT

+關注

關注

186文章

4180瀏覽量

196239

發布評論請先 登錄

相關推薦

單片機中的幾種環形緩沖區的分析和實現

esp32-s3 uvc攝像頭緩沖區溢出是什么原因呢?

ESP8266是否可以添加AT命令并使接收緩沖區大小可調?

ESP8266有雙緩沖區嗎?

創建DMA通道時,能否將DMA緩沖區的大小指定為8字節,并將DMA緩沖區的編號指定為1?

stm32野火開發板上做USB通信,PC端USB的緩沖區和串口緩沖區的大小是多少?

交換機與路由器緩沖區:尋找完美大小

消除IoT上的緩沖區溢出漏洞

消除IoT上的緩沖區溢出漏洞

評論