FPGA實現CORDIC核的應用和解卷繞

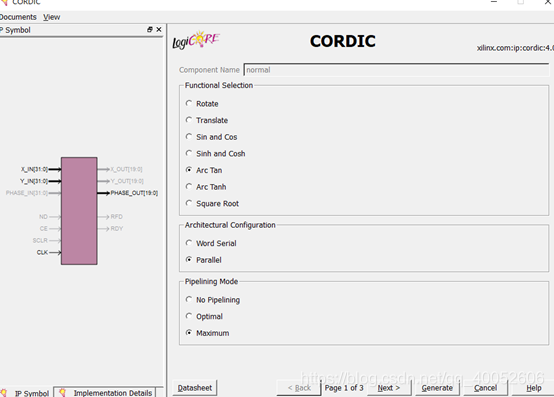

在FPGA硬件實現CORDIC的邏輯其實是很簡單的,就是設置好輸入輸出的位寬,然后建立好對應的精度表,通過旋轉加得到運算結果。但是在IP核的使用中需要特別注意輸入數據的位寬和大小。IP核的申請配置如下圖:

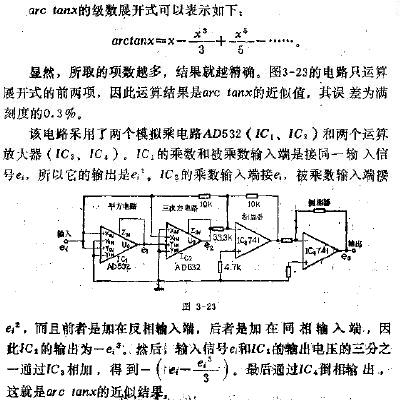

這個選項卡里主要是選擇功能、處理速度和模式。

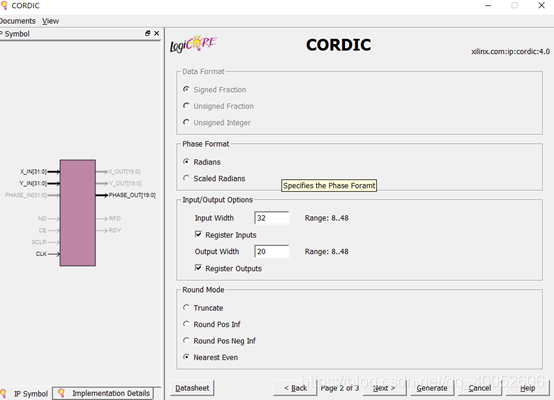

這個選項卡主要是選擇弧度輸出還是±1輸出、輸入輸出位寬和截位方式,一般選擇四舍五入的截位方式。

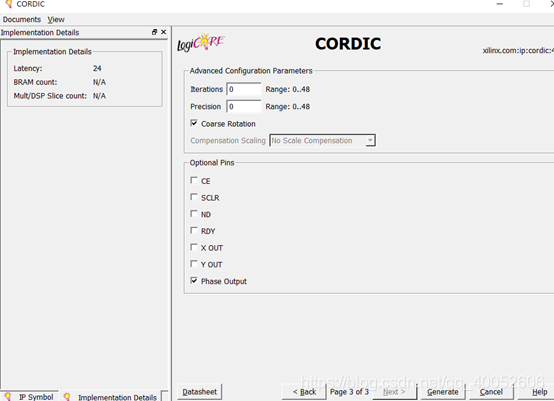

這個選項卡是配置輸出項的。還需要特別注意的就是輸入與輸出的延時latency;

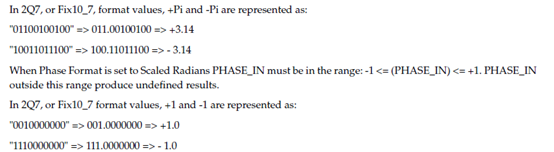

這個IP的申請比較簡單,在實際仿真時需要注意的是輸入數據的大小。在官方文檔LogiCORE IP CORDIC v4.0中對輸入數據有著很嚴格的規定,我們在使用時也需要嚴格的遵守。數據輸入規定如下圖:

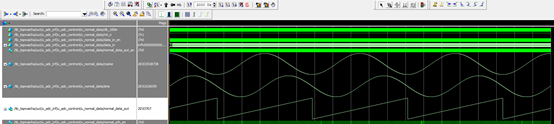

在滿足了上面IP的例化后通過modelsim仿真。分別輸入兩個信號,通過CORDIC核輸出相位信號,仿真波形如下圖:

從圖中可以看出輸入信號是連續的,而輸出信號存在跳躍,這是因為CORDIC核只能輸出-3.14到+3.14之間的信號,因此輸出信號存在著卷繞現象,這樣的輸出結果不能反映實際的相位信息,因此需要進行解卷繞處理。

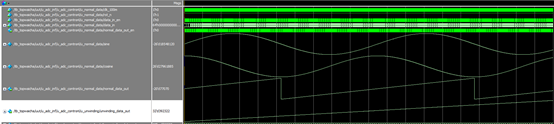

在CORDIC核輸出的相位信號發聲突變是在-3.14到+3.14處,因此我們只要根據突變前后數據的符號和大小即可通過加上或者減去6.28來實現解卷繞的過程。利用FPGA進行解卷繞時至少需要兩個點,通過判斷這兩個點的符號和差值的絕對值是否等于6.28來進行確定相位突變的點和方向。在實際代碼仿真可知通過兩個點判斷這種方式是可行的,仿真波形如下圖所示:

審核編輯:劉清

-

FPGA

+關注

關注

1626文章

21665瀏覽量

601814 -

IP核

+關注

關注

4文章

326瀏覽量

49428 -

CORDIC算法

+關注

關注

0文章

17瀏覽量

9713

原文標題:FPGA實現CORDIC核的應用和解卷繞

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

RX系列三角函數單元(TFU)的使用介紹

基于FPGA的數字三相鎖相環的基本原理分析

labview中的三角函數問題

Cordic IP用戶手冊

利用Cordic算法來計算三角函數的值

基于三角函數搜索因子的混合蛙跳算法

歐拉公式與三角函數_歐拉公式推導三角函數

如何使用Cordic算法C語言實現三角函數的計算

如何使用DSP匯編語言實現高精度的三角函數

在FPGA中利用CORDIC算法IP核實現三角函數關系的轉換

在FPGA中利用CORDIC算法IP核實現三角函數關系的轉換

評論