0 引言

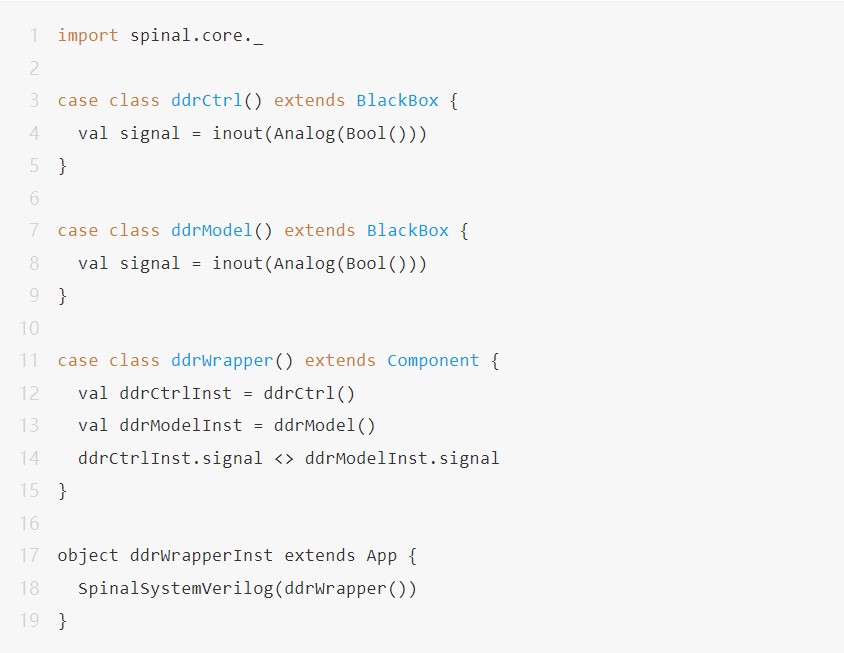

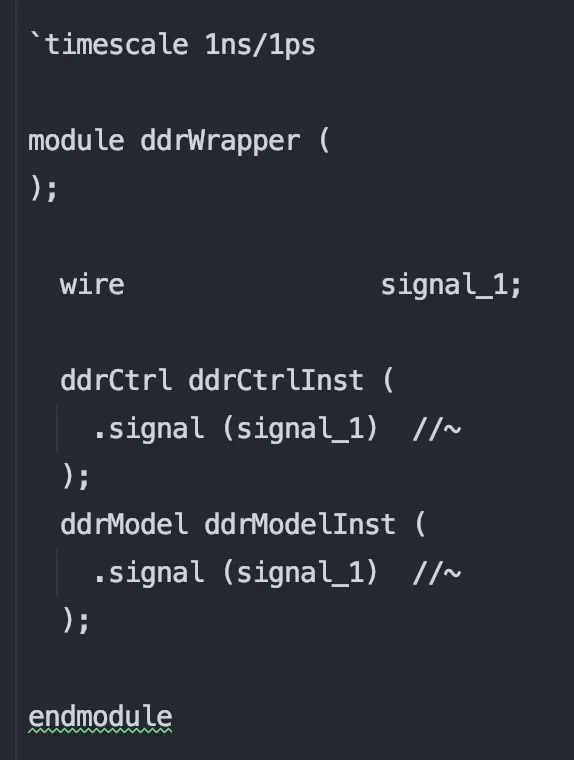

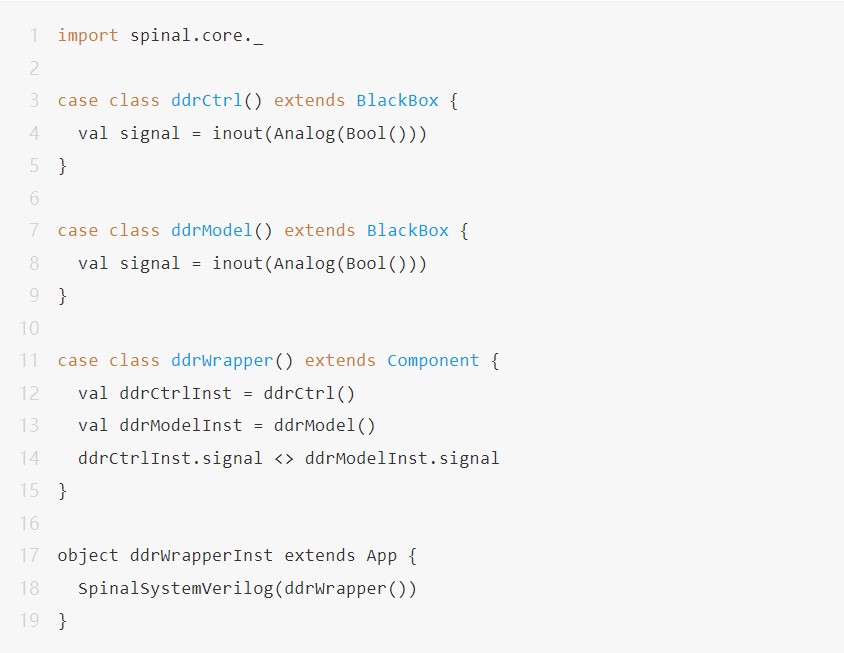

在SpinalHDL 1.7.0版本里,在仿真方面開始支持了VCS,這解決了在FPGA設計里采用Verilator時無法仿真廠商IP的問題。故此,前段時間嘗試了把集成FPGA廠商DDR IP的測試。不曾想卻遇到了一個從未遇到的錯誤。在DDR仿真里一般由控制器IP以及廠商的Memory Model組成,我將其各自封裝成了一個Blackbox,而在集成的時候確過不去了。為簡單起見,這里采用下面的代碼示例:

?

?

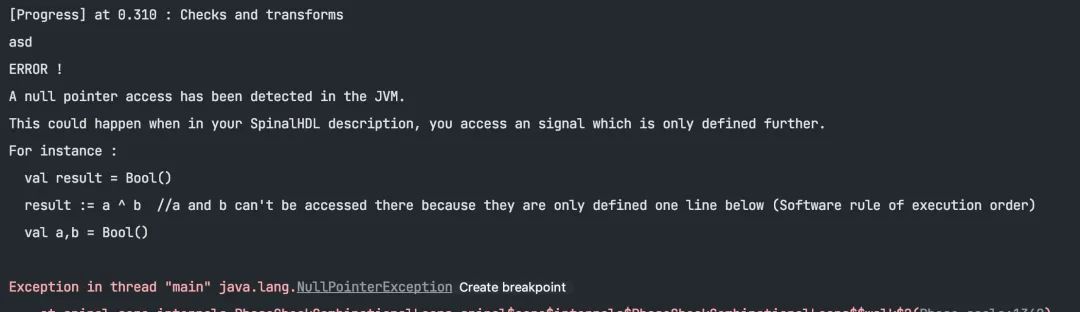

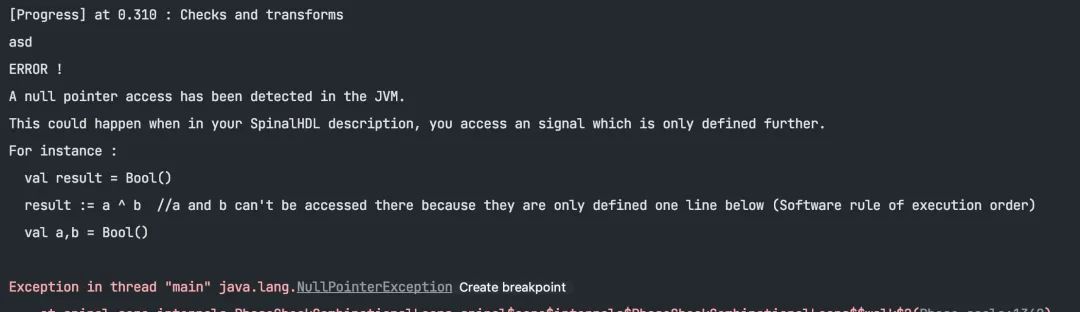

看起來似乎沒啥毛病對吧,而且在之前寫Verilog時候inout端口也是這么連接的。然而在運行的時候卻報了下面的錯誤:

這錯誤類型我熟,但貌似明顯我并沒有犯這個錯誤啊…… 》解決之道

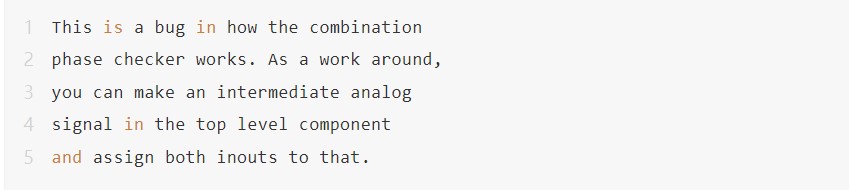

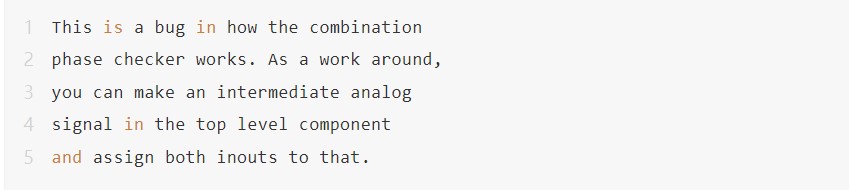

首先需要說明的是,這種使用場景也僅在仿真的時候會使用到,而真實的設計場景是不會有這么用的。但上面這個場景確實存在。在git上大神給出了下面的答復:

??

??

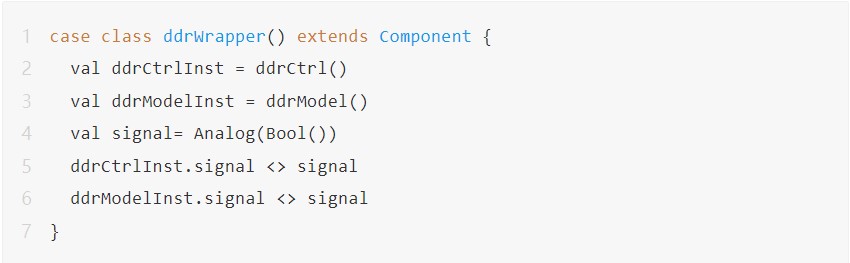

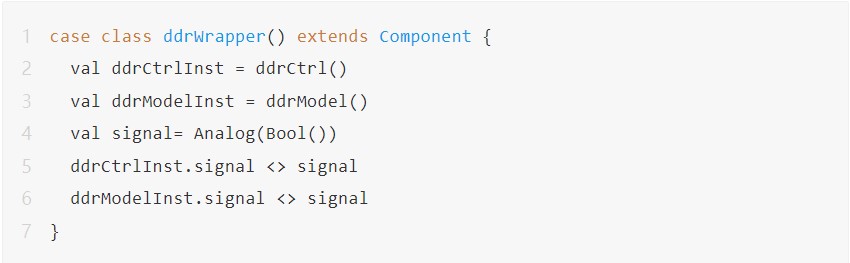

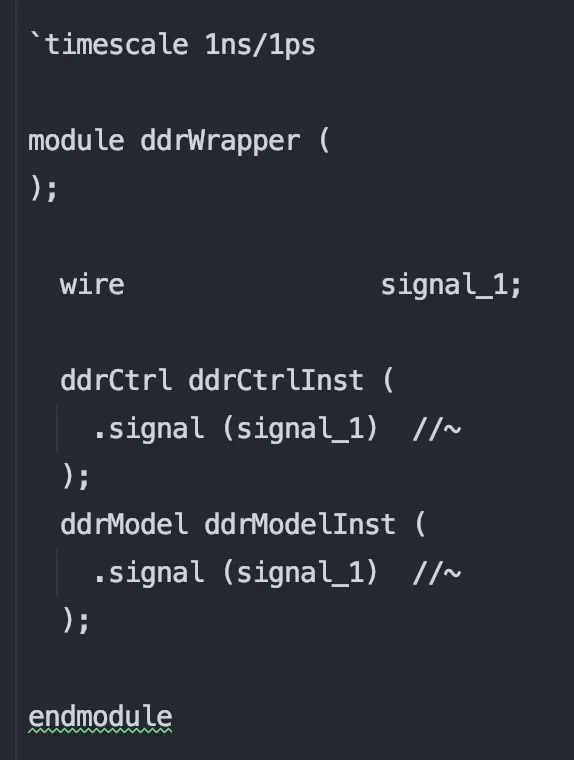

針對這種場景,這里給出一個解決方案,ddrWrapper重寫如下:

修改后即可達成我們想要的效果:

審核編輯:劉清

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

原文標題:踩坑系列——inout連接不上

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

相關推薦

芯片外部引腳很多都使用inout類型的,為的是節省管腿。一般信號線用做總線等雙向數據傳輸的時候就要用到INOUT類型了。就是一個端口同時做輸入和輸出。 inout在具體實現上一般用三態

發表于 01-17 10:08

。 inout在具體實現上一般用三態門來實現。三態門的第三個狀態就是高阻'Z'。 當inout端口不輸出時,將三態門置高阻。這樣信號就不會因為兩端同時輸出而出錯了,更詳細的內容可以搜索一下三態門tri-state

發表于 08-09 08:21

是否可以將一個inout端口直接連接到另一個inout端口?在我的應用中,這個特定的信號只能連接兩個外部設備,但是通過FPGA。它是兩個外部設備的雙向引腳。我已經看到其他地方建議使用類

發表于 04-15 15:08

和Demo APP連接不上,求教如何解決?

發表于 04-24 04:50

請教一個問題,兩個2540設備,一主一從,主查找到這個從設備,會啟動與從設備的連接動作,但是這個時候,從掉電了,我監控到的結果是主一直停留在connecting的狀態,就是啟動建立連接的時候,為什么連接

發表于 11-06 09:32

; data_inout_buffer); 當我試圖映射信號時,它顯示錯誤:錯誤:Xst:528 - 信號單位中的多源>;此信號連接到多個驅動程序。(2)我無法監控chipcope pro分析儀中

發表于 04-07 08:04

VS-RK3399安卓主板adb 鏈接不上問題如何解決?近來有不少人都在問,為啥RK3399的android系統,怎么都連接不

發表于 07-20 15:09

Inout端口信號做輸入時,觀察例子中的輸出Data_out_t就應該是高阻態的,Inout在具體實現上一般用三態門來實現。三態門的第三個狀態就是高阻''Z''。當Inout端口不輸出

發表于 11-11 10:24

?3871次閱讀

。 ? ? ? ?芯片外部引腳很多都使用inout類型的,為的是節省管腿。就是一個端口同時做輸入和輸出。 inout在具體實現上一般用三態門來實現。三態門的第三個狀態就是高阻'Z'。當inou

![的頭像]() 發表于

發表于 08-13 13:45

?1.7w次閱讀

新一代互聯網絡在高性能、高可擴展性、高可用性和易部署性等方面提出了更高的要求,使得路由器結構越來越復雜,我們需要掌握的相關知識也越來越多,那么你知道路由器pppoe連接不上怎么辦嗎?下面是小編整理的一些關于路由器pppoe

發表于 04-27 10:34

?4.5w次閱讀

現在越來越多的小伙伴對于教大家為什么wifi有信號卻連接不上的方法這方面的問題開始感興趣,因為大家現在都是想要熟知,那么既然現在大家都想要知道教大家為什么wifi有信號卻連接

發表于 06-04 09:15

?1.3w次閱讀

Xshell為什么連接不上服務器?Xshell可在Windows桌面下訪問不同系統下的遠程終端服務器,并且進行操作控制。新手用戶有時在用Xshell遠程連接Linux服務器時,可能

![的頭像]() 發表于

發表于 06-09 13:47

?4428次閱讀

芯片外部引腳很多都使用inout類型的,為的是節省管腿。一般信號線用做總線等雙向數據傳輸的時候就要用到INOUT類型了。就是一個端口同時做輸入和輸出。

![的頭像]() 發表于

發表于 06-25 09:10

?6026次閱讀

Verilog語言是一種硬件描述語言(HDL),用于描述數字邏輯電路和系統。它是一種非常強大且廣泛使用的語言,在數字電路設計中扮演著重要的角色。其中, inout 是Verilog中的一種信號類型

![的頭像]() 發表于

發表于 02-23 10:15

?2772次閱讀

InOut類型的仿真是指通過計算機軟件模擬和模擬硬件組件之間的輸入和輸出交互過程,以驗證和評估電子電路設計的正確性和性能。下面將詳細介紹InOut類型的仿真及其實現方法。 一、InOut類型的概述

![的頭像]() 發表于

發表于 02-23 10:17

?888次閱讀

?

?

??

??

inout連接不上如何解決呢

inout連接不上如何解決呢

評論