本文將通過了解同步電路、時鐘傳輸和時鐘分配網絡,進而了解什么是時鐘偏差(clock skew)以及它對現代系統的影響。

現代數字電子產品設計的最大挑戰之一是滿足時序約束的能力。保持可預測和組織良好的操作邏輯流程的方法之一是在數字電路中擁有控制良好、定義明確的時序。 clock skew是這些電路中的一個設計考慮因素,如果沒有得到適當的考慮,它可能是一個重要的問題來源。

上,在許多情況下,系統的clock skew可能是整個系統速度和時鐘頻率的限制因素。要了解clock skew,我們必須首先討論同步電路。同步電路和時鐘——最小時鐘周期計算 大多數現代數字計算機的一個基本特征是同步電路。

同步電路需要一種計時機制來保持有序和周期性的時序邏輯流。在數字電子學中,這種計時機制被稱為時鐘,簡單來說,它是一個具有恒定頻率的方波。

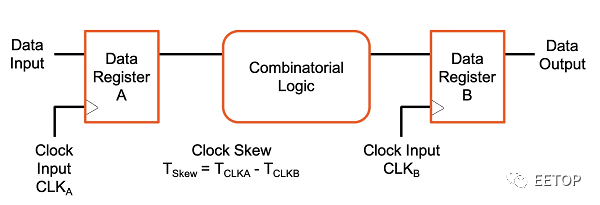

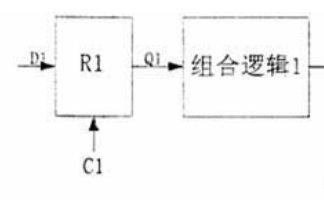

如圖 1 所示,這些電路通過將靜態數據存儲在數據寄存器中來工作,該數據寄存器旨在鎖存數據,直到寄存器遇到時鐘的上升(或下降)沿。當時鐘沿發生時,數據從寄存器中釋放,通過組合邏輯塊發送,然后存儲在下一個寄存器中。

圖 1. 具有兩個順序寄存器的數據路徑同步電路。

這些操作發生的頻率由時鐘頻率設置,時鐘頻率由其他幾個參數設置。最小時鐘周期的一般公式定義為: Tc=tpcq+tpd+tsetup+tskew 式中:

Tc是時鐘周期

tpcq是數據寄存器時鐘到 Q 的時間

tpd是組合邏輯傳播延遲

tsetup是下行寄存器的建立時間

tskew是兩個寄存器之間的時鐘偏差

最大時鐘頻率定義為1/Tc

時鐘傳送和clock skew 由于數字邏輯往往是同步電路,所有邏輯塊的精確時序對于正確的系統行為至關重要。當考慮將圖 1 中的設置從一個數據路徑擴展到數百萬個數據路徑(因為它存在于實際芯片設計中)時,很快就會發現保持一切同步是一項不小的挑戰。

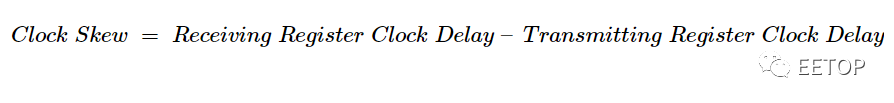

在實踐中,時鐘信號通常由晶體振蕩器生成,饋入鎖相環 (PLL),并在整個 IC 中分布到系統內的每個邏輯塊和晶體管。這種追求中最大的挑戰之一就是clock skew,它可以定義為順序相鄰寄存器的時鐘信號到達時間之間的差異。 這種情況在數學上可以定義為:

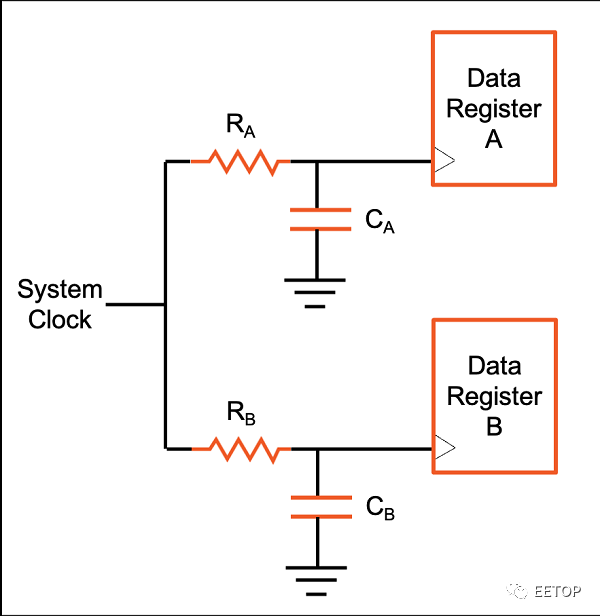

發生clock skew的傳統設置如圖 2 所示,其中時鐘分配網絡中的延遲導致數據寄存器 B 比寄存器 A 更晚地接收其時鐘信號。

圖 2. 時鐘偏差通過在時鐘傳輸網絡中插入延遲來證明。

如果接收寄存器晚于發送寄存器接收時鐘,則偏移可以定義為正,反之則定義為負。clock skew成為數字設計中的一個嚴重問題,因為它可能違反同步電路所依賴的時序約束。

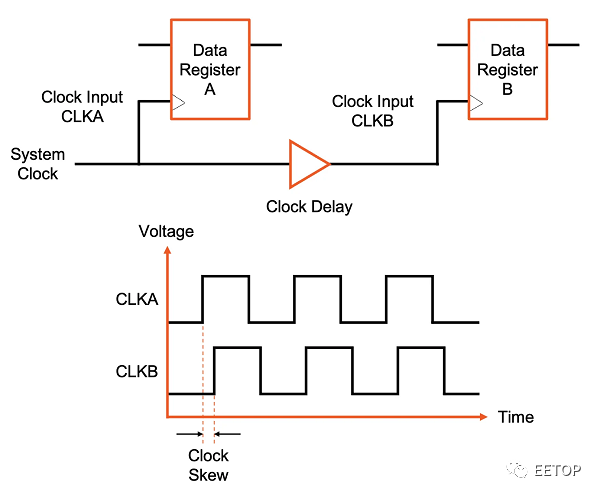

例如,給定一個恒定的時鐘頻率和負偏斜,如圖 3 所示,時鐘到達接收寄存器 B 的時間要比發送寄存器 A 早得多。

在這種情況下,從發送寄存器發出的數據將到達時鐘到達后接收寄存器。這里,數據不滿足接收寄存器的建立和保持要求(即,在時鐘到達時,接收登記處還沒有現成的數據)。因此,由于接收寄存器不能安全地鎖存數據,數據將會丟失。這個概念會產生復合效應,因為后續依賴丟失數據的邏輯操作也會失敗。 ?

?

圖 3. 負時鐘偏移導致數據在其時鐘之后到達接收寄存器 B。 正如我們在最大時鐘頻率等式中看到的,clock skew的增加將增加最小時鐘周期并降低系統的最大時鐘頻率。這是因為clock skew有效地增加了排序開銷,減少了組合邏輯中有用工作的可用時間。還值得注意的是,時鐘不需要同時到達,但clock skew通常存在可接受的誤差范圍。

clock skew的原因

雖然造成clock skew的原因有很多,但它們最終都歸結為時鐘分配網絡中的延遲差異。

clock skew的一個原因是時鐘分配網絡中互連之間的長度不同。如果到兩個連續寄存器的時鐘傳輸路徑中的互連長度變化很大,則可能會發生clock skew。沿著較短互連行進的時鐘將比沿著較長互連行進更快地到達其寄存器。

clock skew的另一個原因可能是時鐘分配網絡中互連延遲的差異。即使兩條時鐘傳輸路徑的長度相同,它們也會由于諸如電阻、電容或電感耦合等寄生效應而經歷不同的延遲。

在圖 4 的示例中,RC 寄生效應的任何差異都會導致寄存器 A 和 B 的時鐘到達時間延遲不同。線路上延遲較大的時鐘信號自然會比延遲較小的信號更晚到達其目的地. 設計具有相同延遲的互連可能是一項極其困難的任務。

圖 4. RC 寄生效應的變化會導致時鐘偏移。

clock skew也可能是由時鐘信號的邏輯路徑延遲的差異引起的。例如,在包括時鐘門控的設計中,時鐘的傳輸路徑中可能存在額外的門,每個門都具有自己的負載電容和傳播延遲。如果不平衡,邏輯路徑的差異會導致時鐘傳遞時間不等。 其他原因可能包括溫度變化、制造變化和材料缺陷。

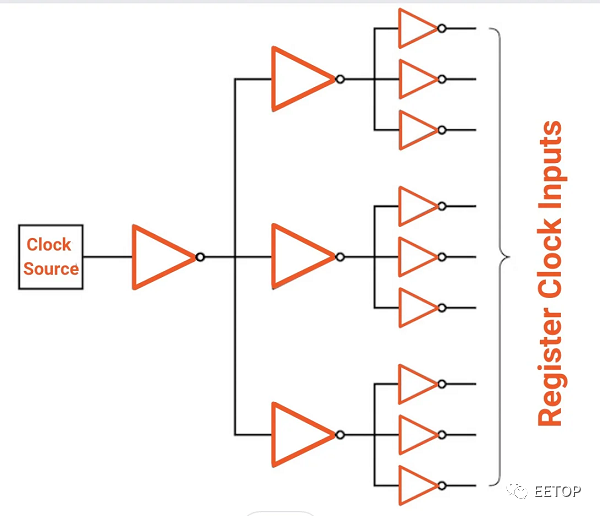

使用時鐘分配網絡最大限度地減少時clock skew

隨著時鐘頻率的增加,clock skew可能會成為一個更具挑戰性的問題,因為隨著時鐘頻率的提高,誤差幅度會顯著降低。為了最大限度地減少clock skew,復雜的同步電路采用類似于圖 5 所示的時鐘分配網絡。這些通常也稱為時鐘樹。時鐘樹中的每個反相器都會放大時鐘信號以驅動時鐘樹的下一級。目標是讓時鐘信號同時到達所有寄存器輸入。

圖 5.具有并行時鐘驅動器的時鐘分配網絡示例。

對于具有數百萬甚至數十億晶體管的超大型 IC,時鐘分配網絡可能會比圖 4 的簡單示例復雜得多。這些網絡的創建通常由EDA軟件自動處理。工程師輸入目標頻率、寄存器設置和保持時間限制以及最大時鐘偏差等關鍵參數。然后,軟件生成時鐘分配網絡以滿足目標時序約束。

結論

clock skew是數字集成電路設計中需要考慮的重要課題。如果沒有正確考慮,時鐘偏差會對系統性能造成嚴重破壞,導致系統操作不當、數據丟失或成為系統時鐘頻率的限制因素。

審核編輯:劉清

-

數據寄存器

+關注

關注

0文章

33瀏覽量

7747 -

數字電路

+關注

關注

193文章

1601瀏覽量

80511 -

同步電路

+關注

關注

1文章

60瀏覽量

13299

原文標題:什么是clock skew?一文了解時鐘分配網絡中的時鐘偏移

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

怎么了解時序報告中的時鐘偏差

怎么消除5ns偏斜

為減少數據和時鐘偏差應遵循哪些通用FPGA編碼規則?

BUFGMUX定時時鐘偏差太大

使用時鐘PLL的源同步系統時序分析

Skew Correction Using Delay Li

三個命令生成的報告中均可顯示Clock Skew的具體數值

同步電路設計中CLOCK SKEW的分析說明

什么是時鐘偏差(clock skew)以及它對現代系統的影響

什么是時鐘偏差(clock skew)以及它對現代系統的影響

評論