簡介

IC互聯(lián)總線(PC總線)的應用正越來越廣泛地擴展到包括消費電子、通信設備和工業(yè)設備中。在實際應用所有情況下,3.3V IPC總線接口都使用低電壓光電耦合器來隔離電流信號。在最少元件配置中,使用三個高速光電耦合器隔離CLK,SDA_in和SDA_out線路信號。

本文討論了對要求隔離I2C總線接口的應用與光電耦合器傳播延遲時間有關的參數(shù)怎樣影響數(shù)據完整性和系統(tǒng)可靠性,包括IEEE 802.3af標準兼容的以太網在線供電交換機和模數(shù)轉換器到微控制器的接口。我們在實例中使用安捷倫HCPL-063L雙通道和HCPL-06OL單通道15 MBd 3.3V光電耦合器。

PC總線基礎知識

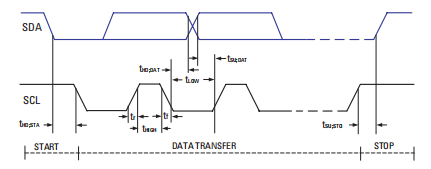

12C總線是飛利浦半導體開發(fā)的一種串行數(shù)字信號通信協(xié)議。它在接口端口中只要求兩條導線和極少的硬件,互連的設備通過軟件尋址。主設備和從設備之間的數(shù)據速率范圍為標準模式下的100 kbps到快速模式下的400 kbps到高速模式下的3.4 Mbps。兩條導線分別承載SDA數(shù)據和SCL時鐘,SDA的每個數(shù)據位在每個SCL時鐘的高電平時上讀取。在此期間,數(shù)據必須保持穩(wěn)定。只有在SCL線路上的時鐘信號為低時,數(shù)據線才能實行高到低或低到高狀態(tài)轉換(圖1)。

圖1 IC總線時序圖

PC總線中的光電耦合器傳播延遲

應用環(huán)境要求在IC總線接口進行電流隔離,以保證無差錯傳送數(shù)據和安全隔離高壓設備。適當?shù)墓怆婑詈掀骺梢蕴峁┻@種隔離能力。

高速光電耦合器的速率范圍從100千波特(kBd)到50兆波特(MBd),可以用于數(shù)字數(shù)據接口隔離。IC總線接口的相應光電耦合器主要取決于應用的速度和傳播延遲要求。

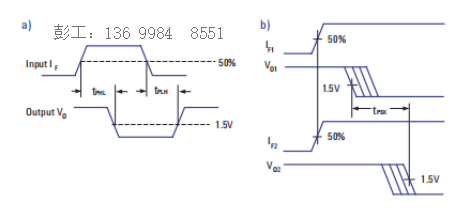

首先,光電耦合器的最大高到低和低到高傳播延遲(TPHL,和tPHL)將決定器件的最大數(shù)據傳輸速率(圖2a)。最大傳播延遲 tP(MAX)以tPHL或tPLH中的高者為準。傳輸NRZ(非歸零)數(shù)據的光電耦合器要求數(shù)據位周期至少要高于(tp(MAX)≥TP(MAx)

因此,最大數(shù)據速率是: FNRz (MAx)=1/t≤1/tP(MAx)

時鐘信號被認為是RZ(歸零)數(shù)據,如IC總線SCL;時鐘周期同時包括高電平時間和低電平時間: t=tHIGH+tLow

對一般50%占空比的RZ時鐘信號,判斷RZ據速率的安全規(guī)則是: fRz(MAx)≤1/2(tp(Mx)

圖2光電耦合器傳播延遲和偏差

但是,在PC總線時鐘周期中,允許高電平時間短于低電平時間。要使光電耦合器傳送占空比小于50%的信號,光電耦合器的最大傳播延遲t(MAX)應小于高電平時間: tHIGH≥tP(MAX)

例如,在考慮隔離400 kHz快速模式時鐘頻率和50%占空比的IC總線時(相當于數(shù)據速率為800 kBd),光電耦合器的最大傳播延遲不能超過1.25 us。由于I2C總線規(guī)范允許快速模式時鐘高電平時間最短為0.6 us,因此光電耦合器的最大傳播延遲tp(MAx) 必須短于0.6 us,而不是1.25us。

在高速光電耦合器中,脈寬失真(PWD)參數(shù)是tPHL和 tPLH之差。一般來說,PWD值在最小數(shù)據脈寬的20%-30%之間是容許的。

在并行數(shù)據信號同時傳輸多通線路時,光電耦合器的傳播延遲偏差tpsx是一個重要系數(shù),它決定著最大并行數(shù)據傳輸速率。如果并行數(shù)據通過兩個單獨的光電耦合器或通過一個多通道光電耦合器傳送,那么通道之間的傳播延遲差異將導致數(shù)據以不同的時間到達光電耦合器的輸出。如果這種傳播延遲差足夠大,那么它將限制可以通過光電耦合器傳輸并行數(shù)據的最大速率。

如圖2b所示,傳播延遲偏差定義為在相同條件下(即相同驅動電流、供電電壓、輸出負荷和工作溫度)對任何光電耦合器通道組,tpLH和/或tPHL最小和最大傳播延遲之差。光電耦合器的tpsx將在數(shù)據線路和信號線路中導致不確定性。一般來說,可以傳輸通過并行光電耦合器的絕對最小數(shù)據脈寬是t.s的兩倍。保守設計應使用略長的脈寬,保證電路中其它地方引起的任何額外不確定性不會導致問題。l2C總線時鐘信號高電平時間是最短的脈沖,因此兩倍的光電耦合器傳播延遲偏差不應超過I2℃時鐘的高電平時間。

PC總線協(xié)議對SCL和SDA信號電平敏感:SDA應在SCL高電平時間中穩(wěn)定在高電平或低電平。l2C總線器件必須在內部提供一個數(shù)據保持時間 tHD:oAT,以過渡在SCL信號下降沿時的高電平和低電平的不確定期。由于光電耦合器將在SDA信號和SCL信號中產生不確定性,數(shù)據保持時間t;DAT應設置成大于tsx。SDA 數(shù)據建立時間tsupAr中也應考慮tpsx的值。

PC總線協(xié)議還要求連接到總線上的發(fā)送器件的輸出電路必須是漏電極-開路或集電極-開路,以執(zhí)行連線邏輯與功能。安捷倫HCPL-O63L光電耦合器擁有一個集電極–開路輸出。根據其技術參數(shù), t-MAx)是90 ns,這表明了其傳輸高速數(shù)據的能力最大傳播延遲偏差tsK最低是40 ns,它將提供足夠的時間允許PC總線設置數(shù)據保持時間/建立時間。

隔離以太網供電中的熱插拔控制器

新興行業(yè)標準IEEE 802.3af可以通過以太網電纜傳輸電力。這一網絡的結構承接IEEE 802.3以太網絡,但在電纜中通過一對備用線或信號線對來傳載-48 VDc電力,為IP電話、網絡像機和無線局域網接入點等被供電設備(PDs)供電。供電設備(PSE)用來在以太網交換機或集線器上提供-48 VDC電源。

從以太網鏈接路段看,802.3af標準PSE可以連接在兩個位置。中間方式連接在現(xiàn)有以太網交換機外部實現(xiàn)PSE技術,終端方式(或終點/DTE PSE)則連接在交換機內部實現(xiàn)PSE。到目前為止,大部分廠商選擇了中間方式PSE,但也有一些廠商在交換機中集成了終端方式PSE。

PSE不僅把電力分配到以太網絡中,它還提供了功率管理功能。功率管理功能搜索鏈路段,看是否存在PD,對PD的額定功率分類,然后在檢測到PD時為鏈路供電,監(jiān)測鏈路段上的電流,在PD斷開連接或不再要求電源時從鏈路段中去掉電力。

在PSE和PD設備中802.3af規(guī)范要求電氣隔離,這與10/10OBASE-T以太網的物理層(PHY)要求相一致。如前所述,PSE熱插拔控制器采用縣-48V電源,這個電源連接到LAN數(shù)據電纜的備用線對或信號線對上。熱插拔控制器與主控制電路之間要求電氣隔離。

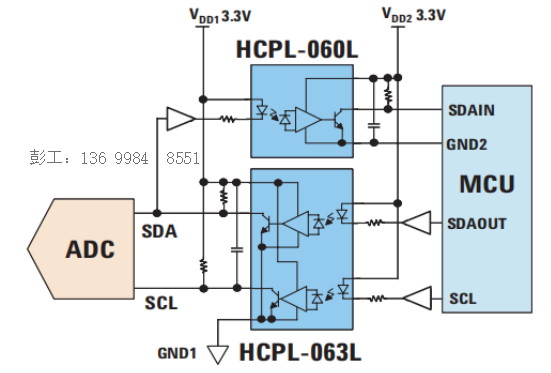

如圖3所示,PSE熱插拔控制器或電源管理芯片利用PC總線協(xié)議來與主機微控制器通信。在本例中,兩個HCPL-063L雙通道3.3V光電耦合器隔離熱插拔控制器芯片和主機微控制器之間的IPC總線接口。其中一個HCPL-O63L的兩條通道把時鐘和SDA_IN數(shù)據從主控制器╱主器件傳送到熱控制器/從器件,另一個HCPL-063L的一條通道把SDA_OUT數(shù)據從從器件反向傳送到主器件。第二條通道可以接口額外的功能,如端口請求/中斷信號。LED輸入電阻器采用保守設計,要求提供的輸入電流大于5 mA閾值電流。我們推薦采用小于200的電阻器,把LED驅動電流限制在大于7.5 mA。在主控制器和熱插拔控制器之間兩個3.3 V電源必須相互隔離。

圖3: POE交換機800 PSE中光電耦合器隔離的12c總線

安捷倫HCPL-O63L隔離電壓達到3750 Vrmg/1分鐘(根據UL1577測試),使得以太網供電交換機能夠滿足電信設備安全標準,如lEC 60950。HCPL-O63L的15kV/us抗共模瞬變能力將防止來自電源熱插拔電路的瞬時電壓噪聲擾亂主控制器一側的電路。

圖4模數(shù)轉換中光電耦合器隔離的PC總線

模數(shù)轉換器РC接口(圖4)

工業(yè)和醫(yī)療儀器可能要求在混合信號和數(shù)字電路之間實現(xiàn)光學隔離。如果醫(yī)療儀器傳感器/探頭接觸到高電壓,那么在模擬傳感器和微控制器/數(shù)字信號處理器之間需要安全電氣絕緣。大多數(shù)電氣隔離的目的是斷開數(shù)字電路和模擬電路之間的任何接地環(huán)路,因為未隔離的接地可能會在系統(tǒng)中導致很高的背景噪聲,影響模數(shù)轉換精度。

I2C總線在模數(shù)轉換器芯片和微控制器之間提供了一個方便的接口。市場上已經能找到內部包含F(xiàn)C接口的模數(shù)轉換器。

一個雙通道光電耦合器(如HCPL-063L)可以隔離從MCU/主器件到ADC/從器件的時鐘和SDAout傳輸,一個單通道光電耦合器(如HCPL-O6OL)把 SDAin、從ADC/從器件傳輸?shù)組CU/主器件上。隔離的DC/DC轉換器可以從數(shù)字系統(tǒng)中導出電源,為模數(shù)轉換器和兩個光電耦合器另一側的Vdd1-GND1供電。

總之,在設計光學隔離I2C總線并行的時鐘和數(shù)據信號時,要求考慮到光電耦合器傳播延遲和偏差性能。具有開路–集電極輸出的光電耦合器可以簡便地直接連接到IP℃總線線路上。光電耦合器本身固有的光學耦合和電氣隔離區(qū)間可以實現(xiàn)的極高的抗電磁干擾能力,幫助保證設備可靠性及能夠滿足EMI標準。

審核編輯:湯梓紅

-

控制器

+關注

關注

112文章

16214瀏覽量

177482 -

PC總線

+關注

關注

0文章

8瀏覽量

8960 -

IC總線

+關注

關注

0文章

8瀏覽量

7211

發(fā)布評論請先 登錄

相關推薦

設計新知:低成本隔離式3.3V到5V DC/DC轉換器的分立設計

隔離式3.3V轉5V轉換器的分立設計

關于AD中PCB信號完整性分析供電網絡設置

如何確保PCB設計信號完整性

信號完整性與電源完整性的相關資料分享

詳解信號完整性與電源完整性

低成本隔離式3.3V到5V DC/DC轉換器的分立設計

低成本隔離式3.3V到5VDC/DC轉換器的分立設計

確保光學隔離的3.3V IC總線中的數(shù)據完整性

確保光學隔離的3.3V IC總線中的數(shù)據完整性

評論