為啥又看反相器呢,因為想做PLL,鎖相環里有PD,PD里面有鎖存器,鎖存器里有NAND,而NAND里又是基于反相器。所以嘍。

反相器,是數字電路中的基本器件。

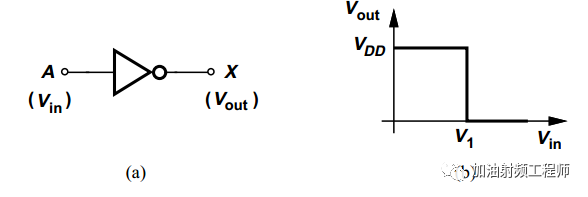

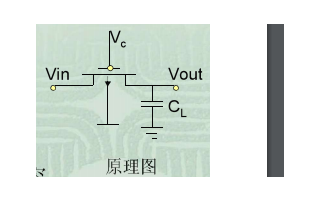

上圖是理想的反相器。

當Vin=0時,Vout=VDD;

當Vin=VDD時,Vout=0;

Vout在VDD和0之間跳變。

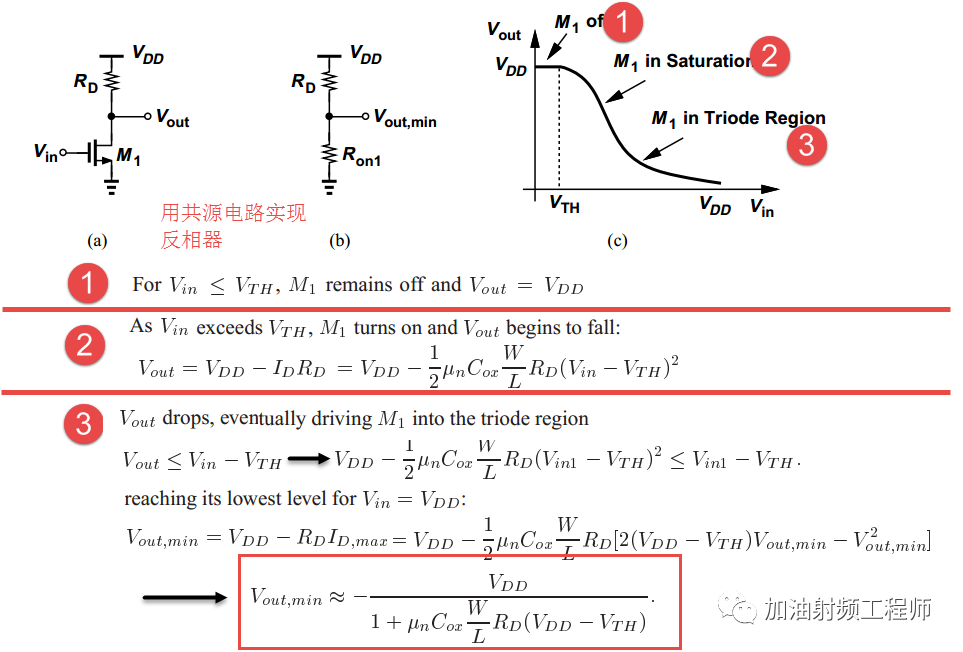

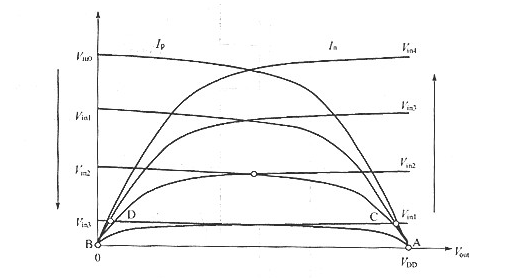

但實際中,不可能實現跳變,即Vin在V1附件一個非常微小的變化,使得Vout從VDD變為0,則表示電路的電壓增益在此時是無限大的;但實際上,電路增益一直是個有限的值,所以實際電路中,Vout只會從VDD漸變至低,至于低電平是多少電壓,則取決于設計。

可以看到,輸出的低電壓與W/L和RD相關,因為分母中的式子不可能為無窮大,所以輸出的低電平只能接近于0,但是到不了0。

雖然用共源電路可以實現反相器的基本性能,但是它確不常用,為什么呢?

因為它具有三個致命的缺陷:

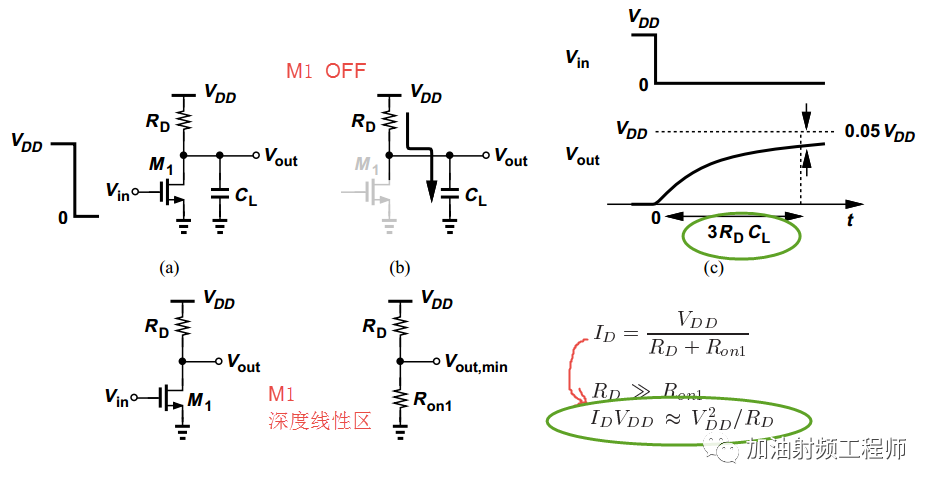

(1) RD的值,必須遠大于晶體管所呈現出來的電阻Ron. 因為當想要輸出低電平時,Vout=Ron*VDD/(RD+Ron),所以為了使得低電平足夠低,則要求RD>>Ron

(2) 因為RD的存在,使得反相器的速度和功耗不能兼得。如下圖,可以看到,當想提高速度時,則需要降低RD,但是此時功耗又上升。

(3) 如果反相器輸出為低電平時,反相器的功耗為 VDD*VDD/RD

這三點中,最要命的是第三點。

在大型數字電路中,有一個靜態功耗,就是指電路不動作時的功耗,而NMOS反相器(共源電路實現的反相器)的靜態功耗為VDD*VDD/RD。

比如說,一個大型數字芯片,有1百萬個門電路,其中有一般是處于低電平輸出狀態,假設VDD=1.8V,RD=10kohm,則靜態功耗高達 162W,這個顯然不能接受。

而這三點缺點,則主要是與上拉電阻RD有關。

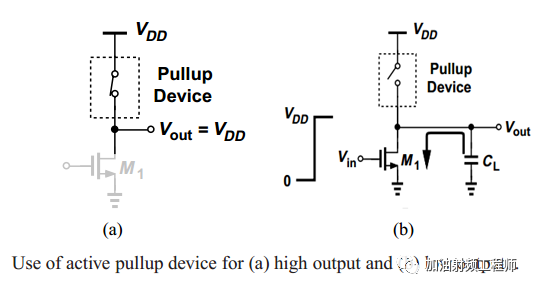

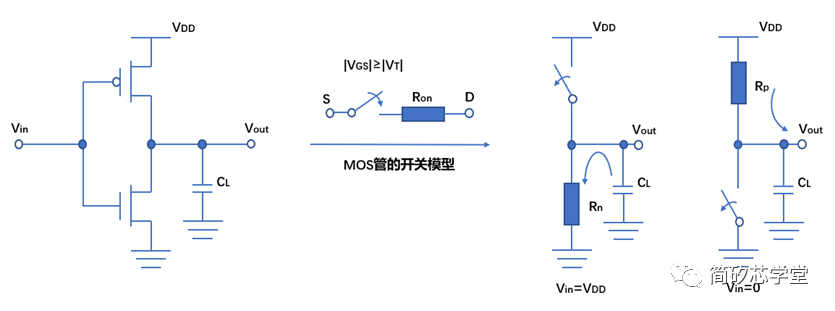

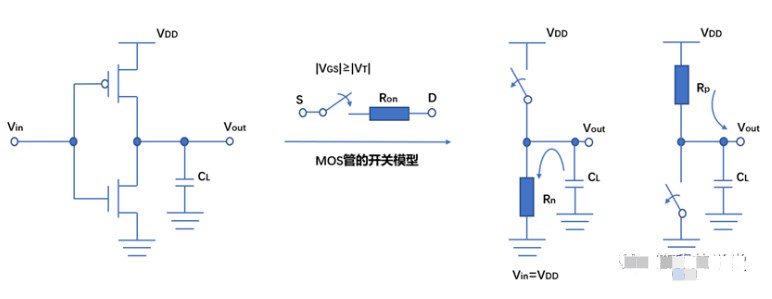

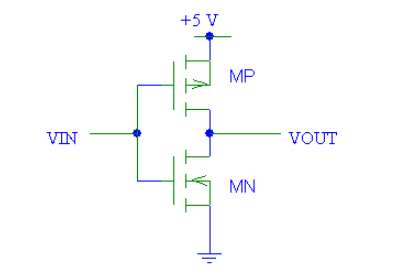

所以,如果能找到這樣一個器件,當M1關斷時,該器件將輸出與VDD相連,最好該器件的電阻很低;而當M1打開時,該器件關斷,這樣就沒有電流從VDD流向地。即如下圖所示。

那什么器件能擔當此重任呢?

那就是PMOS。

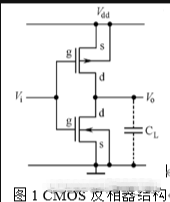

把PMOS和CMOS合體,形成的反相器,稱之為CMOS反相器。

CMOS反相器的輸出低電平基本為0,因為當Vin=VDD時,M2關斷。而NMOS的低電平永遠都不可能為0。

CMOS在高電平輸出和低電平輸出的狀態下,靜態功耗都為0,;而NMOS在低電平輸出狀態下,有靜態功耗。

審核編輯:湯梓紅

-

CMOS

+關注

關注

58文章

5621瀏覽量

234503 -

NMOS

+關注

關注

3文章

283瀏覽量

34107 -

反相器

+關注

關注

6文章

308瀏覽量

43049

原文標題:為啥CMOS反相器要優于NMOS反相器呢?

文章出處:【微信號:加油射頻工程師,微信公眾號:加油射頻工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

為啥CMOS反相器要優于NMOS反相器呢?

為啥CMOS反相器要優于NMOS反相器呢?

評論