EDA 覆蓋電子系統(tǒng)設(shè)計(jì)的全環(huán)節(jié)

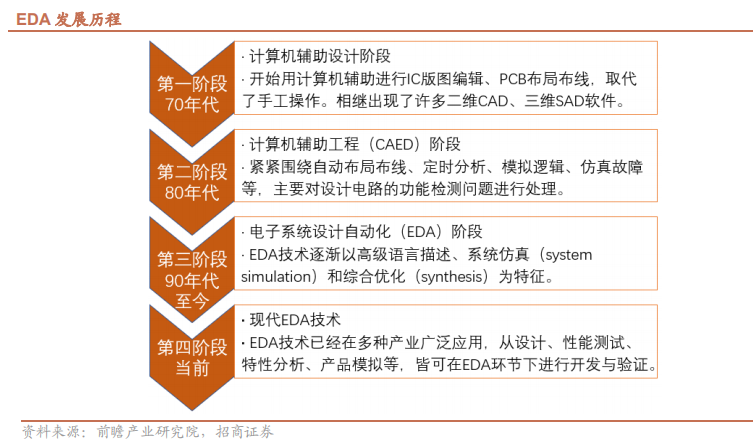

電子設(shè)計(jì)自動(dòng)化(Electronic Design Automation,EDA)技術(shù)是指包括電路系統(tǒng)設(shè)計(jì)、系統(tǒng)仿真、設(shè)計(jì)綜合、PCB版圖設(shè)計(jì)和制版的一整套自動(dòng)化流程。隨著計(jì)算機(jī)、集成電路和電子設(shè)計(jì)技術(shù)的高速發(fā)展,EDA 技術(shù)歷經(jīng)計(jì)算機(jī)輔助設(shè)計(jì)(CAD)、計(jì)算機(jī)輔助制造(CAM)、計(jì)算機(jī)輔助制造(CAM)、計(jì)算機(jī)輔助測試(CAT)和計(jì)算機(jī)輔助工程設(shè)計(jì)(CAE)等發(fā)展歷程,已經(jīng)成為電子信息產(chǎn)業(yè)的支柱產(chǎn)業(yè)。

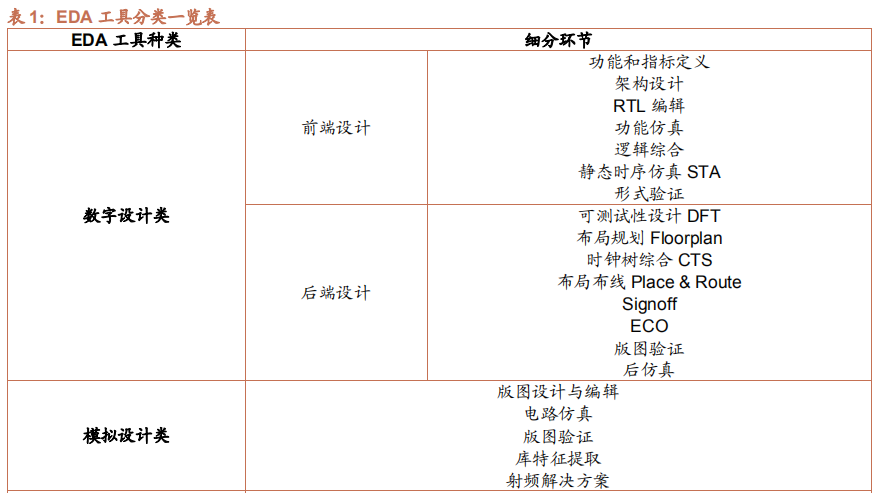

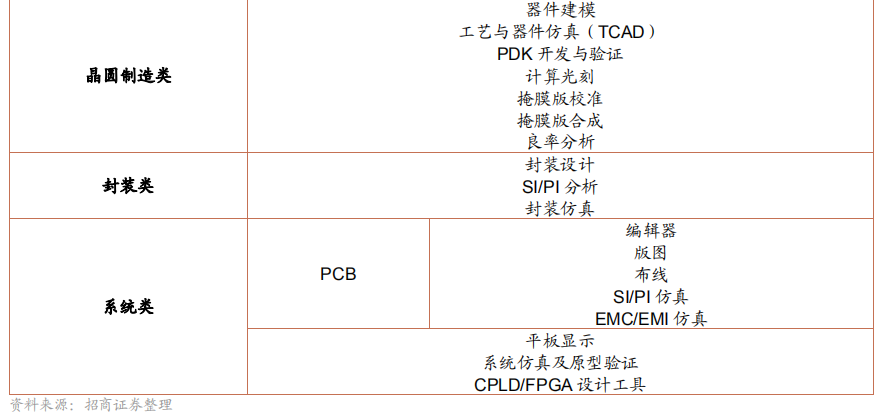

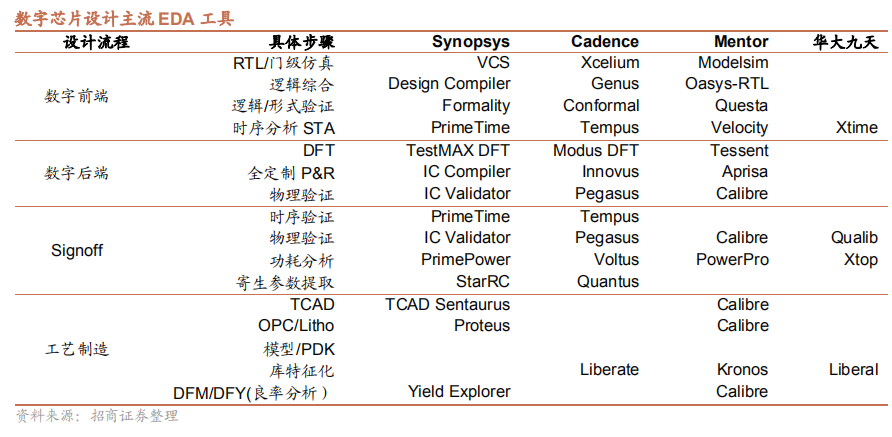

EDA 產(chǎn)品線繁多,根據(jù) EDA 工具的應(yīng)用場景不同,可以將 EDA 工具分為數(shù)字設(shè)計(jì)類、模擬設(shè)計(jì)類、晶圓制造類、封裝類、系統(tǒng)類等五大類,其中系統(tǒng)類又可以細(xì)分為 PCB、平板顯示設(shè)計(jì)工具、系統(tǒng)仿真及原型驗(yàn)證和 CPLD/FPGA設(shè)計(jì)工具等。

數(shù)字設(shè)計(jì)類工具主要是面向數(shù)字芯片設(shè)計(jì)的工具,是一系列流程化點(diǎn)工具的集合,包括功能和指標(biāo)定義、架構(gòu)設(shè)計(jì)、RTL 編輯、功能仿真、邏輯綜合、靜態(tài)時(shí)序仿真(Static Timing Analysis,STA)、形式驗(yàn)證等工具。

模擬設(shè)計(jì)類工具主要面向模擬芯片的設(shè)計(jì)工具,包括版圖設(shè)計(jì)與編輯、電路仿真、版圖驗(yàn)證、庫特征提取、射頻設(shè)計(jì)解決方案等產(chǎn)品線。

晶圓制造類工具主要是面向晶圓廠/代工廠的設(shè)計(jì)工具,該類工具主要是協(xié)助晶圓廠開發(fā)工藝并且實(shí)現(xiàn)器件建模和仿真等功能,同時(shí)也是生成 PDK 的重要工具,而 PDK 又是作為晶圓廠和設(shè)計(jì)廠商的重要橋梁的作用,因此可見 EDA工具和工藝綁定緊密,并且隨著摩爾定律的推進(jìn)需不斷升級(jí)迭代。晶圓制造類工具包括器件建模、工藝和器件仿真(TCAD)、PDK 開發(fā)與驗(yàn)證、計(jì)算光刻、掩膜版校準(zhǔn)、掩膜版合成和良率分析等。

封裝類工具主要是面向芯片封裝環(huán)節(jié)的設(shè)計(jì)、仿真、驗(yàn)證工具,包括封裝設(shè)計(jì)、封裝仿真以及 SI/PI(信號(hào)完整性/電源完整性)分析。隨著芯片先進(jìn)封裝技術(shù)發(fā)展以及摩爾定律往前推進(jìn),封裝形式走向高密度、高集成及微小化,因此對于封裝的要求和難度有較大提高,目前高性能產(chǎn)品需要先進(jìn)的集成電路封裝,如將多芯片的異質(zhì)集成封裝方式、基于硅片的高密度先進(jìn)封裝(HDAP)、FOWLP、2.5/3DIC、SiP 和 CoWoS 等。

在系統(tǒng)類 EDA 領(lǐng)域,EDA 工具可分為 PCB 設(shè)計(jì)、平板顯示設(shè)計(jì)、系統(tǒng)仿真工具(Emulation)、CPLD/FPGA 等可編程器件上的電子系統(tǒng)設(shè)計(jì)。EDA 工程的范疇不斷擴(kuò)展到下游電子系統(tǒng)應(yīng)用,如果沒有 EDA 技術(shù)的支持,想完成先進(jìn)的電子系統(tǒng)設(shè)計(jì)機(jī)會(huì)是不可能的,反過來,生產(chǎn)制造技術(shù)的不斷進(jìn)步又必將會(huì)對 EDA 技術(shù)提出新的要求。

在系統(tǒng)類 EDA 中,印刷電路板(PCB)主要用作電子系統(tǒng)的載體,工程師通常將集成電路元器件焊接在 PCB 上完成整個(gè)電子系統(tǒng)的搭建、控制、通信等功能。目前主流的 PCB 工具有 Cadence 的 Allegro、Mentor Graphics 的 Xpedition及 Zuken 的 CR 等,國產(chǎn) PCB 廠商有立創(chuàng) EDA 等。

平板顯示設(shè)計(jì)主要應(yīng)用于面板的研發(fā)、生產(chǎn)和制造,國內(nèi) EDA 公司華大九天已經(jīng)具備在平板顯示領(lǐng)域全流程的工具,并且基本覆蓋國內(nèi)主要的面板廠商客戶。

系統(tǒng)仿真工具(Emulation),與傳統(tǒng)的仿真工具(Simulation)不同,主要聚焦于系統(tǒng)級(jí)別的仿真,廣泛應(yīng)用于加速軟硬件聯(lián)合開發(fā)的場景,而傳統(tǒng)仿真更多聚焦于單一功能或者局部電路環(huán)節(jié)的仿真。西門子(Siemens)曾推出PAVE360 自動(dòng)駕駛硅前驗(yàn)證環(huán)境(pre-silicon autonomous validation environment),該產(chǎn)品主要意圖在于支持和促進(jìn)創(chuàng)新自動(dòng)駕駛汽車平臺(tái)的研發(fā)。PAVE360 為下一代汽車芯片的研發(fā)提供了一個(gè)跨汽車生態(tài)系統(tǒng)、多供應(yīng)商協(xié)作的綜合環(huán)境,該系統(tǒng)不僅可以實(shí)現(xiàn)汽車硬軟件子系統(tǒng)、整車模型、傳感器數(shù)據(jù)融合、交通流量的仿真,甚至還仿真自動(dòng)駕駛汽車最終在智能城市里面的駕駛。目前 EDA 三大巨頭都在布局系統(tǒng)仿真工具,主流產(chǎn)品包括 Synopsys 的 Zebu、Cadence 的 Palladium 和 Simens EDA 的 Veloce。

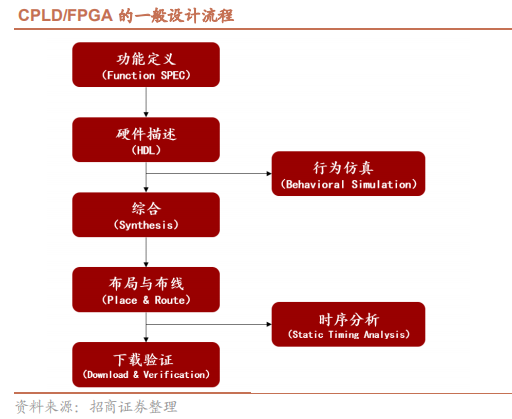

復(fù)雜可編程邏輯器件(Complex Programmable Logic Device,CPLD)和現(xiàn)場可編程陣列(Field Programmable Gates Array,F(xiàn)PGA)最顯著的優(yōu)勢在于開發(fā)周期短、投資風(fēng)險(xiǎn)小、產(chǎn)品上市快和硬件升級(jí)余地大等。這兩類芯片是比較特殊的芯片類型,需要與 EDA 工具協(xié)同才能工作,一般而言開發(fā) CPLD/FPGA 的廠商都需要開發(fā)一套成熟的EDA 下載和驗(yàn)證工具來實(shí)現(xiàn)對芯片的編程。從 CPLD/FPGA 的簡要設(shè)計(jì)流程可以看出,對工程師而言,其工序相對于傳統(tǒng)芯片設(shè)計(jì)流程有明顯減少。目前比較主流的可編程器件的 EDA 集成開發(fā)工具主要有 Altera 公司的 MAX+Plus和 Quartus、Xinlinx 公司的 Foundation 和 ISE,Lattice 公司的 ispDesignExpert 和 ispLever,Synopsys 的Synplify 以及 Cadence 的 Precision。

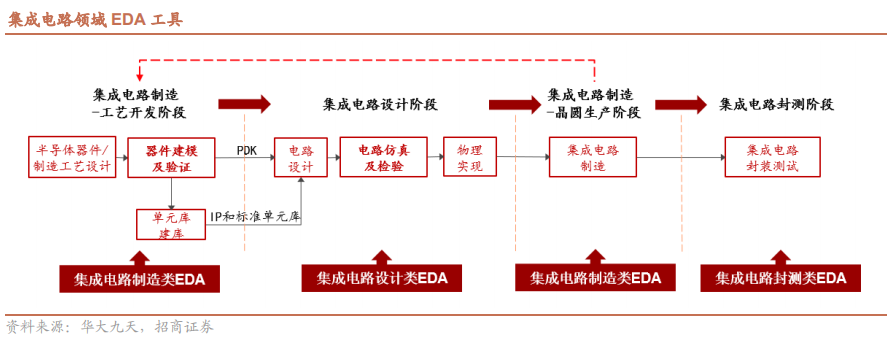

按照集成電路產(chǎn)業(yè)鏈劃分,集成電路 EDA 工具可以分為制造類 EDA 工具、設(shè)計(jì)類 EDA 工具及封測類 EDA 工具。器件建模及仿真類工具就屬于制造類 EDA 工具,晶圓廠(包括晶圓代工廠、IDM 制造部門等)借助器件建模及仿真、良率分析等制造類 EDA 工具來協(xié)助其工藝平臺(tái)開發(fā),工藝平臺(tái)開發(fā)階段主要由晶圓廠主導(dǎo)完成,在其完成半導(dǎo)體器件和制造工藝的設(shè)計(jì)后,建立半導(dǎo)體器件的模型并通過 PDK 或建立 IP 和標(biāo)準(zhǔn)單元庫等方式提供給集成電路設(shè)計(jì)企業(yè)(包括芯片設(shè)計(jì)公司、半導(dǎo)體 IP 公司、IDM 設(shè)計(jì)部門等)。

設(shè)計(jì)類 EDA 工具則是基于晶圓廠或代工廠提供的 PDK或 IP 及標(biāo)準(zhǔn)單元庫為芯片設(shè)計(jì)廠商提供設(shè)計(jì)服務(wù),芯片設(shè)計(jì)廠商采用設(shè)計(jì)類 EDA 工具完成芯片的設(shè)計(jì)。封裝類 EDA工具主要是提供封裝方案設(shè)計(jì)及仿真的功能,從而幫助芯片設(shè)計(jì)企業(yè)完成一顆芯片的全生命周期的設(shè)計(jì)服務(wù)。

數(shù)字設(shè)計(jì) EDA 的核心環(huán)節(jié)是邏輯綜合和布局布線

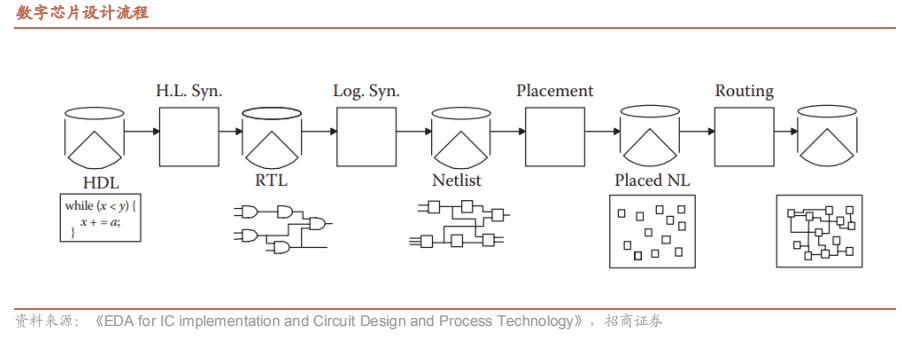

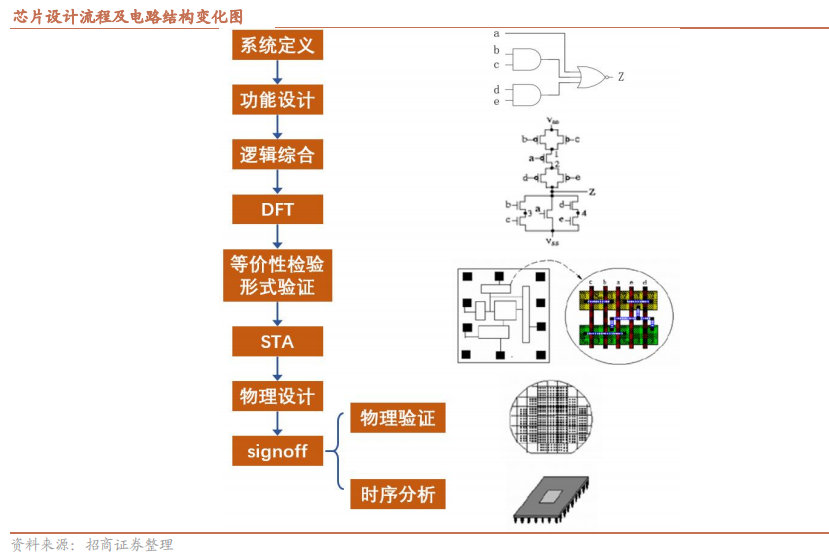

數(shù)字芯片設(shè)計(jì)多采用自頂向下設(shè)計(jì)方式,可以分為五大步驟:1)系統(tǒng)的行為級(jí)設(shè)計(jì),確定芯片的功能、性能指標(biāo)(包括芯片面積、成本等),2)結(jié)構(gòu)設(shè)計(jì),根據(jù)芯片的特點(diǎn),將其劃分為多個(gè)接口清晰、功能相對獨(dú)立的子模塊,3)邏輯設(shè)計(jì),采用規(guī)則結(jié)構(gòu)來實(shí)現(xiàn),或者利用已驗(yàn)證的邏輯單元,4)電路級(jí)設(shè)計(jì),得到可靠的電路圖,5)將電路圖轉(zhuǎn)換為物理版圖。

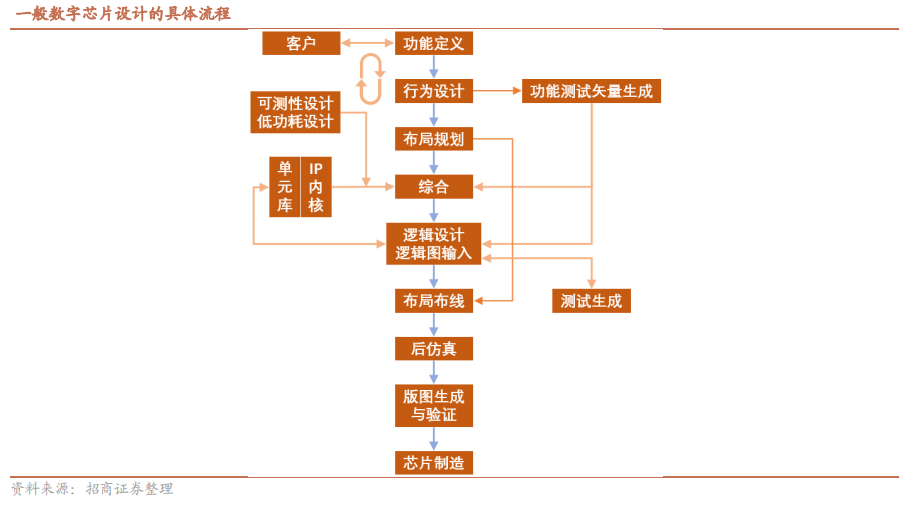

1、系統(tǒng)功能描述:確定芯片規(guī)格并做好總體設(shè)計(jì)方案,是最高層次的抽象描述,包括系統(tǒng)功能、性能、物理尺寸、設(shè)計(jì)模式、制造工藝等,功能設(shè)計(jì)主要是為了確定系統(tǒng)功能的實(shí)現(xiàn)方案,通常是給出系統(tǒng)的時(shí)序圖及各子模塊之間的數(shù)據(jù)流圖,該部分工作主要是客戶向芯片設(shè)計(jì)廠商(Fabless,無晶圓設(shè)計(jì)公司)提出的設(shè)計(jì)要求。

2、邏輯設(shè)計(jì):將系統(tǒng)功能結(jié)構(gòu)化,通常是以 RTL(寄存器傳輸級(jí))代碼(VHDL、Verilog、System Verilog 等硬件描述語句)、原理圖、邏輯圖等表示設(shè)計(jì)結(jié)果,完成相關(guān)設(shè)計(jì)規(guī)范的代碼編寫,并保證代碼的可綜合、可讀性,同時(shí)還需要考慮相關(guān)模塊的復(fù)用性。

3、邏輯綜合:將邏輯設(shè)計(jì)中的電路表達(dá)語句轉(zhuǎn)換為電路實(shí)現(xiàn),使用芯片制造商提供的標(biāo)準(zhǔn)電路單元加上時(shí)間約束(Timing Constraints)等條件,盡可能少的元件和連線完成從 RTL 電路描述映射到綜合庫單元,得到一個(gè)在面積和時(shí)序上滿足需求的門級(jí)網(wǎng)表。邏輯綜合步驟是芯片前端設(shè)計(jì)中的核心環(huán)節(jié),關(guān)系到整個(gè)芯片的 PPA 水平。

4、物理設(shè)計(jì)/布局布線:在邏輯綜合后,基本是只有邏輯和時(shí)序約束的設(shè)計(jì)結(jié)果,而物理設(shè)計(jì)/布局布線則是讓電路設(shè)計(jì)更貼近真實(shí)狀況,即加入物理約束(Physical Constraints),從而使得電路成為一個(gè)真實(shí)能夠在芯片制造商能夠生產(chǎn)的芯片。綜合后的網(wǎng)表和時(shí)序約束文件導(dǎo)入該環(huán)節(jié)工具中,進(jìn)行布局布線,利用相關(guān)提取軟件進(jìn)行寄生參數(shù)提取,并重新反饋到物理實(shí)現(xiàn)的布局布線軟件中,再次進(jìn)行時(shí)序計(jì)算和重新優(yōu)化,直到滿足時(shí)序和功耗要求為止。

5、后仿真/物理驗(yàn)證:布局布線出來的結(jié)果是經(jīng)過多層次的優(yōu)化后的電路,為了保證該電路與最開始系統(tǒng)功能描述的電路功能一致,就需要進(jìn)行后仿真/設(shè)計(jì)驗(yàn)證,主要包括設(shè)計(jì)規(guī)則檢查(DRC)、電路版圖對照檢查(LVS)、電氣規(guī)則檢查(ERC)、寄生參數(shù)提取等。

驗(yàn)證工作貫穿整個(gè)設(shè)計(jì)過程。從芯片設(shè)計(jì)角度看,以物理實(shí)現(xiàn)為分界,芯片設(shè)計(jì)可以劃分為前端(邏輯設(shè)計(jì))與后端(物理設(shè)計(jì)),其實(shí)現(xiàn)過程中將不斷對設(shè)計(jì)進(jìn)行優(yōu)化,優(yōu)化可能改變邏輯描述方式和結(jié)構(gòu),存在引入錯(cuò)誤的風(fēng)險(xiǎn),所以驗(yàn)證貫穿整個(gè)設(shè)計(jì)過程,在每個(gè)環(huán)節(jié)都反復(fù)確保邏輯優(yōu)化過程不改變功能、時(shí)序滿足目標(biāo)需求、物理規(guī)則無違規(guī)等等,因此產(chǎn)生大量的驗(yàn)證流程和工作,更涉及多方共同協(xié)作。

前端設(shè)計(jì)主要考慮邏輯和功能層面,后端設(shè)計(jì)主要目的是物理參數(shù)約束的優(yōu)化。簡單而言,前端設(shè)計(jì)更多的是邏輯/功能層面的實(shí)現(xiàn),實(shí)現(xiàn)方式是以基礎(chǔ)的邏輯單元進(jìn)行連接設(shè)計(jì),以實(shí)現(xiàn)系統(tǒng)需要的邏輯功能,前端設(shè)計(jì)一般沒有過多考慮物理參數(shù)的約束,比如電路間走線的長度帶來的延時(shí)等因素,僅僅考慮了單元器件的電氣物理參數(shù)。而后端設(shè)計(jì)則是重點(diǎn)加入了物理約束,比如某些特定電路模塊的擺放位置,以及電路間連線的物理參數(shù)也會(huì)被考量在軟件優(yōu)化中,因此后端設(shè)計(jì)后的電路更接近于滿足需求的實(shí)際電路。

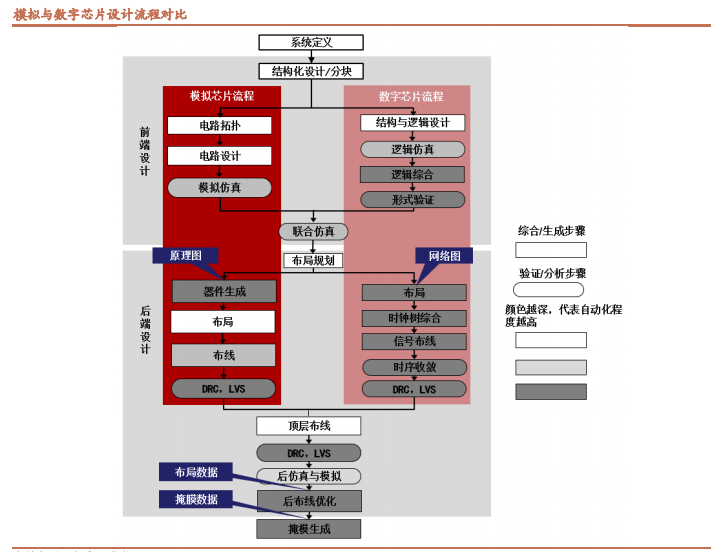

模擬和數(shù)字芯片設(shè)計(jì)流程對比方面,模擬芯片設(shè)計(jì)的自動(dòng)化程度低于數(shù)字芯片設(shè)計(jì)。借用數(shù)字芯片設(shè)計(jì)的概念,模擬芯片設(shè)計(jì)也可以分為前后端,前端設(shè)計(jì)包括電路圖設(shè)計(jì)及生成,涉及大量的算法、計(jì)算以及假設(shè)驗(yàn)證等,從自動(dòng)化程度看,數(shù)字芯片在前端設(shè)計(jì)的自動(dòng)化程度明顯高于模擬芯片,主要是模擬芯片需要工程師手動(dòng)選型電路拓?fù)洳⑶疫x擇合適的元器件。后端設(shè)計(jì)方面,數(shù)字電路的后端設(shè)計(jì)基本實(shí)現(xiàn)了全自動(dòng)化,EDA 工具的性能直接影響到芯片產(chǎn)品的性能,模擬芯片后端設(shè)計(jì)的自動(dòng)化程度較低,尤其在布局步驟方面。

后摩爾時(shí)代技術(shù)演進(jìn)驅(qū)動(dòng)EDA技術(shù)應(yīng)用延伸拓展。后摩爾時(shí)代的集成電路技術(shù)演進(jìn)方向主要包括延續(xù)摩爾定律(More Moore)、擴(kuò)展摩爾定律(More than Moore)以及超越摩爾定律(Beyond Moore)三類,主要發(fā)展目標(biāo)涵蓋了建立在摩爾定律基礎(chǔ)上的生產(chǎn)工藝特征尺寸的進(jìn)一步微縮、以增加系統(tǒng)集成的多重功能為目標(biāo)的芯片功能多樣化發(fā)展,以及通過三維封裝(3D Package)、系統(tǒng)級(jí)封裝(SiP)等方式實(shí)現(xiàn)器件功能的融合和產(chǎn)品的多樣化。其中,面向延續(xù)摩爾定律(More Moore)方向,單芯片的集成規(guī)模呈現(xiàn)爆發(fā)性增長,為 EDA 工具的設(shè)計(jì)效率提出了更高的要求。

面向擴(kuò)展摩爾定律(More than Moore)方向,伴隨邏輯、模擬、存儲(chǔ)等功能被疊加到同一芯片,EDA 工具需具備對復(fù)雜功能設(shè)計(jì)的更強(qiáng)支撐能力。面向超越摩爾定律方向,新工藝、新材料、新器件等的應(yīng)用要求 EDA 工具的發(fā)展在仿真、驗(yàn)證等關(guān)鍵環(huán)節(jié)實(shí)現(xiàn)方法學(xué)的創(chuàng)新。

審核編輯:郭婷

-

pcb

+關(guān)注

關(guān)注

4318文章

23022瀏覽量

396424 -

計(jì)算機(jī)

+關(guān)注

關(guān)注

19文章

7430瀏覽量

87733 -

eda

+關(guān)注

關(guān)注

71文章

2712瀏覽量

172937

原文標(biāo)題:EDA電子設(shè)計(jì)產(chǎn)業(yè)基礎(chǔ)知識(shí)

文章出處:【微信號(hào):AI_Architect,微信公眾號(hào):智能計(jì)算芯世界】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評(píng)論請先 登錄

相關(guān)推薦

電氣與電子系統(tǒng)實(shí)驗(yàn)指導(dǎo)書

電子系統(tǒng)設(shè)計(jì)基本知識(shí)

電子系統(tǒng)仿真與MATLAB

ModelSim 電子系統(tǒng)分析及仿真

基于EDA技術(shù)的FPGA該怎么設(shè)計(jì)?

基于EDA技術(shù)的FPGA該怎么設(shè)計(jì)?

基于EDA技術(shù)的FPGA設(shè)計(jì)計(jì)算機(jī)有哪些應(yīng)用?

為什么需要調(diào)試一個(gè)電子系統(tǒng)

數(shù)字電子系統(tǒng)的EDA設(shè)計(jì)方法研究

現(xiàn)代電子系統(tǒng)中電源技術(shù)的發(fā)展和應(yīng)用

覆蓋電子系統(tǒng)設(shè)計(jì)全環(huán)節(jié)的EDA技術(shù)的基礎(chǔ)知識(shí)

覆蓋電子系統(tǒng)設(shè)計(jì)全環(huán)節(jié)的EDA技術(shù)的基礎(chǔ)知識(shí)

評(píng)論