布局

在設(shè)計(jì)中,布局是一個(gè)重要的環(huán)節(jié)。布局結(jié)果的好壞將直接影響布線的效果,因此可以這樣認(rèn)為,合理的布局是PCB設(shè)計(jì)成功的第一步。

尤其是預(yù)布局,是思考整個(gè)電路板,信號(hào)流向、散熱、結(jié)構(gòu)等架構(gòu)的過程。如果預(yù)布局是失敗的,后面的再多努力也是白費(fèi)。

1、考慮整體

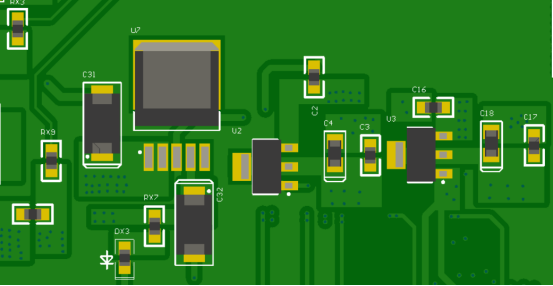

一個(gè)產(chǎn)品的成功與否,一是要注重內(nèi)在質(zhì)量,二是兼顧整體的美觀,兩者都較完美才能認(rèn)為該產(chǎn)品是成功的。

在一個(gè)PCB板上,元件的布局要求要均衡,疏密有序,不能頭重腳輕或一頭沉。

PCB是否會(huì)有變形?

是否預(yù)留工藝邊?

是否預(yù)留MARK點(diǎn)?

是否需要拼板?

多少層板,可以保證阻抗控制、信號(hào)屏蔽、信號(hào)完整性、經(jīng)濟(jì)性、可實(shí)現(xiàn)性?

2、排除低級(jí)錯(cuò)誤

印制板尺寸是否與加工圖紙尺寸相符?能否符合PCB制造工藝要求?有無定位標(biāo)記?

元件在二維、三維空間上有無沖突?

元件布局是否疏密有序,排列整齊?是否全部布完?

需經(jīng)常更換的元件能否方便地更換?插件板插入設(shè)備是否方便?

熱敏元件與發(fā)熱元件之間是否有適當(dāng)?shù)木嚯x?

調(diào)整可調(diào)元件是否方便?

在需要散熱的地方,裝了散熱器沒有?空氣流是否通暢?

信號(hào)流程是否順暢且互連最短?

插頭、插座等與機(jī)械設(shè)計(jì)是否矛盾?

線路的干擾問題是否有所考慮?

3、旁路或去耦電容

在布線時(shí),模擬器件和數(shù)字器件都需要這些類型的電容,都需要靠近其電源引腳連接一個(gè)旁路電容,此電容值通常為 0.1μF。引腳盡量短,減小走線的感抗,且要盡量靠近器件。

在電路板上加旁路或去耦電容,以及這些電容在板上的布置,對(duì)于數(shù)字和模擬設(shè)計(jì)來說都屬于基本常識(shí),但其功能卻是有區(qū)別的。

在模擬布線設(shè)計(jì)中旁路電容通常用于旁路電源上的高頻信號(hào),如果不加旁路電容,這些高頻信號(hào)可能通過電源引腳進(jìn)入敏感的模擬芯片。一般來說,這些高頻信號(hào) 的頻率超出 模擬器件抑制高頻信號(hào)的能力。

如果在模擬電路中不使用旁路電容的話,就可能在信號(hào)路徑 上引入噪聲,更嚴(yán)重的情況甚至?xí)鹫駝?dòng)。而對(duì)于控制器和處理器這樣的數(shù)字器件 來說,同樣需要去耦電容,但原因不同。

這些電容的一個(gè)功能是用作“微型”電荷庫,這是因?yàn)樵?a href="http://www.nxhydt.com/v/tag/8791/" target="_blank">數(shù)字電路中,執(zhí)行門狀態(tài)的切換(即開關(guān)切換)通常需要很大的電流,當(dāng)開關(guān)時(shí)芯片上產(chǎn)生開關(guān)瞬態(tài)電流并流經(jīng)電路板,有這額外的 “備用”電荷是有利的。

如果執(zhí)行開關(guān)動(dòng)作時(shí)沒有足夠的電荷,會(huì)造成電源電壓發(fā)生很大變化。電壓變化太大,會(huì)導(dǎo)致數(shù)字信號(hào)電平進(jìn)入不確定狀態(tài),并很可能引起數(shù)字器件中的狀態(tài)機(jī)錯(cuò)誤運(yùn)行。

流經(jīng)電路板走線的開關(guān)電流將引起電壓發(fā)生變化,由于電路板走線 存在寄生電感,則可采用如下公式計(jì)算電壓的變化:

V=Ldl/dt

其中V=電壓的變化,L=電路板走線感抗,dI=流經(jīng)走線的電流變化,dt=電流變化的時(shí)間。

因此,基于多種原因,在供電電源處或有源器件的電源引腳處施加旁路(或去耦)電容是 非常好的做法。

4、輸入電源如果電流比較大,建議減少走線長(zhǎng)度和面積,不要滿場(chǎng)跑

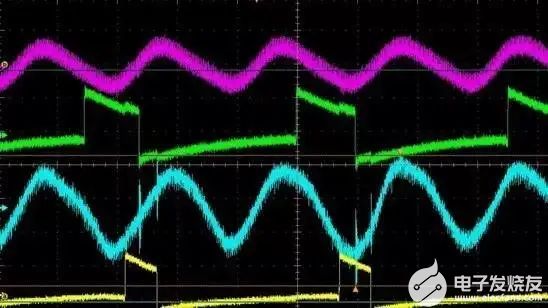

輸入上的開關(guān)噪聲耦合到了電源輸出的平面。輸出電源的MOS管的開關(guān)噪聲影響了前級(jí)的輸入電源。

如果電路板上存在大量大電流DCDC,則有不同頻率,大電流高電壓跳變干擾。

所以我們需要減小輸入電源的面積,滿足通流就可以。所以在電源布局的時(shí)候,要考慮避免輸入電源滿板跑。

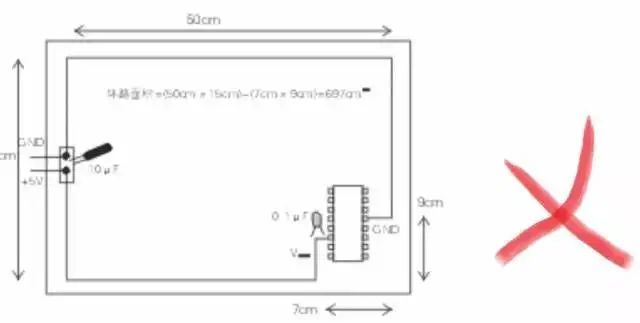

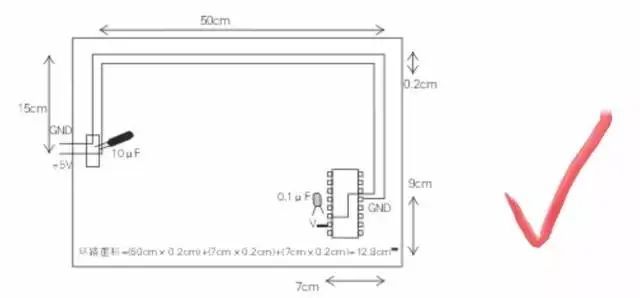

電源線和地線的位置良好配合,可以降低電磁干擾(EMl)的可能性。如果電源線和地線配合不當(dāng),會(huì)設(shè)計(jì)出系統(tǒng)環(huán)路,并很可能會(huì)產(chǎn)生噪聲。

電源線和地線配合不當(dāng)?shù)腜CB 設(shè)計(jì)示例如圖所示。在此電路板上,使用不同的路線來布電源線和地線,由于這種不恰當(dāng)?shù)呐浜希娐钒宓?a target="_blank">電子元器件和線路受電磁干擾 (EMI)的可能性比較大。

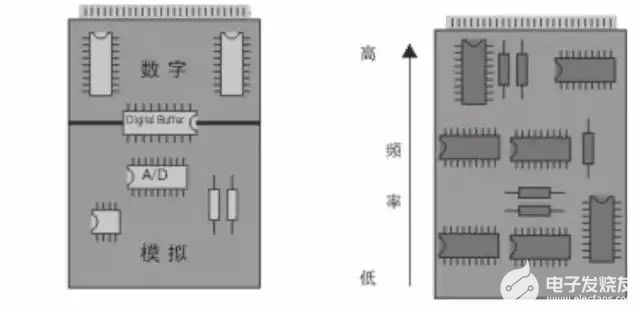

5、數(shù)模分離

在每個(gè) PCB 設(shè)計(jì)中,電路的噪聲部分和“安靜”部分(非噪聲部分)要分隔開。

一般來說,數(shù)字電路可以容忍噪聲干擾,而且對(duì)噪聲不敏感(因?yàn)閿?shù)字電 路有較大的電壓噪聲容限);相反,模擬電路的電壓噪聲容限就小得多。兩者之中,模擬電路對(duì)開關(guān)噪聲最為敏感。在混合信號(hào)系統(tǒng)的布線中,這兩種電路要分隔開。

在布局過程中,需要考慮散熱風(fēng)道,散熱死角;熱敏感器件不要放在熱源風(fēng)后面。

優(yōu)先考慮DDR這樣散熱困難戶的布局位置。避免由于熱仿真不通過,導(dǎo)致反復(fù)調(diào)整。

布線

在PCB設(shè)計(jì)中,布線是完成產(chǎn)品設(shè)計(jì)的重要步驟,可以說前面的準(zhǔn)備工作都是為它而做的,在整個(gè)PCB中,以布線的設(shè)計(jì)過程限定最高,技巧最細(xì)、工作量最大。

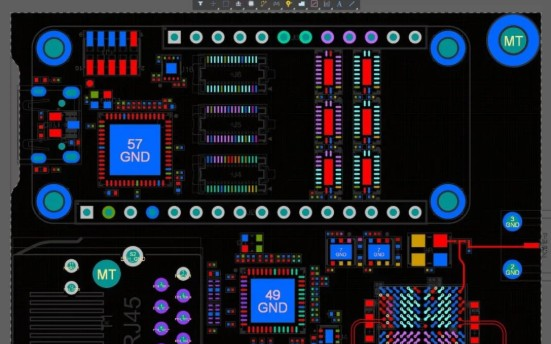

PCB布線有單面布線、雙面布線及多層布線。布線的方式也有兩種:自動(dòng)布線及交互式布線,在自動(dòng)布線之前, 可以用交互式預(yù)先對(duì)要求比較嚴(yán)格的線進(jìn)行布線,輸入端與輸出端的邊線應(yīng)避免相鄰平行,以免產(chǎn)生反射干擾。必要時(shí)應(yīng)加地線隔離,兩相鄰層的布線要互相垂直,平行容易產(chǎn)生寄生耦合。

自動(dòng)布線的布通率,依賴于良好的布局,布線規(guī)則可以預(yù)先設(shè)定, 包括走線的彎曲次數(shù)、導(dǎo)通孔的數(shù)目、步進(jìn)的數(shù)目等。一般先進(jìn)行探索式布經(jīng)線,快速地把短線連通,然后進(jìn)行迷宮式布線,先把要布的連線進(jìn)行全局的布線路徑優(yōu)化,它可以根據(jù)需要斷開已布的線。并試著重新再布線,以改進(jìn)總體效果。

對(duì)目前高密度的PCB設(shè)計(jì)已感覺到貫通孔不太適應(yīng)了, 它浪費(fèi)了許多寶貴的布線通道,為解決這一矛盾,出現(xiàn)了盲孔和埋孔技術(shù),它不僅完成了導(dǎo)通孔的作用,還省出許多布線通道使布線過程完成得更加方便,更加流暢,更為完善,PCB 板的設(shè)計(jì)過程是一個(gè)復(fù)雜而又簡(jiǎn)單的過程,要想很好地掌握它,還需廣大電子工程設(shè)計(jì)人員去自已體會(huì),才能得到其中的真諦。

1、電源、地線的處理

既使在整個(gè)PCB板中的布線完成得都很好,但由于電源、 地線的考慮不周到而引起的干擾,會(huì)使產(chǎn)品的性能下降,有時(shí)甚至影響到產(chǎn)品的成功率。所以對(duì)電、地線的布線要認(rèn)真對(duì)待,把電、地線所產(chǎn)生的噪音干擾降到最低限度,以保證產(chǎn)品的質(zhì)量。

對(duì)每個(gè)從事電子產(chǎn)品設(shè)計(jì)的工程人員來說都明白地線與電源線之間噪音所產(chǎn)生的原因, 現(xiàn)只對(duì)降低式抑制噪音作以表述:

眾所周知的是在電源、地線之間加上去耦電容。

盡量加寬電源、地線寬度,最好是地線比電源線寬,它們的關(guān)系是:地線>電源線>信號(hào)線,通常信號(hào)線寬為:0.2~0.3mm,最經(jīng)細(xì)寬度可達(dá)0.05~0.07mm,電源線為1.2~2.5 mm

對(duì)數(shù)字電路的PCB可用寬的地導(dǎo)線組成一個(gè)回路, 即構(gòu)成一個(gè)地網(wǎng)來使用(模擬電路的地不能這樣使用)

用大面積銅層作地線用,在印制板上把沒被用上的地方都與地相連接作為地線用。或是做成多層板,電源,地線各占用一層。

2、數(shù)字電路與模擬電路的共地處理

現(xiàn)在有許多PCB不再是單一功能電路(數(shù)字或模擬電路),而是由數(shù)字電路和模擬電路混合構(gòu)成的。因此在布線時(shí)就需要考慮它們之間互相干擾問題,特別是地線上的噪音干擾。

數(shù)字電路的頻率高,模擬電路的敏感度強(qiáng),對(duì)信號(hào)線來說,高頻的信號(hào)線盡可能遠(yuǎn)離敏感的模擬電路器件,對(duì)地線來說,整人PCB對(duì)外界只有一個(gè)結(jié)點(diǎn),所以必須在PCB內(nèi)部進(jìn)行處理數(shù)、模共地的問題,而在板內(nèi)部數(shù)字地和模擬地實(shí)際上是分開的它們之間互不相連,只是在PCB與外界連接的接口處(如插頭等)。

數(shù)字地與模擬地有一點(diǎn)短接,請(qǐng)注意,只有一個(gè)連接點(diǎn)。也有在PCB上不共地的,這由系統(tǒng)設(shè)計(jì)來決定。

3、信號(hào)線布在電(地)層上

在多層印制板布線時(shí),由于在信號(hào)線層沒有布完的線剩下已經(jīng)不多,再多加層數(shù)就會(huì)造成浪費(fèi)也會(huì)給生產(chǎn)增加一定的工作量,成本也相應(yīng)增加了,為解決這個(gè)矛盾,可以考慮在電(地)層上進(jìn)行布線。

首先應(yīng)考慮用電源層,其次才是地層。因?yàn)樽詈檬潜A舻貙拥耐暾浴?/p>

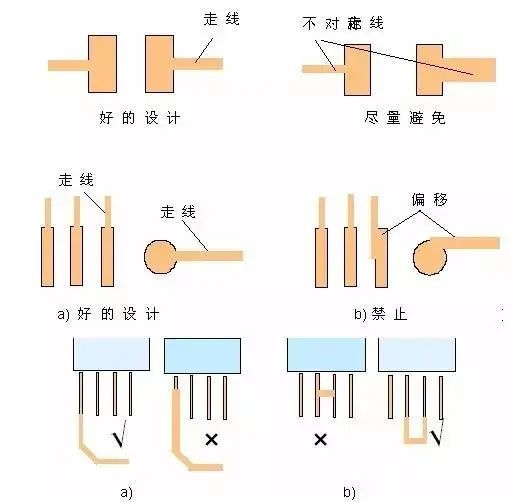

4、大面積導(dǎo)體中連接腿的處理

在大面積的接地(電)中,常用元器件的腿與其連接,對(duì)連接腿的處理需要進(jìn)行綜合的考慮,就電氣性能而言,元件腿的焊盤與銅面滿接為好,但對(duì)元件的焊接裝配就存在一些不良隱患如:

焊接需要大功率加熱器。

容易造成虛焊點(diǎn)。所以兼顧電氣性能與工藝需要,做成十字花焊盤,稱之為熱隔離(heat shield)俗稱熱焊盤(Thermal),

這樣,可使在焊接時(shí)因截面過分散熱而產(chǎn)生虛焊點(diǎn)的可能性大大減少。多層板的接電(地)層腿的處理相同。

5、布線中網(wǎng)絡(luò)系統(tǒng)的作用

在許多CAD系統(tǒng)中,布線是依據(jù)網(wǎng)絡(luò)系統(tǒng)決定的。網(wǎng)格過密,通路雖然有所增加,但步進(jìn)太小,圖場(chǎng)的數(shù)據(jù)量過大,這必然對(duì)設(shè)備的存貯空間有更高的要求,同時(shí)也對(duì)象計(jì)算機(jī)類電子產(chǎn)品的運(yùn)算速度有極大的影響。

而有些通路是無效的,如被元件腿的焊盤占用的或被安裝孔、定們孔所占用的等。網(wǎng)格過疏,通路太少對(duì)布通率的影響極大。所以要有一個(gè)疏密合理的網(wǎng)格系統(tǒng)來支持布線的進(jìn)行。

標(biāo)準(zhǔn)元器件兩腿之間的距離為0.1英寸(2.54mm),所以網(wǎng)格系統(tǒng)的基礎(chǔ)一般就定為0.1英寸(2.54 mm)或小于0.1英寸的整倍數(shù),如:0.05英寸、0.025英寸、0.02英寸等。

6、設(shè)計(jì)規(guī)則檢查(DRC)

布線設(shè)計(jì)完成后,需認(rèn)真檢查布線設(shè)計(jì)是否符合設(shè)計(jì)者所制定的規(guī)則,同時(shí)也需確認(rèn)所制定的規(guī)則是否符合印制板生產(chǎn)工藝的需求,一般檢查有如下幾個(gè)方面:

線與線,線與元件焊盤,線與貫通孔,元件焊盤與貫通孔,貫通孔與貫通孔之間的距離是否合理,是否滿足生產(chǎn)要求。

電源線和地線的寬度是否合適,電源與地線之間是否緊耦合(低的波阻抗)?在PCB中是否還有能讓地線加寬的地方。

對(duì)于關(guān)鍵的信號(hào)線是否采取了最佳措施,如長(zhǎng)度最短,加保護(hù)線,輸入線及輸出線被明顯地分開。

模擬電路和數(shù)字電路部分,是否有各自獨(dú)立的地線。

后加在PCB中的圖形(如圖標(biāo)、注標(biāo))是否會(huì)造成信號(hào)短路。

對(duì)一些不理想的線形進(jìn)行修改。

在PCB上是否加有工藝線?阻焊是否符合生產(chǎn)工藝的要求,阻焊尺寸是否合適,字符標(biāo)志是否壓在器件焊盤上,以免影響電裝質(zhì)量。

多層板中的電源地層的外框邊緣是否縮小,如電源地層的銅箔露出板外容易造成短路。

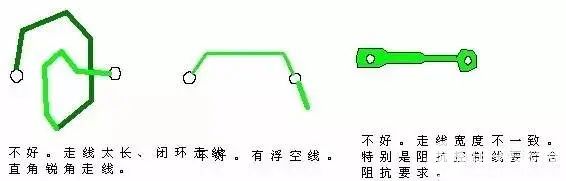

7、檢查是否有銳角、阻抗不連續(xù)點(diǎn)等

1)對(duì)于高頻電流來說,當(dāng)導(dǎo)線的拐彎處呈現(xiàn)直角甚至銳角時(shí),在靠近彎角的部位,磁通密度及電場(chǎng)強(qiáng)度都比較高,會(huì)輻射較強(qiáng)的電磁波,而且此處的電感量會(huì)比較大,感抗便也比鈍角或圓角要大一些。

2)對(duì)于數(shù)字電路的總線布線來說,布線拐彎呈現(xiàn)鈍角或圓角,布線所占的面積比較小。在相同的線間距條件下,總的線間距所占的寬度要比直角拐彎的少0.3倍。

8、檢查3W、3H原則

1)時(shí)鐘、復(fù)位、100M以上信號(hào)以及一些關(guān)鍵的總線信號(hào)等與其他信號(hào)線布線必須滿足3W原則,同層和相鄰層無較長(zhǎng)平行走線,且鏈路上過孔盡量少。

2)高速信號(hào)的過孔數(shù)量問題,有些器件指導(dǎo)書上一般對(duì)高速信號(hào)的過孔數(shù)量要求比較嚴(yán)格,咨詢互連的原則的是除了必須的管腳fanout過孔外,嚴(yán)禁在內(nèi)層打多余的過孔,他們布過8G的PCIE 3.0的走線,也打過4個(gè)過孔,沒有問題。

3)同層時(shí)鐘及高速信號(hào)中心距需嚴(yán)格滿足3H(H為走線層到回流平面間距);相鄰層的信號(hào)嚴(yán)禁重疊,建議也滿足3H的原則,關(guān)于上述的串?dāng)_問題,有工具可以檢查的。

布線約束

布線約束:層分布

RF PCB的每層都大面積輔地,沒有電源平面,RF布線層的上下相鄰兩層都應(yīng)該是地平面。即使是數(shù)模混合板,數(shù)字部分可以存在電源平面,但RF區(qū)域仍然要滿足每層都大面積輔地的要求。

RF單板的層疊結(jié)構(gòu)

布線約束:基本要求

1)走線要求盡量最短,不走閉環(huán),不走銳角直角,線的寬度一致,沒有浮空線。

2)差分信號(hào)線一般都是走的高速信號(hào),其要滿足阻抗的對(duì)稱性,差分線不能交叉走線,線長(zhǎng)相差不能超過100mil,差分線之間和單個(gè)差分線到地之間都要滿足阻抗要求。差分走線過孔不能超過4個(gè),差分線對(duì)間的間距滿足3W規(guī)則。

3)一般晶振、pll濾波器件、模擬處理信號(hào)處理芯片、電感、變壓器下禁止走時(shí)鐘線、控制線、電磁敏感線。

4)模擬信號(hào)與數(shù)字信號(hào),電源線與控制信號(hào)線,弱信號(hào)與其他任何信號(hào)都不能并排走線,應(yīng)該分層(最好有地隔離)或相距較遠(yuǎn)走線。如果分層相鄰層的線與線之間要交叉走線,不能并行走線。為了減少線間串?dāng)_,應(yīng)保證線間距足夠大,當(dāng)線中心間距不少于3倍線寬時(shí),則可保持70%的電場(chǎng)不互相干擾,稱為3W規(guī)則。如要達(dá)到98%的電場(chǎng)不互相干擾,可使用10W的間距。(注:時(shí)鐘布線的時(shí)候,一定要注意和數(shù)據(jù)線、控制信號(hào)線的有效隔離,距離越遠(yuǎn)越好,盡可能不要布在同層。)

5)強(qiáng)輻射信號(hào)線(高頻、高速,尤以時(shí)鐘線為甚)不要靠近接口、拉手條等以防對(duì)外輻射。

6)敏感信號(hào)(主要指:弱信號(hào)、復(fù)位信號(hào)、比較器的輸入信號(hào)、AD的參考電源、鎖相環(huán)濾波信號(hào)、芯片內(nèi)部的PLL電路的濾波部分。)布線應(yīng)該盡可能短,不靠近強(qiáng)輻射信號(hào),不放在板的邊緣,離外金屬框架15mm以上。長(zhǎng)距離走線時(shí)可以包地(應(yīng)注意包地可能會(huì)引起阻抗變化)、內(nèi)層走線。另外,對(duì)于ESD較弱的芯片的走線,建議內(nèi)層走線,可以減弱芯片損壞的概率。

布線約束:電源

1)注意電源退耦、濾波,防止不同單元通過電源線產(chǎn)生干擾,電源布線時(shí)電源線之間應(yīng)相互隔離。電源線與其它強(qiáng)干擾線(如CLK)用地線隔離。

2)小信號(hào)放大器的電源布線需要地銅皮及接地過孔隔離,避免其它EMI干擾竄入,進(jìn)而惡化本級(jí)信號(hào)質(zhì)量。

3)不同電源層在空間上要避免重疊。主要是為了減少不同電源之間的干擾,特別是一些電壓相差很大的電源之間,電源平面的重疊問題一定要設(shè)法避免,難以避免時(shí)可考慮中間隔地層。

布線約束:電源過流能力

1)電源部分導(dǎo)線印制線在層間轉(zhuǎn)接的過孔數(shù)符合通過電流的要求(1A/Ф0.3mm 孔)

2)PCB的POWER部分的銅箔尺寸符合其流過的最大電流,并考慮余量(一般參考為1A/mm線寬)

布線約束:接地方法

1)接地線要短而直,減少分布電感,減小公共地阻抗所產(chǎn)生的干擾。

調(diào)整各組內(nèi)濾波電容方向,縮小地回路。如圖所示的三個(gè)濾波電容,接地偏向于相關(guān)的RF 器件方向,尤其是高頻濾波電容。

電容的接地圖

2)RF 主信號(hào)路徑上的接地器件和電源濾波電容需要接地時(shí),為減小器件接地電感,要求就近接地。

3)有些元件的底部是接地的金屬殼,要在元件的投影區(qū)內(nèi)加一些接地孔,投影區(qū)內(nèi)的表面層不得布信號(hào)線和過孔;

4)接地線需要走一定的距離時(shí),應(yīng)加粗走線線寬、縮短走線長(zhǎng)度,禁止接近和超過1/4導(dǎo)引波長(zhǎng),以防止天線效應(yīng)導(dǎo)致信號(hào)輻射;

5)除特殊用途外,不得有孤立銅皮,銅皮上一定要加地線過孔

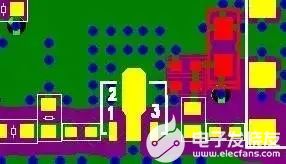

6)對(duì)某些敏感電路、有強(qiáng)烈輻射源的電路分別放在屏蔽腔內(nèi),裝配時(shí)屏蔽腔壓在PCB表面。PCB在設(shè)計(jì)時(shí)要加上“過孔屏蔽墻”,就是在PCB上與屏蔽腔壁緊貼的部位加上接地的過孔。如下圖所示,要有兩排以上的過孔,兩排過孔相互錯(cuò)開,同一排的過孔間距在100mils左右。

布線約束:通用規(guī)則

1)PCB頂層走RF信號(hào),RF信號(hào)下面的平面層必須是完整的接地平面,形成微帶線結(jié)構(gòu)。如圖所示。要保證微帶線的結(jié)構(gòu)完整性,必須做到:同層內(nèi)微帶線要做包地銅皮處理,建議地銅皮邊緣離微帶線邊緣有3H的寬度。H表示介質(zhì)層厚度。在3H范圍內(nèi),不得有其它信號(hào)過孔。禁止RF 信號(hào)走線跨第二層的地平面縫隙。非耦合微帶線間要加地銅皮,并在地銅皮上加地過孔。

微帶線至屏蔽壁距離應(yīng)保持為3H以上。微帶線不得跨第二層地平面的分割線。

微帶線結(jié)構(gòu)圖

2)要求地銅皮到信號(hào)走線間隔≥3H。

3)地銅皮邊緣加地線孔,孔間距約在100mils左右,均勻整齊排列;

4)地線銅皮邊緣要光滑、平整,禁止尖銳毛刺;

5)RF信號(hào)布線周圍如果存在其它RF信號(hào)線,就要在兩者之間輔地銅皮,并在地銅皮上間隔100mils左右加一個(gè)接地過孔,起隔離作用。

6)RF信號(hào)布線周圍如果存在其它不相關(guān)的非RF信號(hào)(如過路電源線),要在兩者間輔地銅皮,并每隔100mils左右加一個(gè)接地過孔。

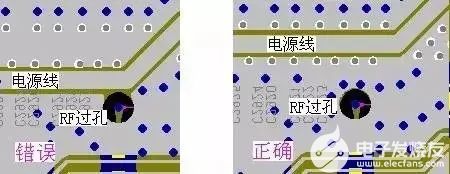

7)RF信號(hào)過孔與內(nèi)層的其它布線靠近,如左圖所示的過路電源線靠近了RF信號(hào)過孔,電源線上的EMI 干擾會(huì)竄入RF布線,所以要采用右圖正確的布線方法,在電源線與RF信號(hào)過孔間輔地并加地過孔,起隔離作用。有時(shí)內(nèi)層的RF信號(hào)線與其它有較強(qiáng)干擾的信號(hào)(如過路電源線)過孔靠近,也采用同樣的方法輔地并加地過孔。

電源線與射頻過孔布線圖

8)器件安裝孔是非金屬化孔時(shí),RF 信號(hào)布線要遠(yuǎn)離器件安裝孔。 需要在RF信號(hào)布線與安裝孔間輔進(jìn)地銅皮,并加接地 過孔。

審核編輯:湯梓紅

-

電路板

+關(guān)注

關(guān)注

140文章

4908瀏覽量

97445 -

PCB

+關(guān)注

關(guān)注

1文章

1777瀏覽量

13204

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

一招搞定PCB布局布線的可制造性設(shè)計(jì)問題

PCB畫板沒有捷徑可走,短短3個(gè)月讓我被老板重用

PCB布局和走線的調(diào)整

解開多年疑惑,原來PCB層疊竟有這些講究!

PCB布局布線的可制造性設(shè)計(jì),薦讀!

開關(guān)電源的PCB設(shè)計(jì)(布局、排版、走線)規(guī)范

開關(guān)電源的PCB設(shè)計(jì)(布局、排版、走線)規(guī)范

如何快速變成PCB大神

PCB走線元器件擺放之美

車規(guī)電容,基美車規(guī)電容的特點(diǎn)和優(yōu)勢(shì)有哪些?

基美車規(guī)電容的特點(diǎn)及優(yōu)勢(shì)

MOS原來還有這些使用技巧

基美(KEMET)車規(guī)電容在電動(dòng)汽車領(lǐng)域應(yīng)用

KEMET(基美)|PCB布局的秘密,原來還有這些“捷徑”可走

KEMET(基美)|PCB布局的秘密,原來還有這些“捷徑”可走

評(píng)論