VHDL、Verilog和SystemVerilog的比較

簡介

各種硬件描述語言 (HDL) 在過去幾年中不斷增強,確定哪種語言適合哪種設計的復雜性也隨之增加。許多設計人員和組織正在考慮是否應該從一種 HDL 切換到另一種HDL。

本文比較了三種通用 HDL 的技術特性:

VHDL (IEEE-Std 1076):一種由多種驗證和綜合(實現)工具支持的通用數字設計語言。

Verilog (IEEE-Std 1364):一種通用數字設計語言,支持多種驗證和綜合工具。

SystemVerilog:Verilog 的增強版本。

語言的“感覺”

每個 HDL 都有自己的風格和特點。以下描述提供了每種語言的整體“感覺”。文章末尾的表格提供了更詳細的功能比較。

VHDL

VHDL 是一種強類型且類型豐富的語言。源自 Ada 編程語言,其語言要求比 Verilog 更冗長。額外的冗長旨在使設計自我記錄(所謂的更嚴謹)。此外,強類型需要額外的編碼才能從一種數據類型顯式轉換為另一種數據類型。

VHDL 的創建者強調明確的語義和易于從一種工具移植到另一種工具的設計。因此,作為語言和工具實現的產物,競爭條件不是 VHDL 用戶關心的問題。

已經開發了幾個相關的標準來增加語言的實用性。今天的 VHDL 設計都依賴于 IEEE-Std 1164(std_logic 類型),并且許多還依賴于標準的 Numeric 和 Math 包。相關標準的開發是 VHDL 作者的另一個目標:即產生一種通用語言并允許開發可重用的包以涵蓋語言中未內置的功能。

VHDL 沒有在語言中定義任何仿真控制或監視功能。這些功能取決于工具。

由于缺乏語言定義的仿真控制命令以及 VHDL 的用戶定義類型功能,VHDL 社區通常依賴交互式 GUI 環境來調試設計問題。

Verilog

Verilog 是一種弱類型和有限類型的語言。它的傳統可以追溯到 C 編程語言和稱為 Hilo 的舊 HDL。

Verilog 中的所有數據類型都在語言中預定義。Verilog 承認所有數據類型都有位級表示。支持的數據可以在 Verilog 中自由混合。

Verilog 中的仿真語義比 VHDL 中的更加模糊。這種模糊性為設計人員在應用優化方面提供了更大的靈活性, 但如果不遵循編碼準則,它也可能(并且經常會)導致競爭條件 。有可能在不同供應商的工具上甚至在同一供應商工具的不同版本上產生不同結果的設計。

與 VHDL 的創建者不同,Verilog 的作者認為他們為設計人員提供了語言所需的一切。語言的范圍更有限,加上缺乏打包能力,即使不是不可能,也很難開發語言中尚未包含的可重用功能。

Verilog 在語言中定義了一組基本的仿真控制能力(系統任務)。

由于這些預定義的系統任務和缺乏復雜的數據類型,Verilog 用戶經常運行批處理或命令行仿真,并通過查看仿真結果數據庫中的波形來調試設計問題。

SystemVerilog

SystemVerilog 的父級顯然是 Verilog,但該語言還受益于稱為 Superlog 的專有 Verilog 擴展以及 C 和 C++ 編程語言的特點。

SystemVerilog 通過添加豐富的用戶定義類型系統來擴展 Verilog。它還添加了強類型功能,特別是在用戶定義類型領域。但是,VHDL 中類型檢查的強度仍然超過了 SystemVerilog。而且,為了保持向后兼容性,SystemVerilog 為內置的 Verilog 類型保留了弱類型。

由于 SystemVerilog 是一種比 Verilog 更通用的語言,它提供了定義和打包該語言中尚未包含的可重用功能的能力。

SystemVerilog 還增加了針對測試臺開發、基于斷言的驗證以及接口抽象和封裝的功能。

強類型的優點和缺點

強類型的好處是在驗證過程中盡早發現設計中的錯誤。在分析/編譯源代碼的過程中有很多都是強類型發現的問題,在仿真過程中可能會發現更多問題。

強類型的缺點是性能成本。由于工具必須對源代碼進行檢查,因此編譯速度往往較慢。

當啟用運行時檢查時,仿真也會由于檢查開銷而變慢。此外,由于設計人員在編寫代碼時必須編寫類型轉換函數并插入類型轉換或顯式聲明的轉換函數,因此設計人員的工作效率在編寫代碼階段可能會降低。

1,000,000 元的問題是:強類型的好處是否超過成本?

這個問題沒有一個正確答案。一般來說,VHDL 語言設計者想要一種安全的語言,能夠在流程的早期捕獲盡可能多的錯誤。Verilog 語言設計者想要一種設計者可以使用的語言——用來快速編寫模型。SystemVerilog 的設計者正試圖通過在增強領域提供強類型來提供兩全其美,同時不會顯著影響代碼編寫和建模效率。

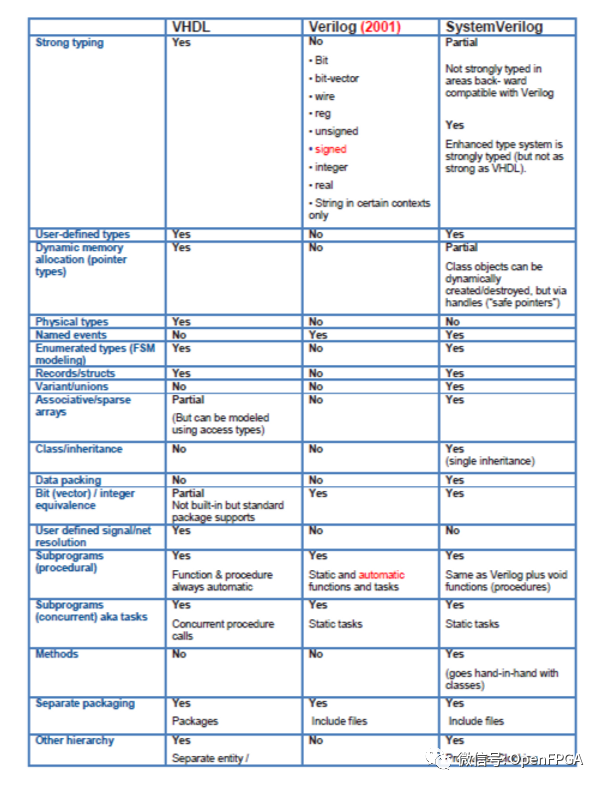

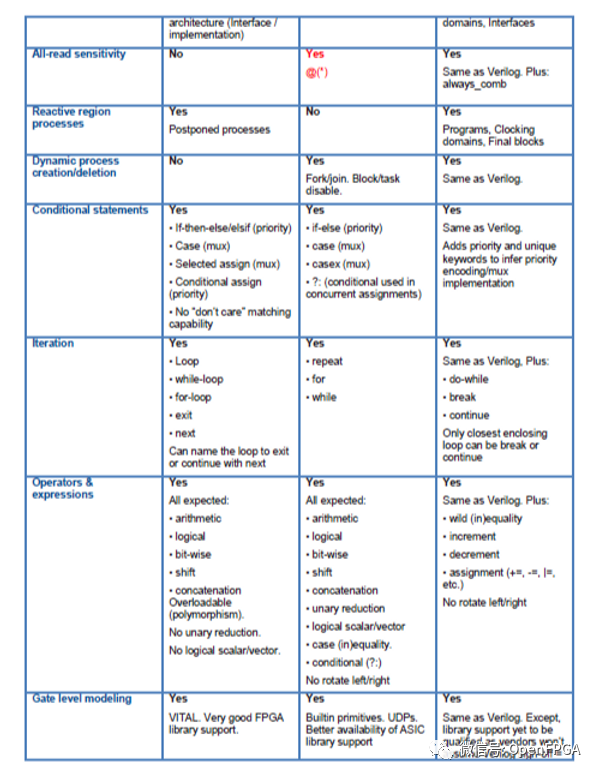

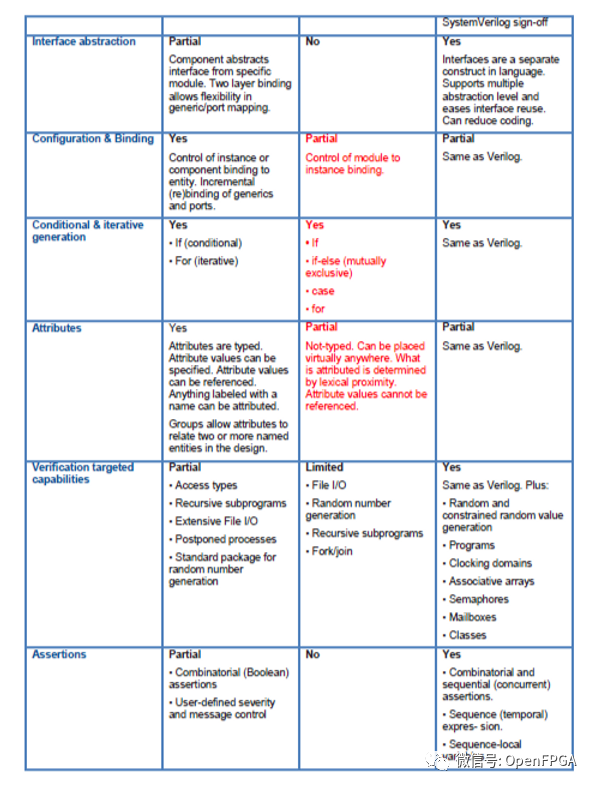

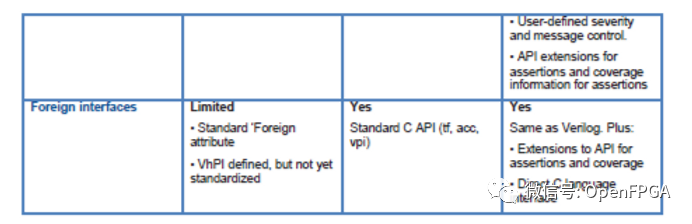

語言特征比較

下表顯示了三種 HDL 的逐個特性比較。請注意,紅色字體將 Verilog 2001 功能與 Verilog 1995 功能區分開來。

總結

除了上面的語言特性比較之外,這里還有一些需要考慮的最后幾點:

SystemVerilog 是一個新興的標準,仍在不斷發展。SystemVerilog 擁有一系列引人注目的功能,是當前 Verilog 用戶可能的遷移路徑。但是目前一些綜合工具支持的還不是支持的特別好~

對于VHDL 用戶,許多SystemVerilog 和Verilog 2001 增強功能已經以VHDL 語言提供。還有一項新的 VHDL 增強工作正在進行中,它將為該語言添加測試平臺和擴展的斷言功能(SystemVerilog 將在這兩個領域提供超過 VHDL 2002 的價值)。考慮到更改流程和工具的成本以及培訓所需的投資,必須非常慎重地考慮是否放棄 VHDL(應該都不會)。

-

硬件

+關注

關注

11文章

3252瀏覽量

66112 -

HDL

+關注

關注

8文章

327瀏覽量

47336 -

仿真控制

+關注

關注

0文章

4瀏覽量

6557

原文標題:VHDL、Verilog和SystemVerilog的比較

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

硬件描述語言(HDL)編碼技術:xilinx verilog語法技巧

寄存器用廠家distributed ram描述是否比"HDL通用寄存器描述...

Verilog HDL入門教程(全集)

基于模型設計的HDL代碼自動生成技術綜述

Verilog HDL綜合實用教程

Verilog HDL華為入門教程

Verilog HDL入門教程

Verilog HDL入門教程之Verilog HDL數字系統設計教程

Verilog HDL入門教程

詳細介紹基于HDL的FPGA開發流程

HDL是什么_HDL語言的特點

Verilog HDL語言技術要點

通用HDL的技術特性

通用HDL的技術特性

評論