在近日于硅谷舉辦的英特爾 On 技術(shù)創(chuàng)新峰會(huì)上,英特爾宣布推出英特爾AgilexD 系列 FPGA 和 SoC,為采用較小外形規(guī)格的中端 FPGA 應(yīng)用帶來(lái)更高性能與更低功耗。最初的英特爾AgilexFPGA 和 SoC 家族一經(jīng)問(wèn)世,便獲得了市場(chǎng)的廣泛認(rèn)可,之后英特爾不懈創(chuàng)新,賦予英特爾AgilexFPGA 架構(gòu)新的特性和不同特點(diǎn),使這一家族適配的應(yīng)用范圍更加廣泛。這些新特性與新功能在支持并發(fā)工作負(fù)載需求方面的重要性日益凸顯。更值得一提的是,眾多中端應(yīng)用既要將功耗限制在一定水平,又要滿足不斷增長(zhǎng)的性能需求,這正是英特爾制程工藝技術(shù)的用武之地。

全新英特爾 Agilex D 系列 FPGA 和 SoC 具備多項(xiàng)新特性,例如升級(jí)版硬核處理器系統(tǒng) (HPS)、采用 AI 張量模塊的增強(qiáng)型數(shù)字信號(hào)處理 (DSP)、MIPI I/O 支持和固核 IP 時(shí)間敏感網(wǎng)絡(luò) (TSN) 控制器;同時(shí),該系列還具備這一家族其他產(chǎn)品擁有的重要特性,包括第二代英特爾 Hyperflex FPGA 架構(gòu)和高速 SerDes 收發(fā)器。上述特性相結(jié)合,使英特爾 Agilex D 系列 FPGA 廣泛適用于各種中端 FPGA 應(yīng)用。

英特爾利用半導(dǎo)體制程工藝上的進(jìn)步,成功打造出英特爾 Agilex D 系列 FPGA,從而將英特爾 Agilex FPGA 產(chǎn)品組合擴(kuò)展到邏輯密度和功耗更低、外形規(guī)格更小的應(yīng)用。英特爾 Agilex FPGA 和 SoC 家族早期成員采用的是英特爾 10 制程工藝節(jié)點(diǎn),而英特爾 Agilex D 系列產(chǎn)品采用的是英特爾 7 制程工藝技術(shù)。這項(xiàng)技術(shù)現(xiàn)已成為英特爾用來(lái)制造第 12 代英特爾 酷睿 CPU 和第四代英特爾 至強(qiáng) 可擴(kuò)展服務(wù)器用 CPU 等大容量 CPU 的成熟制造工藝。全新英特爾 Agilex D 系列 FPGA 和 SoC 采用英特爾 7 制程工藝與單體結(jié)構(gòu),性能出色,功耗低,可滿足不同應(yīng)用的多種要求(如下圖所示):

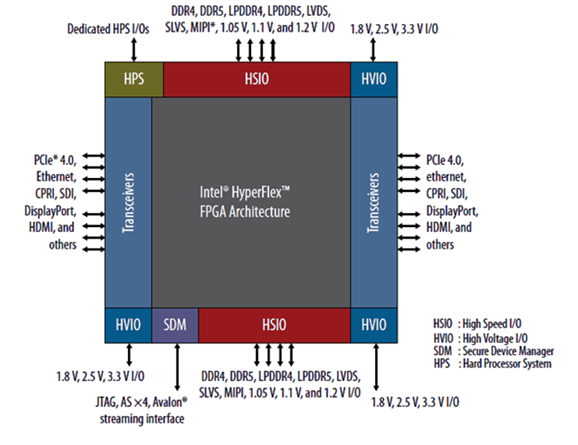

英特爾 7 制程工藝的運(yùn)用使英特爾打造的可編程邏輯器件能將快速 I/O 電路(包括 28 Gbps 高速 SerDes 收發(fā)器、靈活的通用 I/O Bank 以及可編程邏輯和固核 IP 模塊)集成在一個(gè)單體硅晶片上。而通過(guò)英特爾 7 制程工藝的厚柵氧化層晶體管變體,英特爾 Agilex D 系列 FPGA 可同時(shí)擁有高速 I/O Bank 和可支持在 3.3 V 電壓下運(yùn)行的高壓 I/O Bank。英特爾 Agilex FPGA 家族早期成員采用獨(dú)立的半導(dǎo)體小芯片。這些小芯片通過(guò)英特爾 嵌入式多芯片互連橋接 (EMIB) 技術(shù)和高級(jí)接口總線 (AIB) 技術(shù)進(jìn)行連接,可實(shí)現(xiàn)某些高級(jí) I/O 功能。英特爾 Agilex D 系列 FPGA 和 SoC 采用單體結(jié)構(gòu),可降低時(shí)延、優(yōu)化性能功耗比并減少成本。

此外,英特爾 Agilex D 系列 FPGA 和 SoC 產(chǎn)品還配備了若干硬核 IP 模塊。這些首次應(yīng)用于英特爾 Agilex FPGA 家族的模塊包括采用 AI 張量模塊的增強(qiáng)型 DSP、時(shí)間敏感網(wǎng)絡(luò)模塊、MIPI 接口和由 1 個(gè) Arm Cortex-A76 雙核處理器和 1 個(gè) Arm Cortex-A55 雙核處理器組成的升級(jí)版硬核處理器系統(tǒng)。借助 Arm 的 DynamIQ 多核處理器技術(shù),軟件開發(fā)人員可利用 Arm Cortex-A76 CPU 和 Cortex-A55 CPU 組成單一的融合集群,進(jìn)而為多種應(yīng)用帶來(lái)更低的功耗和更好的性能。

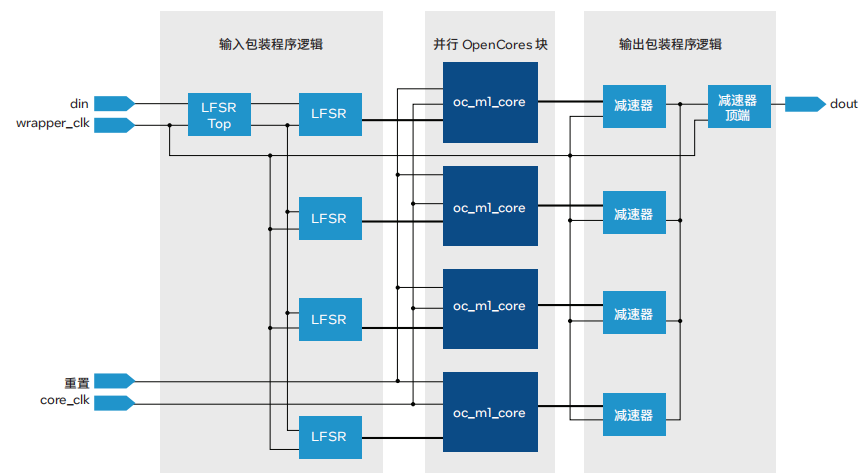

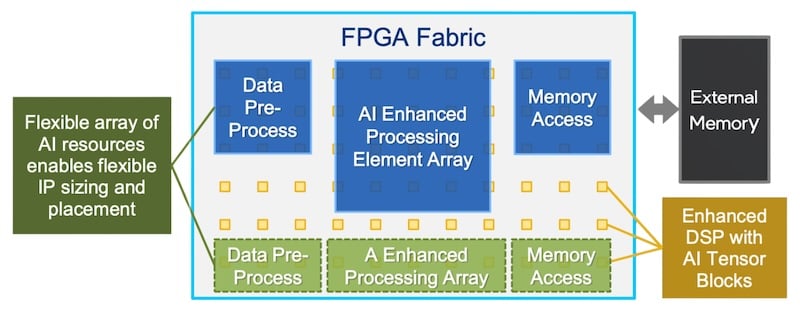

全新英特爾 Agilex D 系列 FPGA 和 SoC 的 FPGA 邏輯結(jié)構(gòu)中加入了采用 AI 張量模塊的增強(qiáng)型 DSP 功能。該功能模塊承襲了英特爾 Agilex FPGA 家族早期產(chǎn)品配備可變精度 DSP 模塊,支持多種 AI 工作負(fù)載的設(shè)計(jì)。除了上述功能,全新英特爾 Agilex D 系列 FPGA 和 SoC 還增加了源自英特爾 Stratix10 NX FPGA 所用張量模塊的特性,以兩種重要的新操作模式,支持 AI/圖像/視頻處理以及可執(zhí)行復(fù)數(shù)計(jì)算的 DSP 密集型應(yīng)用。

第一種新模式為 INT9 矢量模式。該模式可在一個(gè) DSP 模塊內(nèi)生成 6 次帶符號(hào)的 9 x 9 位或 8 x 8 位乘法運(yùn)算結(jié)果之和,而之前執(zhí)行同樣的計(jì)算任務(wù)需要 4 個(gè)英特爾Agilex FPGA DSP 模塊。這種模式對(duì)以 AI 為中心的張量數(shù)學(xué)運(yùn)算和各種 DSP 應(yīng)用非常有用。第二種新模式為復(fù)數(shù)模式。該模式可在進(jìn)行復(fù)數(shù)乘法運(yùn)算時(shí)將 DSP 模塊的性能提高一倍。以往進(jìn)行復(fù)數(shù)乘法運(yùn)算時(shí)通常需要兩個(gè) DSP 模塊,但英特爾 Agilex D 系列 FPGA 和 SoC 卻可以在一個(gè)采用 AI 張量模塊的增強(qiáng)型 DSP 內(nèi)進(jìn)行 16 位定點(diǎn)復(fù)數(shù)乘法運(yùn)算。

這些新的硬件特性加上高性能、低功耗的 FPGA 邏輯結(jié)構(gòu)使英特爾 Agilex D 系列 FPGA 和 SoC 非常適合從網(wǎng)絡(luò)邊緣到核心等不同市場(chǎng)的中端 FPGA 應(yīng)用,包括無(wú)線和有線通信、視頻和音頻廣播設(shè)備、工業(yè)應(yīng)用、測(cè)試和測(cè)量產(chǎn)品、醫(yī)療電子設(shè)備以及軍事/航空航天應(yīng)用。

審核編輯:郭婷

-

FPGA

+關(guān)注

關(guān)注

1626文章

21665瀏覽量

601805 -

英特爾

+關(guān)注

關(guān)注

60文章

9880瀏覽量

171485 -

soc

+關(guān)注

關(guān)注

38文章

4118瀏覽量

217930

原文標(biāo)題:解析丨全新英特爾? Agilex? D系列FPGA和SoC:為中端FPGA應(yīng)用帶來(lái)更高性能與更低功耗

文章出處:【微信號(hào):英特爾FPGA,微信公眾號(hào):英特爾FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Altera推出一系列FPGA軟、硬件和開發(fā)工具

Agilex 7 FPGA和SoC的基準(zhǔn)測(cè)試

Altera將AI注入新的中端FPGA

BittWare提供基于英特爾Agilex? 7 FPGA最新加速板

使用英特爾Agilex3和Agilex5器件構(gòu)建下一代數(shù)據(jù)中心平臺(tái)管理方案

英特爾和Altera宣布推出全新邊緣優(yōu)化處理器、FPGA可編程解決方案

英特爾旗下FPGA公司Altera正式亮相

中端FPGA成為主戰(zhàn)場(chǎng),Altera獨(dú)立后的市場(chǎng)格局

英特爾成立全新獨(dú)立運(yùn)營(yíng)的FPGA公司Altera

AMD推出全新Spartan UltraScale+ FPGA系列

英特爾旗下Altera正式獨(dú)立運(yùn)作,FPGA市場(chǎng)將迎來(lái)怎樣的巨變?

英特爾成立Altera新公司,專注FPGA端到端解決方案

英特爾宣布成立全新獨(dú)立運(yùn)營(yíng)的FPGA公司——Altera

全新英特爾Agilex D系列FPGA和SoC適用于中端FPGA應(yīng)用

全新英特爾Agilex D系列FPGA和SoC適用于中端FPGA應(yīng)用

評(píng)論