引言

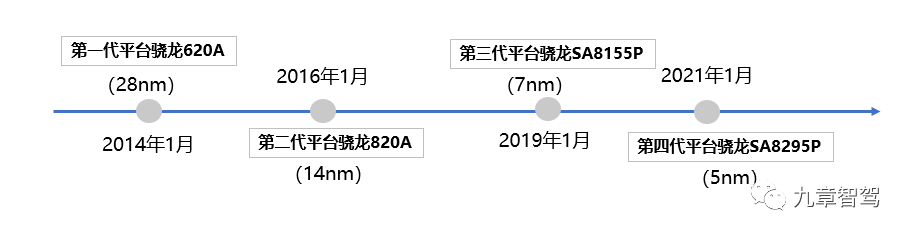

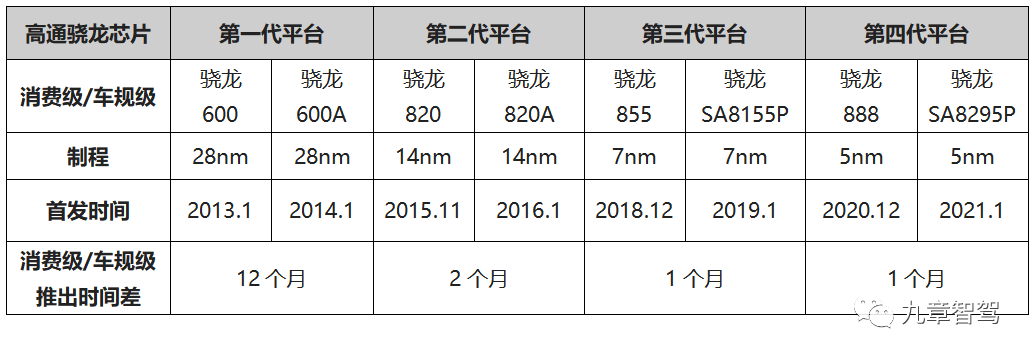

提到座艙域控制器用的主控SoC芯片,大家第一個會想到應該就是高通的SA8155P 。目前,在主機廠新上市的中高端車型中,其座艙的主控SoC芯片多是采用高通的SA8155P, SA8155P為什么會得到眾多主機廠的青睞呢?不妨先看一看高通座艙SoC芯片的迭代歷程。

高通座艙芯片的迭代歷程

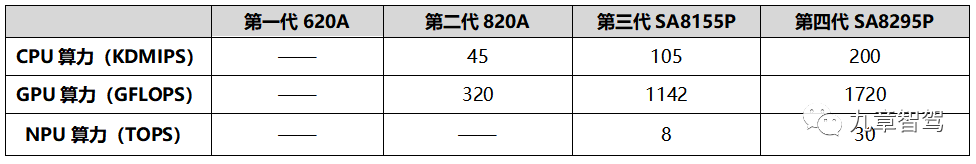

高通四代座艙SoC芯片的算力

通過對比高通的四代座艙芯片,能夠從側面反映出:智能座艙的算力需求在不斷增長,不管是CPU算力(DMIPS)、GPU算力(FLOPS)或者是NPU算力(TOPS)。

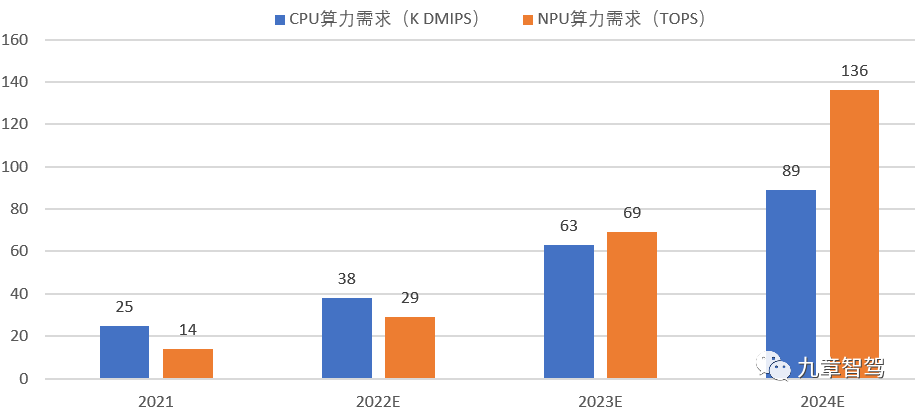

CPU算力和NPU算力需求預測(數據來源 - IHS Markit)

那么,智能座艙算力需求不斷增長的驅動力又是什么呢?

1)EE架構的不斷升級推動座艙功能集成化

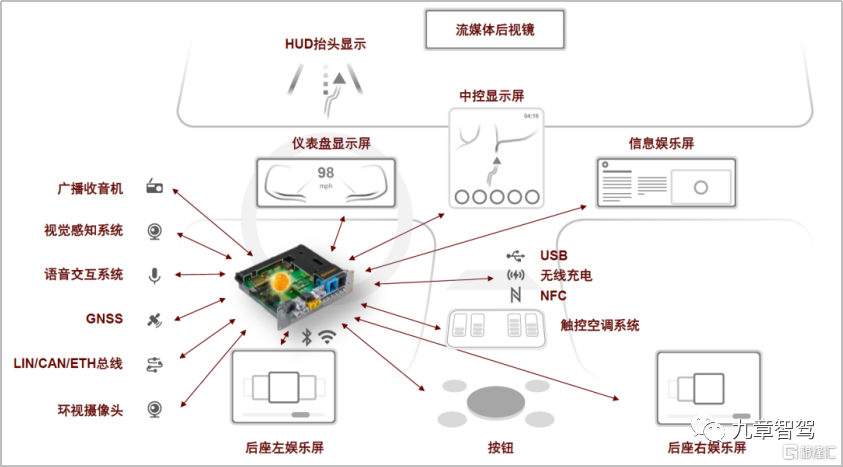

智能座艙系統架構圖(圖片來源:大陸集團,中金公司研究部)

座艙集成的功能越來越多,需要處理的數據越來越多、也越來越復雜,因此座艙對算力的需求將持續增長。當前座艙域控制器功能集成的外在表現主要有:一芯多屏、艙內感知技術融合 、艙泊一體等。

2)艙內應用場景的拓展

傳統意義上的座艙一般只服務于駕駛員,現在座艙的概念從“駕艙”擴展到整個“座艙”,服務的對象就不再只是重點針對駕駛員,還包括了副駕和后排乘客。

芯馳科技資深產品市場總監金輝說:“傳統的車機系統基本上只和駕駛員發生交互,而現在的智能座艙系統還需要同時和多個乘客發生交互,即多人交互。”

隨著自動駕駛能力由人機共駕過渡到無人駕駛階段,座艙的應用場景不斷拓展,除了用于導航、安全預警等傳統駕駛/安全相關的需求外,各種各樣的人機交互以及娛樂體驗變得越來越突出,座艙的應用場景開始逐漸延伸到辦公、生活以及娛樂等。

應用場景不斷地拓展,自然會衍生出一些新的功能需求,從而間接推動座艙算力需求的增長。

3)數據安全的重視

座艙內的應用生態越來越豐富,它對安全性的要求也變得越來越高。“每個人都希望保護好自己的隱私,國家也推出了數據保護和個人隱私保護相關的法律和法規。數據安全的處理,在一定程度上也會推高座艙對算力的需求。”均聯智行中國區CTO陳遠介紹說。

本文先從智能座艙域控制器的硬件架構特點入手,再從功能集成表現、產品形態、數據安全三個維度講智能座艙域控制器的技術發展趨勢。

1. 座艙域控制器硬件架構特點

? 1.1 座艙域控制器硬件架構方案:SoC + MCU

當前,座艙域控制器和智駕域控制器的硬件架構非常相似,都是SoC+MCU的方案。

座艙域控控制器的主控SoC芯片用于跑復雜的操作系統,做大數據的處理,比如圖像、視頻、音頻等非結構化數據的處理。

但是,現在的智能座艙主控SoC芯片架構多是從手機端遷移過來的,本身不帶車載網絡訪問的接口,比如CAN、MOST、LIN等。因此,需要搭配MCU去訪問車身網絡。因此,復雜的座艙域控制器一般都是采用兩類芯片:SoC+MCU。

一般情況下:

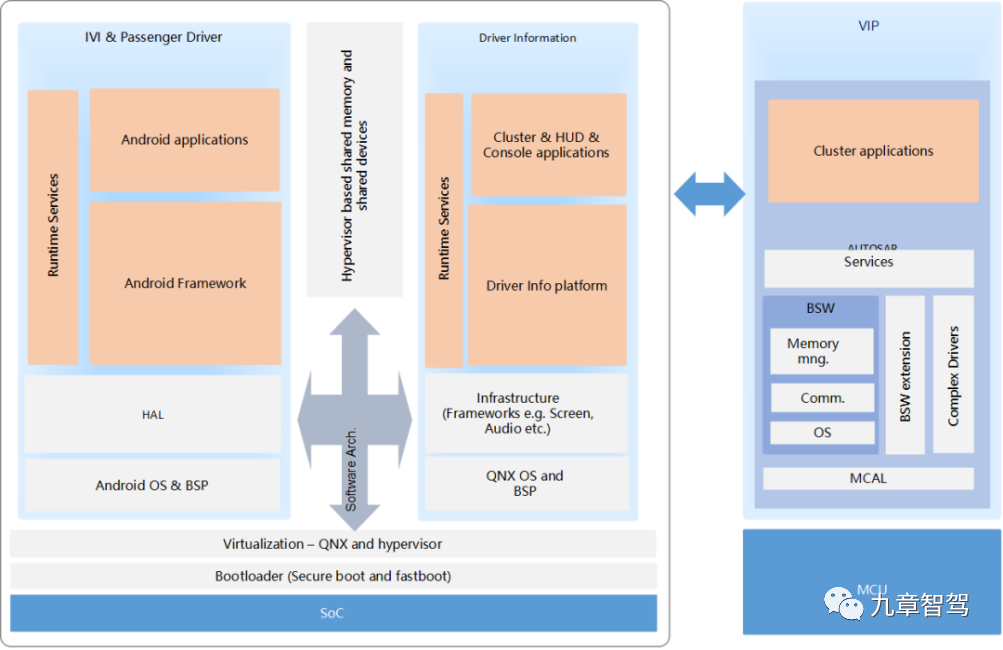

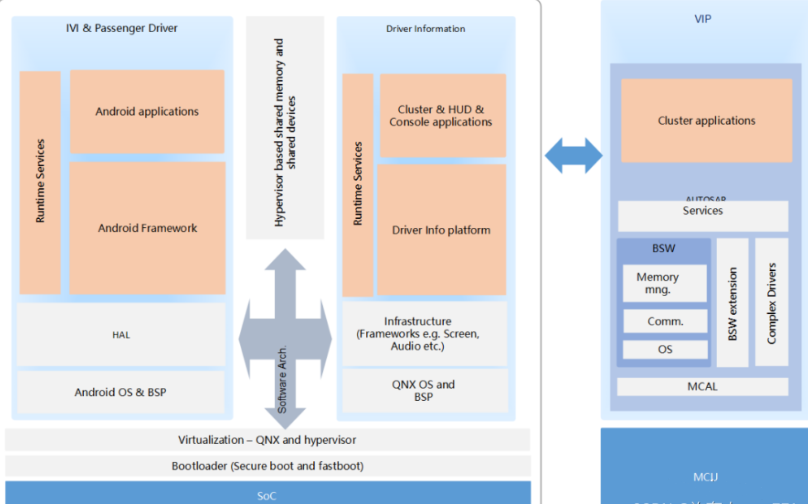

1)SoC運行Hypervisor,在Hypervisor之上運行兩類操作系統,其中對實時性和安全性要求比較高的安全域模塊跑在QNX或者Linux系統上;對實時性要求不太高、但對生態要求比較高的娛樂域模塊跑在Android系統上;

2)MCU運行AUTOSAR系統,用于CAN/LIN總線的喚醒、通訊以及電源管理等。

座艙域控系統軟件架構(圖片來源:公眾號-阿寶1990)

為什么MCU是座艙域控硬件架構中不可或缺的一部分呢?諾博汽車副總經理陳禮順解釋道:“MCU的實時性和可靠性要求非常高,啟動喚醒都是毫秒級別,需要支持CAN、LIN各類車載通訊總線。座艙域控制器與車身、動力等控制器的信息交互需要通過MCU來完成。另外,MCU還需要對SoC進行電源管理和狀態監控。

“也有廠商打算通過在SoC里面集成一個MCU模塊,來替代外掛的MCU,但是目前內置MCU的方案的可靠性有待驗證,并且集成后的MCU和SoC電源需要考慮獨立供電以降低靜態功耗,實現起來也相對復雜些。

“相比于MCU,SoC的功耗很大(靜態電流很大),所以在整機睡眠狀態下,SoC一般處于斷電狀態,MCU處于供電狀態。當MCU監控到有喚醒源時,會把SoC喚醒,然后SoC開始啟動工作;如果SoC需要進入睡眠模式,MCU會把SoC電源給斷掉。

“此外,整個產品級控制器的電源管理都是通過MCU去實現的,MCU是不可缺少的。”

1.2 座艙主控SoC芯片與智駕主控SoC芯片的區別

跟智駕主控soc芯片一樣,座艙主控SoC芯片也是采用異構多核架構,并且,兩者的內部架構也大體相似——都包括了CPU、GPU、NPU等多種異構資源 ,但座艙和智駕畢竟是兩種不同的應用場景,這就決定了座艙SoC芯片和智駕SoC芯片在設計的時候會各有側重點。

1)異構架構的側重點不同

座艙域控器主控SoC芯片的側重點是CPU和GPU,智駕域控器主控SoC芯片的側重點是CPU和NPU。

CPU用于通用邏輯運算,比如說系統調度、外部資源訪問等,不管是座艙系統,還是智駕系統,CPU資源都是不可或缺的。

GPU浮點運算能力強,但是在智駕SoC芯片上,基本上不會集成非常強的GPU,因為其內部NPU的張量單元本身就很強,不需要GPU去做張量運算和加速運算;座艙SoC芯片需要進行圖像的3D渲染、圖像拼接以及運行大型的3D 游戲等應用,因此座艙SoC芯片對GPU的能力要求會比智駕SoC芯片高。

NPU作為神經網絡算法的加速器,負責處理AI方面的計算需求。智能駕駛對NPU的算力需求比較大,這點毋容置疑;一些座艙SoC芯片雖然也帶有NPU模塊,可以做DMS或者LDW等一些基礎的駕駛輔助功能,但整體而言,座艙主控SoC芯片中的NPU性能要弱于智駕主控SoC芯片中的NPU。

總之,座艙主控SoC芯片是通用核強于專用核,智駕主控SoC芯片則是專用核強于通用核。

2)接口定義的區別

座艙域控器主控SoC芯片和智駕域控制器SoC芯片的接口定義也有很大的區別。均聯智行中國區CTO陳遠認為,座艙面向的應用場景更側重于艙內的人機交互能力。人機交互則需要提供大量的數據輸出,比如,視頻、聲音,還有其它投影圖像等數據輸出;同時,還需要獲取車里的數據輸入,主要是車內人員的數據輸入—— 有視頻(DMS/OMS)、也有聲音(麥克風)等。因此,座艙SoC芯片會面臨一些多樣化的傳感器數據的輸入和輸出要求。

諾博汽車副總經理陳禮順也基本認同這一觀點,他說:“座艙外設的側重點在于音視頻等大數據的輸入輸出等。比如,支持多少DP或DSI 接口—— 決定了能接多少路顯示屏;支持多少路TDM - 決定了是否可以實現更復雜的多場景音頻通路;還要支持GNSS、WIFI、Bluetooth等模塊接口。總之,座艙SoC芯片對外圍接口的要求非常高。

“在自動駕駛系統解決方案中,毫米波雷達信號一般通過CAN總線傳輸,激光雷達信號一般通過以太網傳輸,這些都是標準通訊接口,因此,智駕主控SoC芯片的外設接口就相對簡單,外設方面需要重點考慮攝像頭的接入。”

3)功能安全設計的差別

“功能安全不是針對芯片,而是針對產品本身。功能安全設計是一個系統工程,既可以在芯片層面設計一些冗余或者增加一些狀態檢測,也可以針對控制器產品本身進行系統級的監控以及功能分解。

“芯片廠商在做SoC芯片設計開發的時候,如果考慮功能安全,必然要考慮它具體的應用場景,是應用于座艙,還是應用于駕駛,甚至是具體的某些工況,然后再針對相應的場景、工況做針對性的基于芯片層面的功能安全設計。”諾博汽車副總經理陳禮順告訴九章智駕。

座艙SoC芯片和智駕SoC芯片在做功能安全認證方面沒有太大的差異,但是在功能安全設計上有一定的差別。

據相關業內人士透露,除芯片本身的功能安全設計之外,還需要有其它的設計來聯合保證智能駕駛的功能安全要求達標。芯片只是一部分,系統方案是另外一部分,如果要做系統方案備份,芯片設計本身就需有一些接口能夠做冗余通訊方式。

相對而言,座艙系統對功能安全設計的要求就要低很多,即便是對安全性和實時性要求比較高的儀表或者HUD模塊,主控SoC芯片功能安全等級達到ASIL B即可滿足要求。

2. 座艙功能集成化的表現

整車EE架構由分布式架構向域集中式架構升級,驅動座艙內一個個獨立的ECU集成到一個座艙域控制器的DCU上。座艙需要整合的功能越來越多,那么座艙進行功能整合的原則是什么?哪些功能適合被整合進去?

2.1 功能整合的原則

1)在座艙主控SoC芯片的能力邊界之內

集成什么樣的功能取決于座艙主控SoC,主機廠或Tier1會評估座艙主控SoC能夠支持接入多少路、多大分辨率的攝像頭和顯示屏;同時,也要看被整合功能的安全等級是否能夠被座艙芯片覆蓋到(不超過ASIL B),如果主控SoC的處理能力或性能能夠覆蓋到此功能,那么便可以初步判斷,此功能適合作為座艙功能的一個延伸,被集成進去。

2)無需額外新增硬件

如果增加一項或幾項功能,可以不用增加硬件,只需要把算法和軟件移植到座艙域控制器里面,同時,在成本上還具有一定的競爭力,此功能便適合被集成進去。

2.2 座艙功能集成化的三種表現

隨著智能座艙主控SoC芯片性能的不斷提升,以及5G車聯網、OTA等功能的加速滲透,無論是主機廠還是Tier1,都開始注重智能座艙域控制器在功能上的融合。座艙域控制器的功能集成主要表現在如下幾個方面:

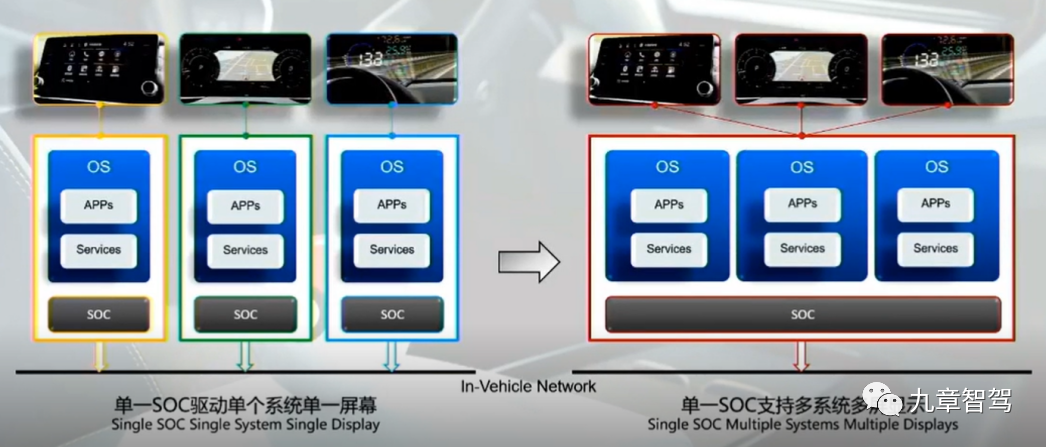

2.2.1 一芯多屏

在傳統的座艙解決方案中,中控、儀表等系統相互獨立,一般由單一芯片驅動單個功能/系統。隨著座艙智能化發展,座艙域控制器進一步集成儀表、HUD、流媒體后視鏡等其它系統 —— 從單個SoC驅動單個系統單一屏幕到單一SoC支持多系統多屏顯示。

一芯多屏(圖片來源:大眾對外公開宣講材料)

要在一個SoC芯片上支持多個屏的顯示,從安全性角度考慮,虛擬儀表、HUD需要采用QNX或者Linux系統;從軟件生態角度考慮,中控導航、副駕娛樂和后排娛樂則需要采用Android系統。

目前主流的方案是采用虛擬機-Hypervisor來實現在一個硬件上運行多個操作系統,那么現階段,Hypervisor技術在座艙上的應用還存在哪些不足或需要提升的地方?是否有其它技術可以作為Hypervisor技術的替代方案呢?

Hypervisor技術存在的不足或需要提升的地方:

1)會造成一定的硬件性能損失

芯馳科技資深產品市場總監金輝介紹說:“使用軟件虛擬化需要付出代價,不管是CPU、GPU,還是NPU,它們的算力在軟件虛擬化的過程中會流失掉一部分,并沒有被完全用起來,也就是說性能打了折扣。同時,外設訪問的性能也會受到軟件虛擬化的影響—— 多個系統要通過軟件虛擬化去訪問同一個接口,這個接口需要在虛擬機軟件里去做一些軟件層面的處理,訪問外設的效率和性能會降低。”

“ 使用Hypervisor一定會導致系統開銷增大,像GPU、CPU以及NPU等系統資源進行虛擬化處理的時候,硬件資源在不同的應用之間進行切換,不可避免地會造成系統總負載的升高。”均聯智行中國區CTO陳遠也基本認同這一觀點。

2)系統沒有實現有效的隔離

“Hypervisor技術是通過軟件來實現系統的劃分,并沒有實現硬件層面的有效隔離 —— 各系統都是放在同一個軟件的上層去運行,相比于硬隔離方案,功能安全和信息安全得不到有效的硬件保障。”芯馳科技資深產品市場總監金輝表示。

那么,是否有Hypervisor的替代方案呢?

均聯智行中國區CTO陳遠告訴九章智駕:“QNX的行業地位,短期內很難被撼動。所有的選擇都是在成本和效率之間去尋找平衡。目前有一些企業采用硬隔離的方案,硬隔離方案是一種選擇;不用硬隔離方案,在芯片上進行軟件隔離也是一種選擇。”

采用Hypervisor技術的優勢在于所有的IP核( CPU、GPU、DSP等)以及周圍的外設都可以共享,而硬隔離的問題在于資源不能很好地去共享。比如,安全域中用于儀表模塊的資源閑置了,也沒辦法分配給娛樂域去使用。

但是,硬隔離也有自身優勢,芯馳科技資深產品市場總監金輝表示:“相比于Hypervisor技術,采用硬隔離方案便無需支付虛擬化軟件上的License費用,并且算力也不打折扣,功能安全和信息安全也能夠得到保障。”

2.2.2 艙內感知技術融合

目前DMS的主流實現方案是基于人臉識別的視覺技術,對芯片的要求很高 —— 首先是車規級的要求,需要經過環境試驗和壽命試驗等可靠性認證;其次是對AI算力的需求也較高,比如,為了準確識別人臉3D 的球狀形象,不僅需要較高分辨率的攝像頭,在圖像數據采集后還需要將模型進行優化。

隨著技術的發展,DMS延伸發展到了OMS,即將檢測范圍從駕駛員擴展到車內乘客,比如,檢測乘客是否系安全帶,下車的時候是否把兒童遺忘在車內等應用場景。當前不少主機廠已經將DMS和OMS組合起來進行應用。

DMS及OMS功能主要是通過對艙內攝像頭數據的實時分析來實現的。現在座艙主控SoC芯片的算力和性能越來越強,不僅能夠支持多通道的視頻輸入能力,還集成有單獨的DSP單元。

將DMS/OMS功能融合到座艙,不僅是因為座艙SoC芯片的性能能夠覆蓋到DMS/OMS ,也是因為把它們融合到座艙,它們便可以和座艙內的其它關聯模塊更好地進行信息交互。

比如,偉世通的 HMEye 是基于視線測量的 DMS,除了可以監測駕駛員的雙手和視線是否在駕駛狀態,它還可以讓駕駛員通過眼球的轉動實現開關廣播、調整溫度、開啟導航等功能,這樣,在駕駛過程中,駕駛員便可以更安全地去進行人機互動。

2.2.3 艙泊一體

泊車融入到座艙也有功能集成化的因素:早期的360環視都有單獨的控制器;后來360環視和自動泊車輔助APA進行融合,再升級到融合泊車功能,控制器的性能再次升級;再往后發展,座艙主控SoC芯片具了更強的CPU算力和AI算力,具備了整合泊車功能的條件,于是,也便有了把泊車功能融合到座艙的需求出現。

座艙整合基本的泊車功能:一是可以降本,至少可以把原來泊車的控制器省掉,能夠節省一定的物料成本;二是整合到座艙,能夠更好地做泊車場景下的人機交互設計,把泊車功能融入到座艙,座艙域控制器會得到更多的泊車信號;最后,座艙上的算力也能得到最大程度的利用。

均聯智行中國區CTO陳遠解釋道:“泊車功能是在停車的場景下才會用到,剛好跟座艙上的一些應用形成時間上的錯位 ,比如導航信息顯示、行車信息顯示都是在行車的時候使用,泊車的時候這些應用基本都處于停用狀態,因此,泊車時便可以將座艙上剩余的大部分算力全部用于做泊車的相關應用。”

3. 座艙域控制器產品形態的變化

在不同的自動駕駛階段,座艙域控設計理念上的不同,甚至會導致產品的形態產生較大的差異。

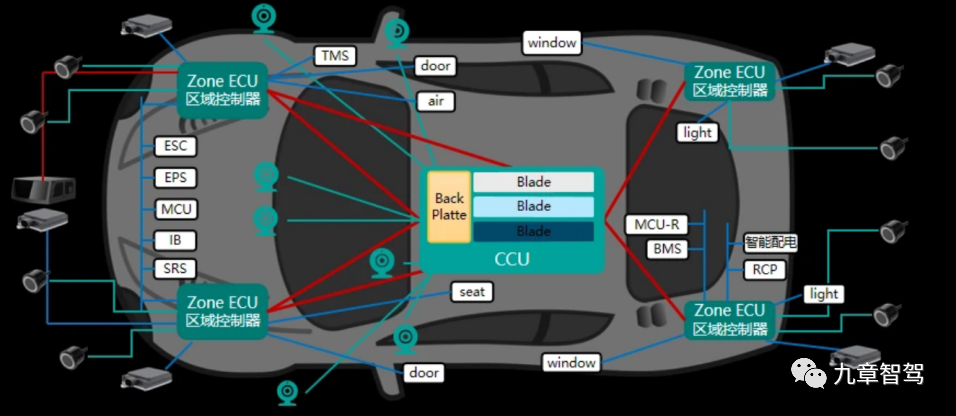

從技術發展趨勢上來看,當前屬于人機共駕階段,即所謂的駕駛輔助階段。在此階段,智駕域控和智艙域控還是兩個獨立的控制器。等過渡到真正的無人駕駛階段,業內人士普遍認為,隨著整車電子電氣架構的進一步升級,達到所謂的中央計算平臺+區域控制器的架構階段,座艙和智駕的功能會高度融合,即艙駕一體。

中央計算+區域控制架構(圖片來源:均聯智行對外宣傳材料)

根據不同階段的EE架構和主控SoC芯片的融合能力,艙駕一體高性能計算平臺又會出現不同的形態:

采用多顆SoC芯片,座艙和智駕功能分別部署在不同板子上,板間通過以太網或PCIE連接

采用多顆SoC芯片,座艙和智駕功能部署在同一個板子上

座艙和智駕功能部署到單SoC芯片上

現在有人提到艙架一體HPC,但它也不是單SoC芯片方案,基本上是由兩塊板子組成,一塊板子跑智能座艙系統,另外一塊板子跑智能駕駛系統,但是,這樣的結構形式對散熱設計和供電設計提出了很高的要求。

某主機廠EE架構專家告訴九章智駕:“在域控制器階段,智艙和智駕還是分別采用單獨的盒子控制,這在目前來看還是比較好的方案。如果現在要把兩個獨立盒子的方案改為一個盒子內兩塊板子的方案,成本應該是可以降低,但在工程上會比較麻煩:比如一盒子里有多塊板子,不同的板子用不同的供應商,中途發現不好用,換起來會很麻煩;如果是改為一個盒子一塊板子的方案,意味著要把太多的功能綁在一塊板子上,必然要受多方的牽扯,前期的協調溝通以及后期的更換維護都會比較復雜。”

某主機廠資深工程師也同意現階段座艙系統和智駕系統應該相互獨立的觀點,他說:“單純從整車EE架構的演進來看,艙駕融合肯定是大勢所趨,但從短期來看,把智駕和智艙結合在一起,純粹是一種形式上的結合,不是從產品需求的角度分解出來的結果。

“兩者面向的應用場景、功能定義、性能邊界都不一樣,至少從目前來看,我覺得兩者沒必要去融合,如果硬要把他們捏在一起,不管是芯片的選型,還是外圍電路的設計,面臨的要求都不一樣。那么,在成本和性能的考慮上,我們到底應該傾向于誰?總之,兩者融合的方式會給開發者帶來一系列設計方面的難題。”

雖然單SoC芯片的艙駕一體架構方案才能實現真正的座艙和智駕融合,但是座艙和智駕在功能需求、功能安全要求、信息安全要求以及對不同類型算力需求的側重點等多個方面的要求是不一樣的,如果兩者放在一個芯片內去做,系統將會異常復雜,短期內很難有一款單SoC芯片能夠同時滿足這樣的需求。

現階段,單SoC芯片的艙駕一體方案仍面臨一些硬件和軟件上的問題。具體面臨什么樣的問題,這里便不多做介紹,感興趣的讀者可查看筆者之前的文章:“艙駕融合”技術發展趨勢分析,里有比較詳細的介紹。

4. 智能座艙的數據安全防護

現在座艙內的攝像頭越來越多,艙內的功能也日漸豐富。座艙系統將會在本地使用大量的用戶數據,同時也需要和云端保持實時的數據共享和同步,座艙域控制器是車企后續進行用戶數據收集、OTA的重要端口,因此座艙系統的數據安全將變得非常重要。

那么應如何保護用戶的私有敏感數據信息不被泄露和非法使用呢?

4.1 確保操作系統本身的信息安全

首先,要確保操作系統本身的信息安全,比如,Andriod、QNX等系統在啟動的時候,需要做安全啟動校驗,防止系統遭到病毒感染。另外,對操作系統進行權限控制,做一些最小化的授權事項,避免所有的應用都可以訪問一些很私密的區域。

其次,控制器之間的通信需要做一些安全通信處理,比如做C2C加密,一個報文過來,需要校驗是誰發的。

4.2 數據加密和脫敏處理

數據采集和數據存儲不僅需要得到用戶的授權,同時還需要進行加密和脫敏處理。

數據加密 ——座艙SoC芯片里有一個信息安全的模塊HSM,它內置了信息安全的加密引擎。用戶有了這些引擎和配套的處理器之后,可以在上層構建一些加密算法,比如國密的SM2/SM3/SM4/SM9,或者是商用的一些加密算法等。

座艙信息安全的基本框架主要就是私鑰加密+公鑰解密。傳輸的隱私數據,第一,需要簽授權;第二,需要加密。也就是說,用私鑰加密,加密完了之后把數據發給對方。對方用公鑰解密后才能看到數據。在傳輸過程中,其他任何人如果沒有公鑰,即便拿到數據也解密不出來。

數據脫敏 ——識別人的時候不能識別人的身份,也不能識別人的個性特征,比如,是男還是女。采集數據自然就可能會涉及到對他人隱私的侵犯,所以數據必須要經過脫敏處理。并且,很多數據必須在終端上處理,不能送到云端處理,以避免在往云端傳輸的過程中出現數據泄露的風險。

總之,數據安全的防護是非常復雜的工程,需要從各個方面去考慮。在保護數據的同時,還要防止被黑客侵入。“在全球,有很多黑客去攻擊特斯拉的車輛,去尋找漏洞,然后再上報給特斯拉去獲取一些獎勵。現在很多車輛都要求做滲透測試,也就是說去找一家第三方公司去破解這輛車,看它有沒有漏洞。”均聯智行中國區CTO陳遠舉例說。

5. 座艙主控SoC芯片市場格局

當前,座艙域控制器的主控SoC芯片的市場格局已經逐漸明朗:中低端市場 —— 傳統汽車芯片廠商是主力,比如 瑞薩、TI、恩智浦等;高端市場 —— 消費電子芯片廠商是主力,比如高通、三星、英特爾、AMD等。

為什么消費電子芯片廠商能夠殺入到座艙芯片市場領域?

有業內專家指出,消費電子芯片廠商之所以能夠進入座艙領域,是因為從消費電子芯片轉向座艙芯片的壁壘并不高 —— 兩者在技術層面的要求高度相似,車規級的特殊要求主要體現在壽命、適應車載環境等安全層面,然而,消費電子芯片廠商通過這些車規級認證的難度并不是特別大。

同時,消費電子芯片廠商在消費端已經具備了足夠強的設計能力,從而能夠幫助他們在相對小眾的汽車領域里,也能提供類似工藝和設計的車規級座艙芯片。

消費電子芯片廠商不但殺入了座艙領域,為什么還能牢牢霸占座艙領域的高端市場?

1)成本優勢

消費級芯片廠商能夠最大化利用其在消費端的生產能力,去攤銷整個芯片設計的成本。因此當其把消費端的芯片轉移到座艙領域來應用,在成本上對傳統芯片廠商是一個降維打擊。

諾博汽車副總經理陳禮順說:“ 座艙的SoC芯片一般都會包含CPU、GPU、NPU、DSP等等,這些IP設計與授權一般都是來自第三方公司,比如ARM, Imagination等,對于傳統汽車芯片廠商,這些IP的授權費都是非常高的,但對于高通來講,一是很多IP都是進行自研設計,二是ARM的架構授權費也是要比一些傳統汽車芯片廠商低很多。”

2)芯片的性能和迭代速度優勢

首先,消費電子芯片廠商的座艙芯片在先進制程和大算力上具有明顯的優勢。

其次,消費電子芯片廠商的座艙芯片迭代速度快。消費電子芯片廠商可以在智能消費電子芯片迭代的基礎上再去迭代座艙芯片,他們的芯片迭代的速度自然要遠遠快于傳統汽車芯片廠商。

高通四代座艙平臺的基礎信息(數據來源:公開資料整理)

備注:截止目前為止,高通總共對外發布了四代座艙芯片,而這四代芯片都是遵循著“消費級芯片先發,智能座艙芯片后改”的底層邏輯。

審核編輯 :李倩

-

芯片

+關注

關注

453文章

50406瀏覽量

421833 -

控制器

+關注

關注

112文章

16203瀏覽量

177413 -

智能座艙

+關注

關注

4文章

911瀏覽量

16274

原文標題:智能座艙域控制器技術發展趨勢分析

文章出處:【微信號:阿寶1990,微信公眾號:阿寶1990】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

開關電源的最新技術發展趨勢

未來的ar技術發展趨勢

Arm Cortex-R82AE賦能高性能區域控制器設計

無線充電技術發展趨勢

2024年全球與中國7nm智能座艙芯片行業總體規模、主要企業國內外市場占有率及排名

座艙域控制器硬件架構方案:SoC + MCU

智能座艙域控制器技術發展趨勢分析

智能座艙域控制器技術發展趨勢分析

評論