Zynq的開(kāi)發(fā)四種方式

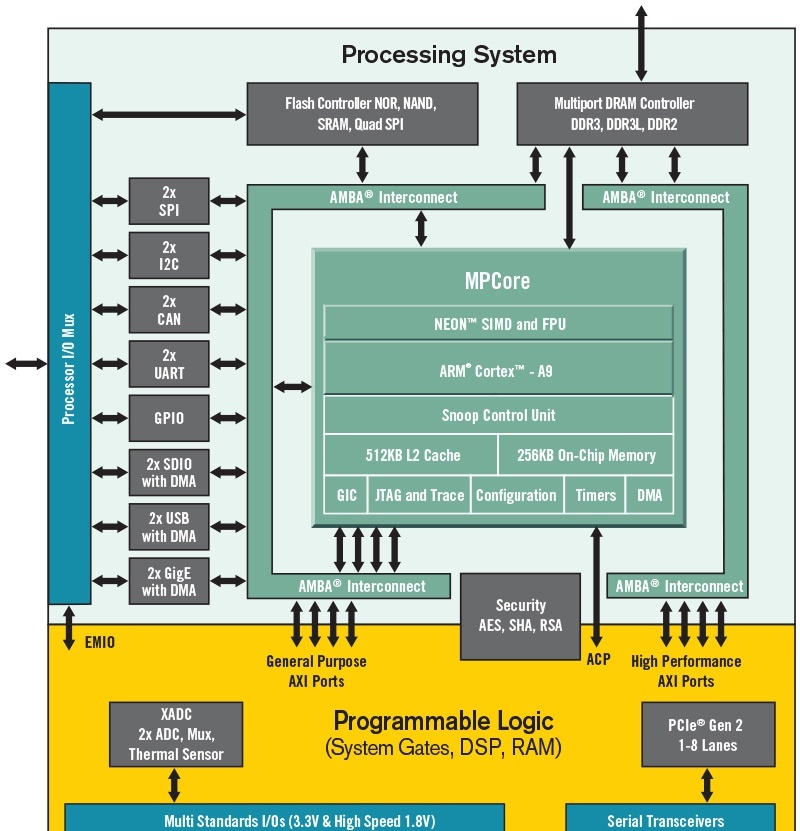

ZYNQ中包含了兩個(gè)部分,雙核的arm和FPGA。根據(jù)XILINX提供的手冊(cè),arm模塊被稱為PS,而FPGA模塊被稱為PL。

ZYNQ內(nèi)部包含PS和PL兩部分,ZYNQ開(kāi)發(fā)有一下四種方式:

A:純PS開(kāi)發(fā)

PS中包含2個(gè)ARM Cortex-9的內(nèi)核,一些基本的外設(shè)擴(kuò)展口以及Memory接口。PS中包含以下4個(gè)主要功能模塊:

Application processor unit (APU)

Memory interfaces

I/O peripherals (IOP)

Interconnect

PS開(kāi)發(fā)有兩種方式:即傳統(tǒng)的arm的方式和xilinx方法(這個(gè)是生成一個(gè)elf文件,這個(gè)elf文件包括了硬件配置信息(xmp)和裸跑程序(c文件))。

B:純PL開(kāi)發(fā)

PL即FPGA,這個(gè)和一般的xilinx的FPGA沒(méi)有很大的區(qū)別。

C:PS+PL(不跑操作系統(tǒng))開(kāi)發(fā)

生成elf文件包括了硬件配置信息(xmp)和裸跑程序(c文件),還有一個(gè).bit文件。

D:PS+PL(跑操作系統(tǒng))開(kāi)發(fā)

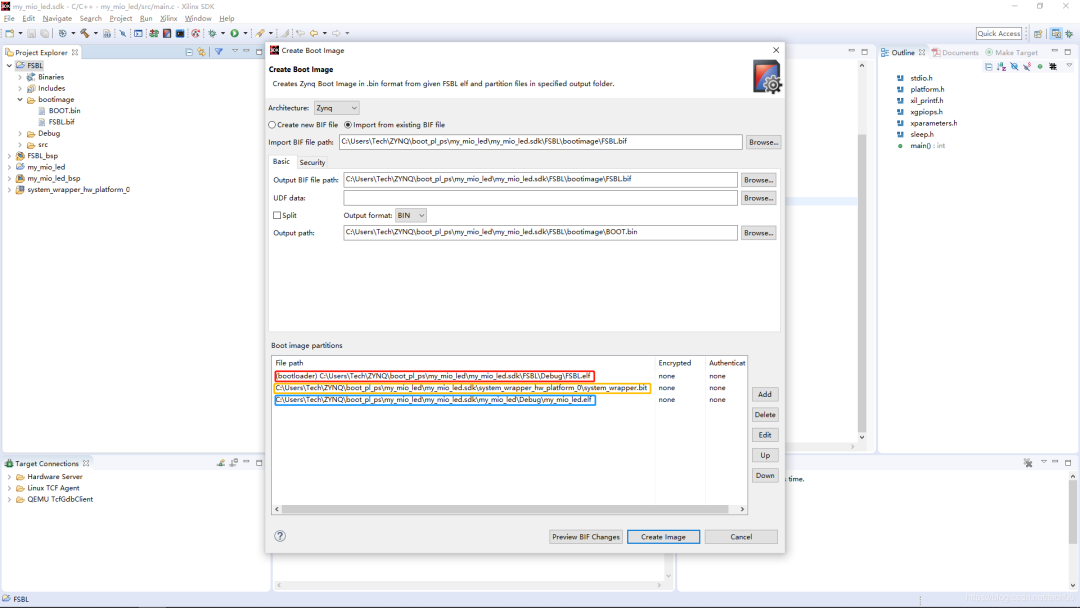

這個(gè)就需要BOOT.BIN,設(shè)備樹(shù),linux內(nèi)核鏡像,文件系統(tǒng)了。

其中BOOT.BIN是由3部分組成的(boot.elf, .bit, fsbl.elf),boot.elf這個(gè)是由交叉編譯環(huán)境產(chǎn)生的,相當(dāng)于ssbl,.bit文件是PL使用文件,fsbl.elf這個(gè)是fsbl。

之前剛開(kāi)始學(xué)FPGA的時(shí)候用的是基于spartan的FPGA開(kāi)發(fā)板,當(dāng)上手ZYNQ后一直以為ZYNQ就是在資源上做了升級(jí),我所要做的工作無(wú)非是把開(kāi)發(fā)工具從ISE升級(jí)到VIVADO罷了,后來(lái)發(fā)現(xiàn)自己還是過(guò)于天真了,很多事都有存在的意思,上手之后便發(fā)現(xiàn)ZYNQ和之前的板子有區(qū)別。

SOC FPGA

區(qū)別就是ZYNQ除了傳統(tǒng)FPGA外,還把ARM核和FPGA結(jié)合在了一起,成為了內(nèi)嵌處理器硬核的FPGA,即SOC FPGA,二者利用高速總線AXI4進(jìn)行通信。

內(nèi)部結(jié)構(gòu) PL與PS

由于它既有FPGA又有ARM,所以它同時(shí)具有ARM軟件的可編程性和FPGA 的硬件可編程性,不僅可實(shí)現(xiàn)重要分析與硬件加速,同時(shí)還在單個(gè)器件上高度集成CPU、DSP、ASSP 以及混合信號(hào)功能。

從結(jié)構(gòu)來(lái)看,支持FPGA的部分稱為PL(Programmable Logic),支持ARM的部分稱為PS(Processing System),如下圖所示。

可以看出PS部分有很多接口,如SPI,UART,CAN等等,這些接口的存在可以讓FPGA不用寫控制器去傳輸,節(jié)省了資源但是犧牲了速度。

工作

PL端和PS端一般通過(guò)AXI4總線通信,使用AXI4的PL模塊會(huì)有相應(yīng)c驅(qū)動(dòng)文件,用于PL端模塊的控制。這些驅(qū)動(dòng)文件有裸機(jī)版本,也有l(wèi)inux版本,linux運(yùn)行時(shí),如果調(diào)用pl端模塊就使用這些驅(qū)動(dòng)即可。

Zynq的啟動(dòng)分三個(gè)階段。階段0是BOOTROM的固化代碼,不用管;階段1中,first stage boot loader 首先配置PS端,之后硬件比特流對(duì)PL進(jìn)行配置。階段2運(yùn)行用戶程序,Linux的BOOT loader在這個(gè)階段才開(kāi)始運(yùn)行。

ZYNQ并不能說(shuō)是一個(gè)嵌入ARM核的FPGA。從它的啟動(dòng)過(guò)程就可以發(fā)現(xiàn),絕對(duì)是ARM主導(dǎo)的,因此稱它為以高性能FPGA為外設(shè)的雙核ARM或許更為合適。

那么就有一個(gè)問(wèn)題Zynq可以作為獨(dú)立的ARM或者獨(dú)立的FPGA使用嗎?答案是肯定的,可以的。

首先,Zynq可以作為獨(dú)立的ARM使用是顯而易見(jiàn)的,因?yàn)閆ynq中ARM就是主處理器,上電啟動(dòng)過(guò)程也是由ARM來(lái)完成的,除了新建ARM工程時(shí)需要HDL硬件描述文件(HDL硬件描述文件的制作也很簡(jiǎn)單),其他都一樣。

其次,Zynq作為獨(dú)立的FPGA使用其實(shí)也是可以的,首先我們可以跟使用傳統(tǒng)的FPGA一樣使用Vivado集成開(kāi)發(fā)環(huán)境綜合編譯工程并通過(guò)JTAG接口下載bit文件。唯一的不同是在我們燒寫啟動(dòng)時(shí),我們需要把bit文件和FSBL源碼合成為一個(gè)bin文件燒寫后才能啟動(dòng),上電啟動(dòng)時(shí)ARM會(huì)先運(yùn)行加載FSBL程序,然后通過(guò)FSBL會(huì)加載FPGA的程序。FSBL程序是Xilinx提供的集成在SDK里的二級(jí)boot loader程序,我們?cè)赟DK集成開(kāi)發(fā)環(huán)境中通過(guò)很簡(jiǎn)單的操作就可以完成FSBL程序和bit文件的合成。

上圖中紅色框框出來(lái)的是二級(jí)boot loader程序,黃色框框出來(lái)的是FPGA程序,藍(lán)色框框出來(lái)的是ARM的用戶應(yīng)用程序,如果我們把Zynq作為獨(dú)立的FPGA使用時(shí),我們就可以刪除藍(lán)色框即ARM用戶應(yīng)用程序,保留紅色框二級(jí)boot loader程序和黃色框FPGA程序即可。

審核編輯 :李倩

-

FPGA

+關(guān)注

關(guān)注

1626文章

21669瀏覽量

601866 -

Zynq

+關(guān)注

關(guān)注

9文章

608瀏覽量

47128

原文標(biāo)題:zynq 和fpga區(qū)別快速認(rèn)識(shí)Zynq開(kāi)發(fā)

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

dac3174與xilinx zynq7000系列連接,fpga的案例參考代碼有沒(méi)有?

正點(diǎn)原子fpga開(kāi)發(fā)板不同型號(hào)

ZYNQ核心板學(xué)習(xí)筆記

正點(diǎn)原子ZYNQ7015開(kāi)發(fā)板!ZYNQ 7000系列、雙核ARM、PCIe2.0、SFPX2,性能強(qiáng)悍,資料豐富!

[XILINX] 正點(diǎn)原子ZYNQ7035/7045/7100開(kāi)發(fā)板發(fā)布、ZYNQ 7000系列、雙核ARM、PCIe2.0、SFPX2!

FPGA(ZYNQ AX7Z020)輸出pwm波形振蕩。

簡(jiǎn)談Xilinx Zynq-7000嵌入式系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

Xilinx ZYNQ 動(dòng)手實(shí)操演練

Zynq-7000為何不是FPGA?

沒(méi)用過(guò)zynq今天在看解析是發(fā)現(xiàn)汽車的CID上有用這個(gè),不知道zynq有什么優(yōu)勢(shì)?

簡(jiǎn)談Xilinx Zynq-7000嵌入式系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

基于ZYNQ FPGA構(gòu)建嵌入式的模擬計(jì)算板卡

基于ZYNQ FPGA的工業(yè)現(xiàn)場(chǎng)綜合數(shù)據(jù)采集嵌入式計(jì)算機(jī)

zynq和fpga區(qū)別快速認(rèn)識(shí)Zynq開(kāi)發(fā)

zynq和fpga區(qū)別快速認(rèn)識(shí)Zynq開(kāi)發(fā)

評(píng)論