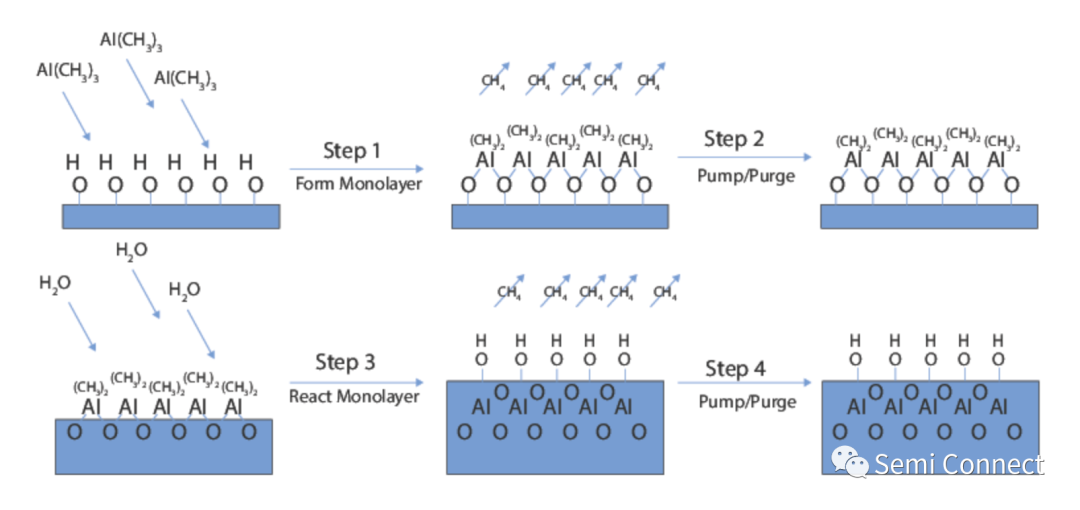

原子層沉積 (AtomicLayer Deposition, ALD)是指通過單原子膜逐層生長(zhǎng)的方式,將原子逐層沉淀在襯底材料上。典型的 ALD 采用的是將氣相前驅(qū)物(Precursor)交替脈沖式地輸人到反應(yīng)器內(nèi)的方式。

例如,首先將反應(yīng)前驅(qū)物 1通入到襯底表面,并經(jīng)過化學(xué)吸附,在襯底表面形成一層單原子層,接著通過氣泵抽走殘留在襯底表面和反應(yīng)腔室內(nèi)的前驅(qū)物1;然后通入反應(yīng)前驅(qū)物2到襯底表面,并與被吸附在村底表面的前驅(qū)物1 發(fā)生化學(xué)反應(yīng),在耐底表面生成相應(yīng)的薄膜材料和相應(yīng)的副產(chǎn)物;當(dāng)前驅(qū)物1完全反應(yīng)后,反應(yīng)將自動(dòng)終止,這就是 ALD 的自限制 (Self-Limiting)特性,再抽離殘留的反應(yīng)物和副產(chǎn)物,準(zhǔn)備下一階段生長(zhǎng);通過不斷重復(fù)上述過程,就可以實(shí)現(xiàn)沉積逐層單原子生長(zhǎng)的薄膜材料。

ALD與 CVD 都是通入氣相化學(xué)反應(yīng)源在襯底表面發(fā)生化學(xué)反應(yīng)的方式,不同的是 CVD 的氣相反應(yīng)源不具有自限制生長(zhǎng)的特性。由此可見,開發(fā)ALD 技術(shù)的關(guān)鍵是尋找具有反應(yīng)自限制特性的前驅(qū)物。

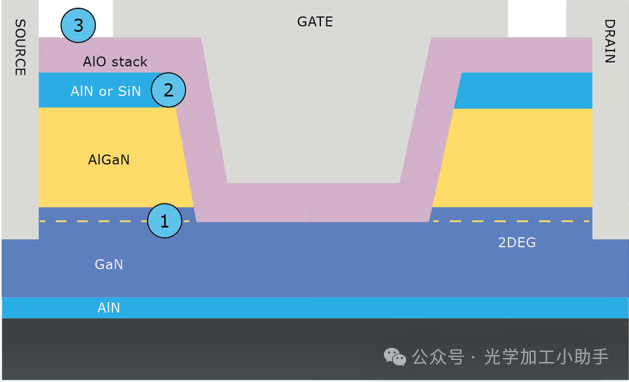

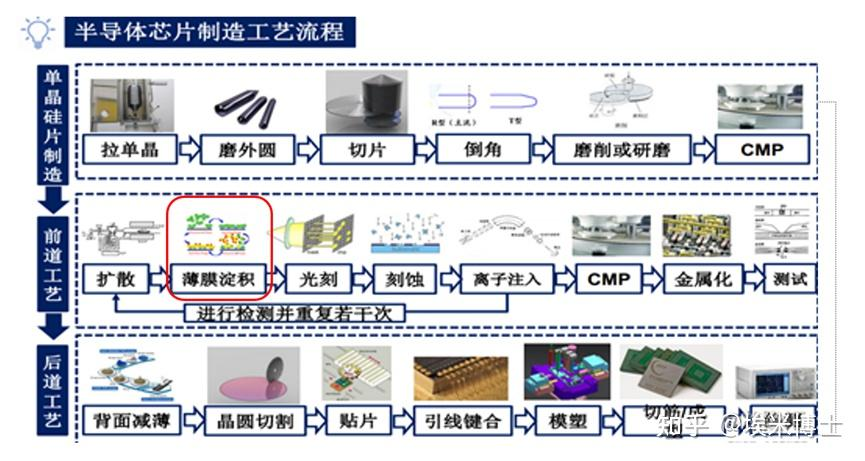

由于 ALD 技術(shù)逐層生長(zhǎng)薄膜的特點(diǎn),所以 ALD 薄膜具有極佳的合階覆蓋能力,以及極高的沉積均勻性和一致性,同時(shí)可以較好她控制其制備薄膜的厚度、成分和結(jié)構(gòu),因此被廣泛地應(yīng)用在微電子領(lǐng)域。尤其是 ALD 具有的極佳的臺(tái)階覆蓋能力和溝槽填充均勻性,十分適用于棚極側(cè)墻介質(zhì)的制備,以及在較大高寬比的通孔和溝槽中的薄膜制備。

ALD 技術(shù)在產(chǎn)業(yè)中的主要應(yīng)用領(lǐng)域?yàn)闁艠O側(cè)墻生長(zhǎng)、高k柵介質(zhì)和金屬柵(Metal Gate)、銅互連工藝中的阻擋層 (BarierLayer)、微機(jī)電系統(tǒng)(MEMS)、光電子材料和器件、有機(jī)發(fā)光二極管 ( OrganieLight Eimiting Diode, OLED)材料、DRAM 及 MRAM 的介電層、嵌人式電容、電磁記錄磁頭等各類薄膜。

隨者集成電路的發(fā)展,器件的尺寸越來越小,生長(zhǎng)的薄膜厚度不斷縮小且深槽深寬比不斷增加,使得 ALD 技術(shù)在先進(jìn)技術(shù)節(jié)點(diǎn)的應(yīng)用越來越多,如從平面器件轉(zhuǎn)到 FinFET 器件后,自對(duì)準(zhǔn)兩次曝光技術(shù)的側(cè)墻采用 ALD 技術(shù)生長(zhǎng);從多晶硅柵轉(zhuǎn)向高k介質(zhì)金屬柵技術(shù),高k介質(zhì)和金屬柵疊層生長(zhǎng)過程也采用了 ALD 技術(shù)。

審核編輯 :李倩

-

原子

+關(guān)注

關(guān)注

0文章

85瀏覽量

20282 -

反應(yīng)器

+關(guān)注

關(guān)注

2文章

96瀏覽量

11030

原文標(biāo)題:原子層沉積(Atomic Layer Deposition,ALD)

文章出處:【微信號(hào):Semi Connect,微信公眾號(hào):Semi Connect】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

OSI七層模型中各層的協(xié)議 OSI七層模型的優(yōu)勢(shì)與不足

OSI七層模型的每一層功能

淺談薄膜沉積

原子層鍍膜在功率器件行業(yè)的應(yīng)用

最新Science:原子層沉積技術(shù)在鈣鈦礦太陽(yáng)能電池中沉積錫氧化物(SnOx)以提高其長(zhǎng)期穩(wěn)定性的研究

wdm主要應(yīng)用在傳輸網(wǎng)絡(luò)的什么層

周星工程研發(fā)ALD新技術(shù),引領(lǐng)半導(dǎo)體工藝革新

中微推出自研的12英寸原子層金屬鎢沉積設(shè)備Preforma Uniflex AW

江蘇魯汶儀器股份有限公司揭示原子層刻蝕新方法

蘋果測(cè)試新抗反射涂層技術(shù),提升iPhone相機(jī)成像水平

流量控制器在半導(dǎo)體加工工藝化學(xué)氣相沉積(CVD)的應(yīng)用

原子力顯微鏡AFM測(cè)試與案例分享

化學(xué)氣相沉積與物理氣相沉積的差異

原子層沉積(Atomic Layer Deposition,ALD)

原子層沉積(Atomic Layer Deposition,ALD)

評(píng)論