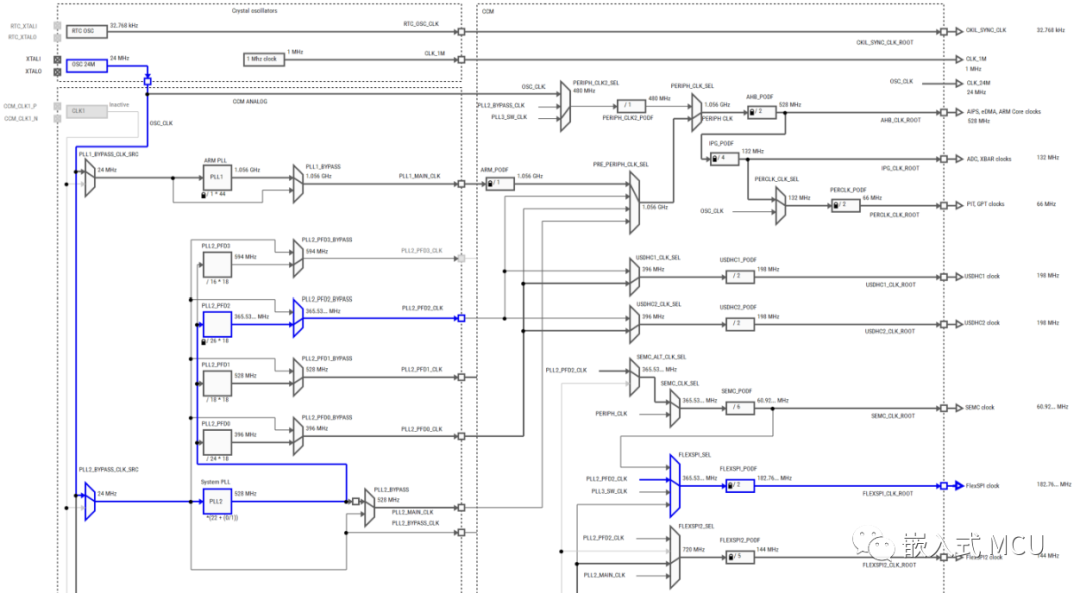

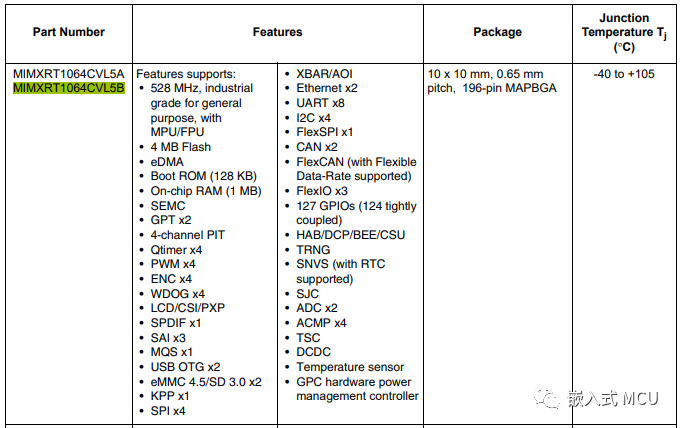

NXP MIMXRT1064CVL5B 能否支持使用SPI接口的HyperRAM?使用HyperRam的原因是為LCD存儲幀或者USB記錄數據或者以太網采集通信數據都需要緩沖區。使用NXP MIMXRT1062DVL6B MCU,SDRAM使用并行接口會占用很多GPIO引腳,把所有二進制軟件從非易失性Nand閃存復制到SDRAM,大多數SDRAM資源將用于運行應用代碼,最大速度為166Mhz,如果在SDRAM上添加幀或者數據緩沖區,速度會很慢。MCU上還可用的接口是使用HyperRam。在MIMXRT1064CVL5B的參考手冊中,FlexSPI 模塊支持HyperBus 器件(HyperFlash / HyperRAM)。可以使用 I.MX Pins配置工具進行管腳和時鐘配置。

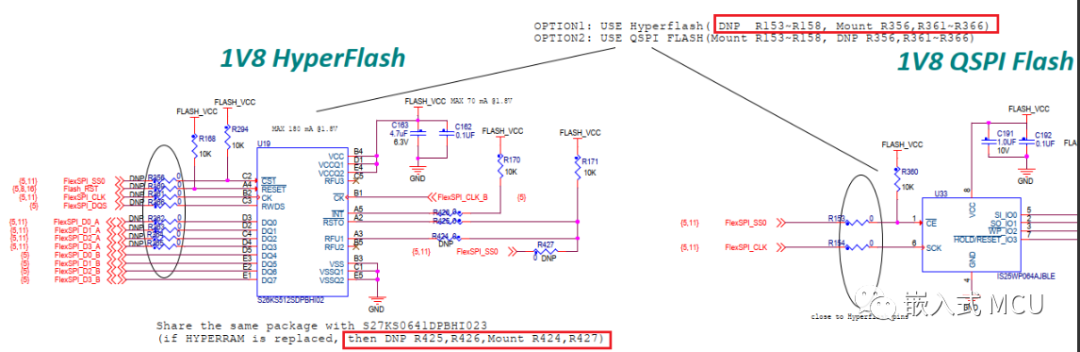

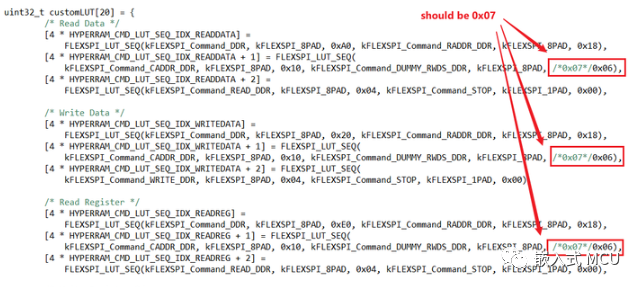

使用S27KL0642DP為3.0V HyperRAM,不適用于1V8 HyperFlash,RT1060-EVK開發板中的默認FLASH_VCC為1V8,如果要使用S27KL0642DP,則應將FLASH_VC更改為3V。或者將HyperRAM更改為S27KS0642DP。S27KL0642DP的冗余時鐘數為7。

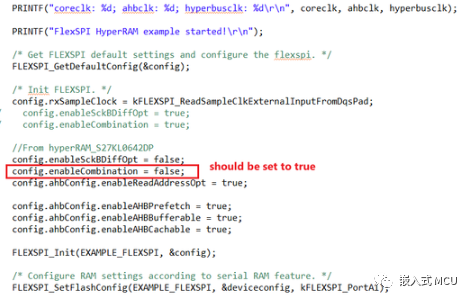

需要啟用 combination。

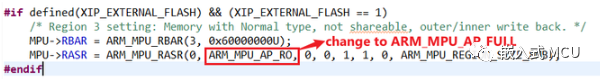

另外的 MPU 配置,設置存儲器 0x60000000 為 ARM_MPU_AP_FULL,如下圖所示。

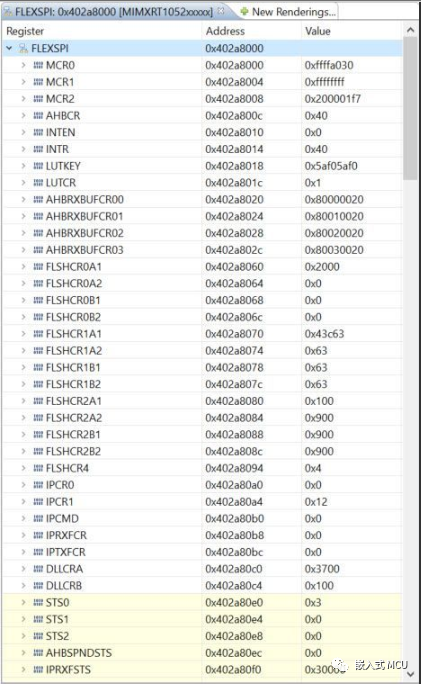

可以從調試器中獲取 FlexSPI寄存器的狀態。

不管應用程序如何使用內存,都能夠在HyperRAM中啟用不可緩存區域。雖然在HyperRAM中配置不可緩存內存沒有問題,禁用緩存的外部內存性能將大大降低。需要仔細考慮如何在應用程序中使用它。例如,與USB或網口一起使用。在MCU中的多個主機之間共享RAM確實需要一個不可緩存區域,因為緩存僅由內核使用。因此,USB端點緩沖區或由內核以外的主機更新的任何RAM都應該是不可緩存的。理想情況下,內部OCRAM將用于這些共享RAM,因為它比外部存儲器的性能高得多。特別是對于高速USB或任何需要RAM高性能的主機,使用較慢的外部RAM可能會導致一些帶寬/延遲問題。通常,這些與其他主機共享的RAM較小,非常適合放置在內部OCRAM中。

此外,由于堆棧一直在使用,并且經常是非線性訪問,因此存儲在非緩存的外部內存中可能會對應用程序的性能產生影響。堆棧僅由內核主機使用。理想情況下,堆棧將放置在DTCM中。或者,如果它們不適合DTCM,那么使用緩存的OCRAM或外部內存將優化性能。

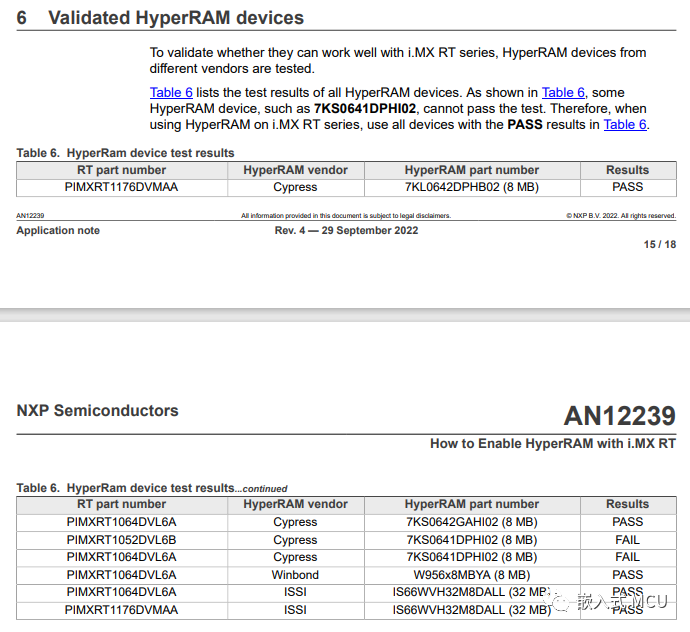

在AN12239里面提到了測試驗證過的 HyperRAM列表。

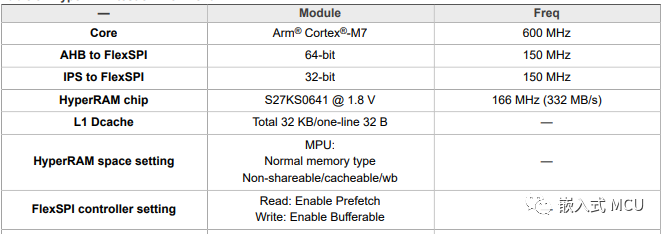

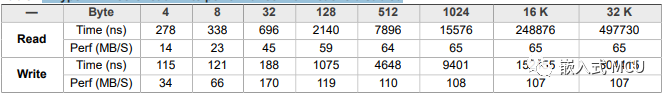

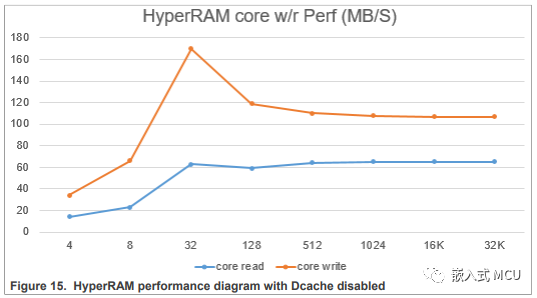

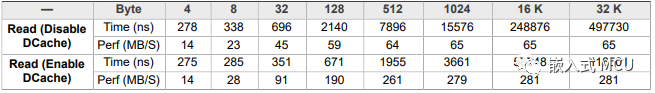

實際測試,當Cached禁止的時候,HyperRAM寫測試比讀操作性能更高。HyperRAM 讀/寫性能(Dcache禁止)

一些配置可能會影響HyperRAM性能:

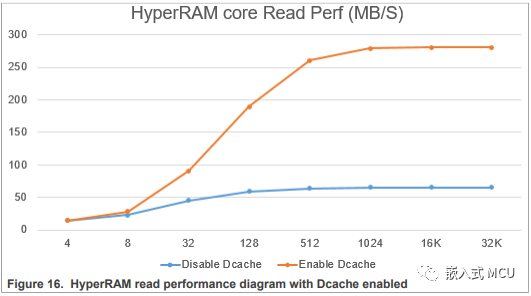

緩存影響——RT1060支持最大32K DCACHE和32K ICACHE,啟用緩存后可以進一步提高性能。

預取緩沖區影響——RT1060支持1024KB的預取緩沖區,其策略如下:

可為指定的主控或多個主控配置共享同一緩沖區。自動將數據預取到緩沖區,直到緩沖區已滿。檢查是否命中預取地址范圍,如果超出范圍,則從FlexSPI 器件觸發新的讀取操作,否則,如果它已經在預取緩沖區中,則從AHB緩沖區讀取,如果沒有,則等待預取數據到緩沖區。

因此,需根據應用做不同的配置。如果每次數據訪問都很小,并且訪問地址不連續,建議設置較小的預取緩沖區大小。如果是連續地址訪問,建議設置大的預取緩沖區大小。從HyperRAM測試性能來看,有以下建議:啟用Cache緩存以進一步提高HyperRAM性能。

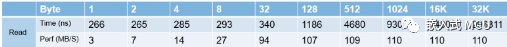

如下是 SDRAM(使能 Cache)測試數據:

如下是 Hyper RAM(使能Cache)測試數據:

HyperRAM性能與SDRAM相比,SDRAM讀取吞吐量(ARM內核讀取)比HyperRAM慢。HyperRAM MPU配置:( non-shareable,Cacheable,Write back,使能 Dcache)。另外從內存性能來看,SDRAM/Hyper RAM/HyperFlash/Octal Flash幾乎具有類似的性能,需要平衡ARM內核和DMA訪問超RAM 時隙,可以更改NIC-301SIM-M7寄存器以設置ARM內核和DMA訪問優先級。

-

mcu

+關注

關注

146文章

16520瀏覽量

346722 -

NXP

+關注

關注

60文章

1239瀏覽量

180597 -

HyperRAM

+關注

關注

0文章

4瀏覽量

1464

原文標題:MIMXRT1064CVL5B 連接 HyperRAM

文章出處:【微信號:嵌入式 MCU,微信公眾號:嵌入式 MCU】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

NXP品牌MCU系列最新優勢到貨型號:LPC4320FBD144,MCIMX6Y2CVM08AB,MIMXRT1051CVL5B等型號

如何搭建NXP MIMXRT1052CVL5B + 正點原子 + MCUXpresso IDE的開發環境?

MIMXRT1061CVL5B在斷電然后上電后,微控制器無法啟動的原因?

如何下載MIMXRT1051CVL5B的IAR IDE SDK?

PIMXRT1064DVL6A的MIMXRT1064-EVK板溫度怎么可能比環境溫度低這么多?

如何為 i.MIMXRT1064 EVK啟用ETM(嵌入式跟蹤宏單元)功能?

如何在MIMXRT1064評估套件上部署tflite模型?

如何使用MCUXpresso安全配置工具通過UART閃存MIMXRT1064?

將非緩存數據放在HyperRAM中有什么問題嗎?

MiMXRt1064 -EVK停止調試并報錯的原因?

MIMXRT1051CVL5B MCU不喚醒的原因?

MIMXRT1051CVL5B VDD_USB_CAP 引腳浮動,是否有任何東西可能損壞或無法正常工作嗎 ?

NXP MIMXRT1052CVL5B + 正點原子 + MCUXpresso IDE 開發環境搭建

MIMXRT1064CVL5B連接HyperRAM

MIMXRT1064CVL5B連接HyperRAM

評論