這兩年由于疫情,太過于動蕩,包括我們的FPGA,也由于市場、供應鏈、以及某些人的短期趨利問題,價格簡直上了天。

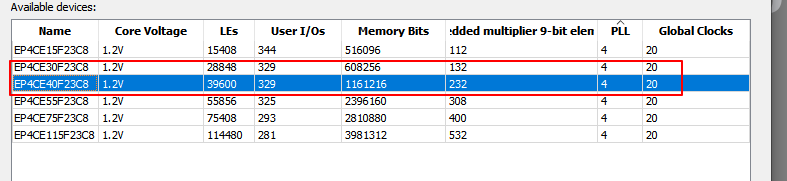

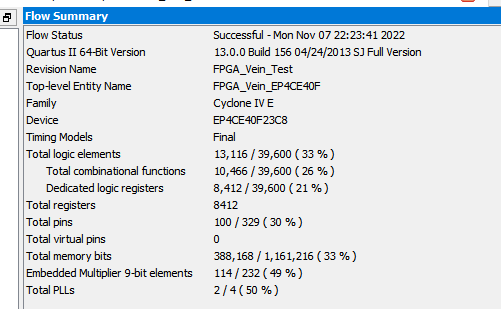

過去一個設計用了Altera的EP4CE30F23C8N,這款芯片幾乎是Altera性價比最高的芯片,并且他和EP4CE40F是同一個Die,因此熟悉門路的人知道,可以直接將EP4CE30F價格采購的芯片,當作EP4CE40F來用,瞬間資源倍增,如下圖所示,LE直接增加1/3,Memory和乘法器幾乎翻倍:

可惜是曾經可以用60-80RMB的零售價買到的EP4CE30F FPGA,由于這兩年的動蕩,以及供應鏈的轉移,10倍的價格也只能買到翻新的料了。或許Altera也可能已經放棄了中低端Cyclone IV系列FPGA,或者更多的將產能放到了高端Stratix FPGA上了。

那么我們就難了,原有的產品不能因此斷片,全新的EP4CE30幾乎需要幾千才能買得到,進退兩難,只能另謀出路,上帝給你關閉一扇門的同時,很有可能還會給你開另一扇門。

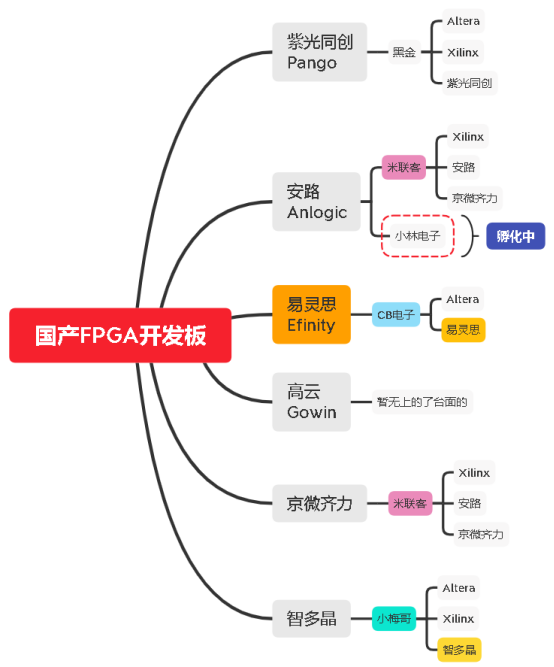

之前我寫過一篇公眾號,時隔10年,我將重新殺回國產FPGA,其中我列舉了當前國產FPGA的市場格局,如下圖所示:

我在這些選項中尋找尋找可以替代EP4CE30F的FPGA,希望這款FPGA可以滿足以下要求:

邏輯資源在30K左右

引腳在256-484之間

有豐富的Memory資源

可以運行在200MHz左右的頻率

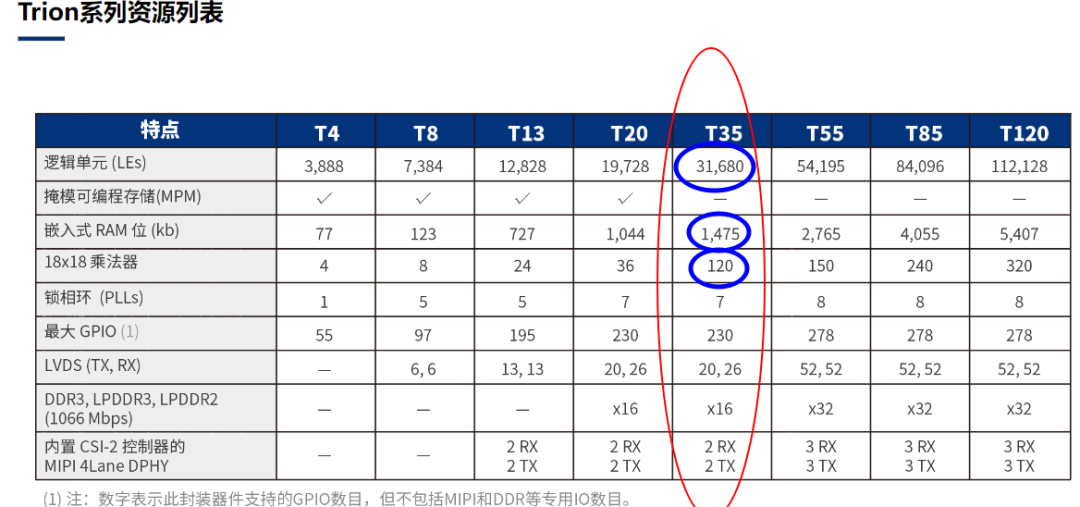

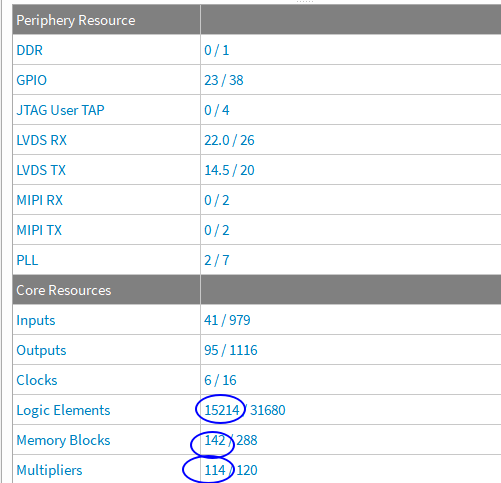

縱觀思維導圖,我找不到可以同時滿足以上5個要求,同時價格還可以和EP4CE30F不相上下的FPGA。直到有一天,Eric給我推薦了易靈思。易靈思有Trion和鈦金兩個系列,相比工藝Trion系列和Cyclone IV更貼近,同時第一次觀摩T35(35K LE)的內部資源,瞬間讓我找到了北,太滿足替代EP4CE30F的需求了,其資源如下。

尤其是乘法器的數量,在同等規格的國產FPGA中,我幾乎找不到能做到這么慷慨的,這給需要做一點圖像運算的我笑出了聲。

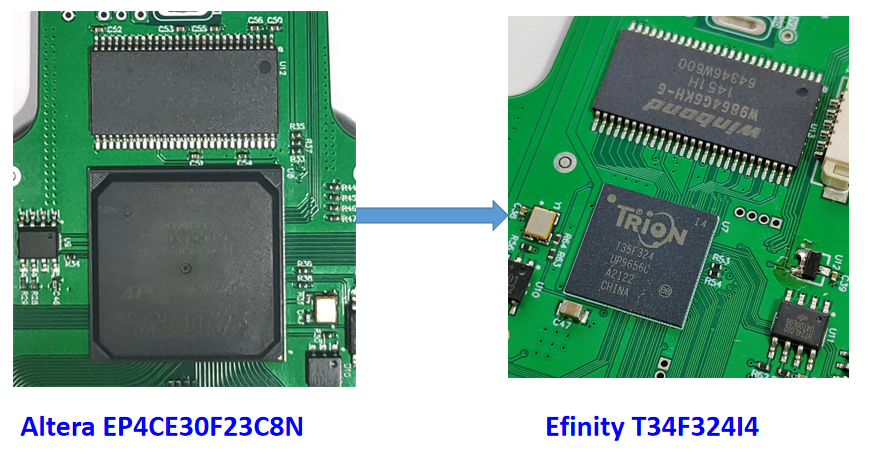

一直拖著,一直拖著,直到有一天,我確實被Altera的貨源逼瘋了,最終不得已,我下手將EP4CE30F給成了T35F324,即便是降低性能我不能讓設計承受50倍物料的成本,為此不惜代價。也感謝自己放棄了很久,最終還是堅持到了曙光,雖然這一路上的坎坷,真的不堪入目。

(一)軟件使用的艱難

這應該是使用國產FPGA,尤其是使用易靈思FPGA的同仁的心聲。細數目前國產FPGA的軟件開發環境,只有類Quartus和不類Quartus兩種,前者以紫光、安路為代表,換個環境根本不需要什么手冊教程;后者就是易靈思的Efinity,思路清奇,別具一格,用FAE的話說是:沒有他們的指導很難摸透(所以之前寫過一篇文章:骨骼清奇的易靈思FPGA-小試牛刀驅動LVDS屏)。

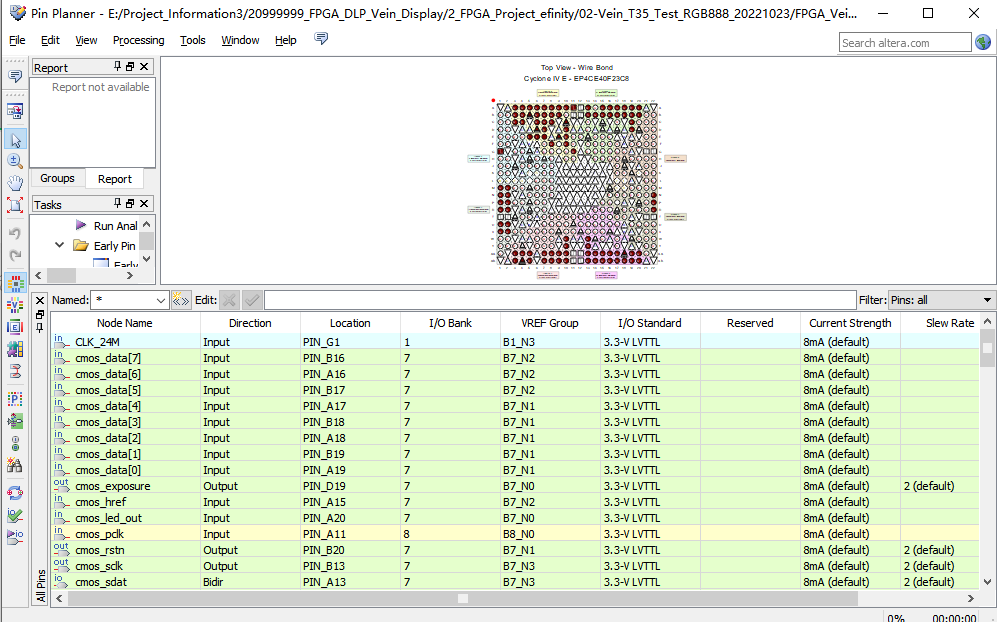

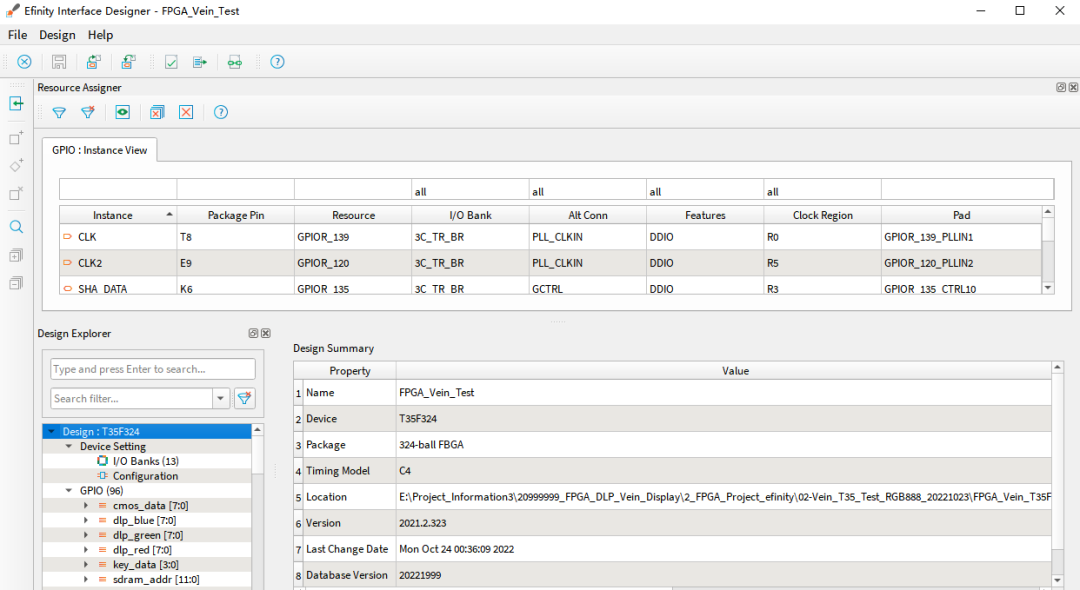

這過程確實浪費了不少的時間,包括Interface是純硬件的設計,到Design的物理連接是分離的,所以原先Altera的設計不能直接移植。同時RAM ROM使用LUT描述再映射RAM的方式,確實和之前直接用IP Core非常不一樣。這里以引腳分配為例,截圖為證:

(二)軟件綜合和PR的坑

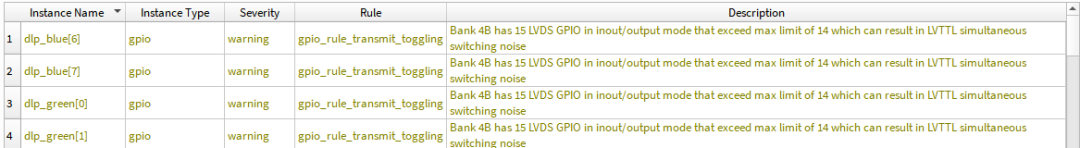

由于原本在設計中,采用ShiftRAM生成了41*41的窗口進行后續的圖像處理,因此簡單粗暴的有1681*8個寄存器,用于計算。但一模一樣的設計,在易靈思的Efinity中半天都無法綜合出結果,更別說PR,百思不得其解,最后只能花費巨大的精力,將按窗口的存儲修改成按照列的存儲模式,但是代價是需要復雜的邏輯以及主頻。下圖分別是Quartus與EfinityPR后的資源報表:

因此,這里不得不說國產FPGA的EDA工具鏈的重要性。在IC行業,EDA工具是被Synopsys、Cadence、Mentor三大家壟斷的,國產EDA目前還只是萌芽階段,這方面少說還有幾十年的差距。

FPGA行業也亦是如此,Quartus II的軟件是做的宇宙最好的,那是真的好用;Xilinx的Vivado是做的很強大甚至一個軟件30多G,強大到一時半會兒還學不會。國產FPGA的軟件,那簡直做的是一塌糊涂,到底是PR優先,還是時序有限,或者其綜合、PR算法,那真的不敢恭維,個人認為還是有很長的路要走。

不過易靈思的Efinity軟件,相對其他某幾家,做得還是不錯的。

(三)硬件設計的約束

這方面真的太難了,如果沒有FAE的支持,處處是坑。如果有FAE這根避雷針,很多時候可以避免掉坑里,畢竟爬出來還要很久。比如:

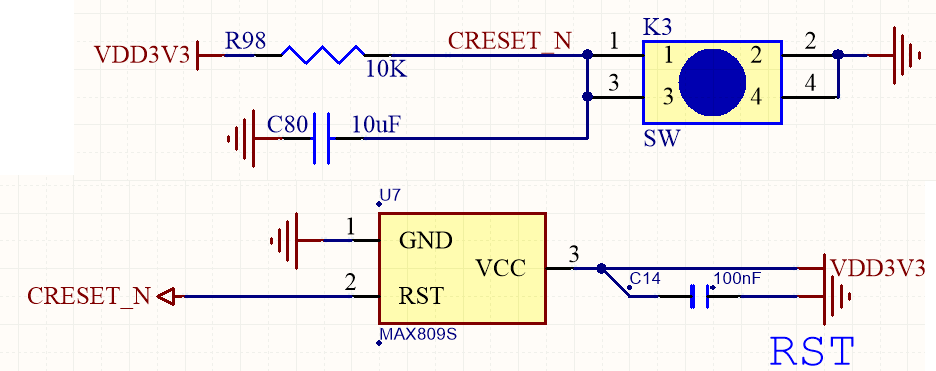

1)CRESET必須有上拉電阻+下拉電容,或者加一個復位芯片,否則無法正常啟動工作

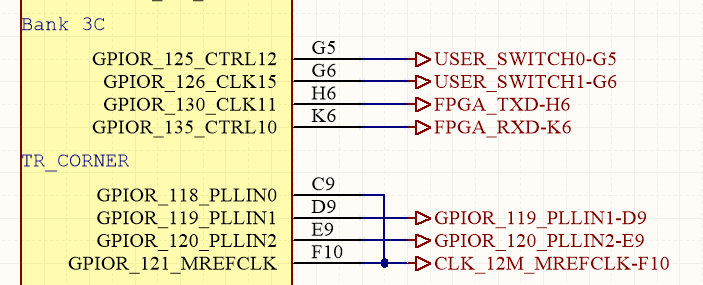

2)硬件設計的時候,有些GCLK輸入的時鐘可以去PLL,而有些GCLK輸入的時鐘只能直接使用。

那么問題來了,如果全局只有從PLL GCLK輸入的時鐘,如果我想先延時一段時間在釋放PLL的復位,那么就得用PLL之前輸入的時鐘,但是Efinity從PLL輸入的時鐘,不允許用戶直接拿來用,似乎是PLL專用的。。。所以這就很尷尬,強行使用,采用Efinify 2021編譯直接報錯,采用2022編譯會給出Warming,但流程可以繼續往下走,這就很尷尬了。

個人目前對Efinify的GCLK網絡結構還是有一點懵圈,不知道只有bug呢,還是有特別的妙招,反正現在使用受限。

3)一個BANK并不是所有IO都可用的,但用了也不會咋地,FAE又據說速度慢一點可以,但有時也真是有一些異常,官方有明確的答案嗎?

然后我現在確實有遇到一些神奇的問題,比如某一個一定時序啟動的設備,有概率性時間起不來,不知道是不是IO用多了的問題。

面積與功耗的優勢!!

但不得不說易靈思的FPGA,0.65mm的球間距,12*12mm的封裝尺寸,還有當前設計沒有用上的DDR硬核和MIPI CSI控制器,簡直是圖像領域FPGA設計的福音。

還有非常關鍵的一點,我們都知道Altera FPGA功耗比Xilinx FPGA的功耗做的好很多,但與易靈思FPGA相比;同等規模+同樣設計的Altera的功耗,還是做的略遜了一點。如下所示,同樣的系統+同樣的設計(后來用了同一套代碼),分別測試Altera與易靈思T35方案,實際的5V下電流,如下所示:

從原先的6.4W,到采用易靈思T35后降低到3.8W,幾乎降低了40%的功耗。并且這還是整機的功耗,如果單純評估FPGA的功耗,估計降了100%以上(系統中還有一個吃電的DLP光機)

至此,最近幾個月的易靈思FPGA項目實戰的坎坷精力,已經給大家匯報完畢,期間也是一把鼻涕一把淚,換方案想著簡單,做起來還是挺麻煩的。此處感謝易靈思T35,可以把物料成本上天的方案降低到合理水平,得以讓此繼續。也真心祝愿各位采用國產FPGA做替代的朋友,早點讓自己的設計安頓下來,找到一條可以走得更遠的路。

審核編輯 :李倩

-

FPGA

+關注

關注

1626文章

21670瀏覽量

601877 -

供應鏈

+關注

關注

3文章

1652瀏覽量

38830 -

易靈思

+關注

關注

5文章

45瀏覽量

4852

原文標題:易靈思FPGA做替代,到底有多難?

文章出處:【微信號:瘋狂的FPGA,微信公眾號:瘋狂的FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

lm2902做的二階低通濾波器,無論怎么調試C1的值,電路的波特圖都保持不變,請問一下C1的作用到底有多大?

易靈思RAM使用--Update5

國產FPGA應用專題--易靈思Efinity軟件使用心得

易靈思RAM使用--Update4

網線到底有多少種連接器

AD7280AWBSTZ和AD7280ABSTZ之間到底有什么區別?

COB與SMD到底有什么不同?

易靈思RAM使用--Update3

易靈思FPGA做替代,到底有多難?

易靈思FPGA做替代,到底有多難?

評論