RTL建模中的函數和任務(Function 和 task)

SystemVerilog的函數和任務可以將復雜的功能劃分為更小的、可重用的代碼塊。函數對于RTL建模非常有用,本文將對此進行研究。

任務雖然有自己的優勢,但在RTL模型中幾乎沒有價值。使用void函數(將在本節后面討論)是比使用任務更好的RTL編碼方式。因此,本文僅簡要討論任務。

函數和任務可以在使用它們的模塊或接口中定義。定義可以出現在調用函數或任務的語句之前或之后完成,函數和任務也可以在包中定義,然后導入到模塊或接口中,包導入語句必須出現在調用函數或任務之前。

函數

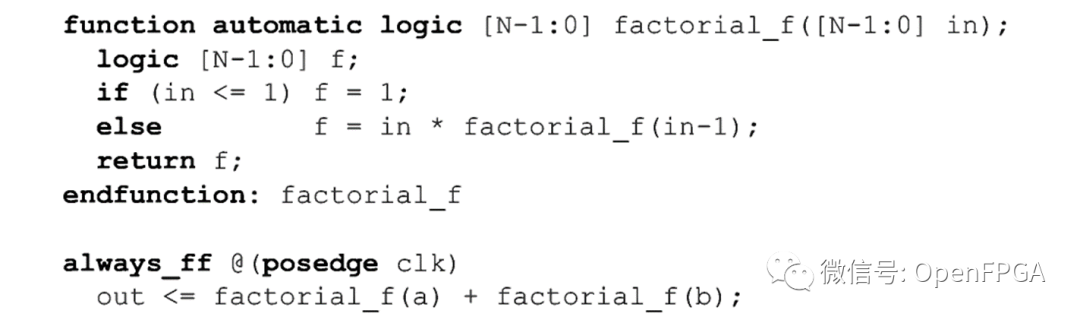

調用時,函數執行其編程語句并返回值。對函數的調用可以在任何可以使用表達式(如網絡或變量)的地方使用。這里展示了一個函數定義示例和對該函數的調用。本節后面將展示更實用的可綜合示例。

SystemVerilog語法要求函數在零仿真時間內執行。可綜合函數不能包含時鐘周期或傳播延遲。

靜態和自動(Static and automatic)函數。函數(和任務)可以聲明為靜態或自動。如果兩者都未指定,則模塊、接口或包中定義的函數的默認值為靜態。

靜態函數保留從一個調用到下一個調用的任何內部變量或存儲的狀態。函數名和函數輸入是隱式內部變量,在函數退出時將保留它們的值。

這種靜態存儲的效果是-對函數的新調用可以記住以前調用的值。這種“記憶性”在驗證代碼中很有用,但這種行為并不能準確地仿真綜合編譯器從函數實現的門級行為,這可能導致RTL模型仿真與ASIC或FPGA的實際功能不匹配。

自動函數在每次調用該函數時都會分配新的存儲。遞歸函數調用(如上文所示的 階乘f(factorial_f) 函數示例)需要自動存儲(兩個不同過程同時調用同一任務的可重入任務調用也需要自動存儲)

| 最佳實踐指南6-8 |

|---|

| 將RTL模型中使用的函數聲明為自動函數。 |

靜態存儲的默認設置不適用于硬件行為的RTL建模。此外,綜合編譯器要求包或接口中聲明的函數必須聲明為自動函數。

函數默認為靜態存儲是有歷史原因的。在Verilog仿真的最初幾年,當時計算機內存有限且處理器速度慢得多,靜態存儲有助于提高仿真運行時性能,與使用現代仿真器和計算服務器的自動存儲相比,靜態存儲沒有性能優勢。SystemVerilog標準保留了靜態函數的原始語言默認值,以便與遺留的驗證代碼保持向后兼容,這些代碼可能是為了利用函數的靜態存儲而編寫的。

函數返回。

函數的返回數據類型定義在函數名之前。在上面的 階乘f(factorial_f) 示例中,該函數返回一個N位寬的向量,其類型為logic(4-state)。如果未指定返回類型,則默認情況下,函數返回為1位logic(4-state)類型。

SystemVerilog提供了兩種指定函數返回值的方法。一種方法是使用return關鍵字,如上面的factorial_f示例所示。return關鍵字后面是函數要返回的值。或者,可以將此返回值括在括號中。

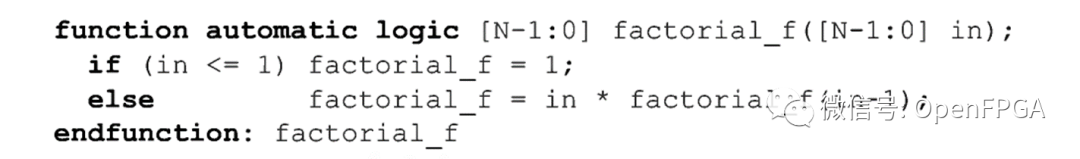

第二種指定返回值的方法是為函數名賦值。函數名是與返回值數據類型相同的隱式變量類型,當函數計算返回值時,此隱式變量可用于臨時存儲。分配給函數名的最后一個值將成為函數返回值。本節開頭顯示的 階乘f(factorial_f) 函數可以重新編碼,以使用函數名作為隱式內部變量來計算返回值。

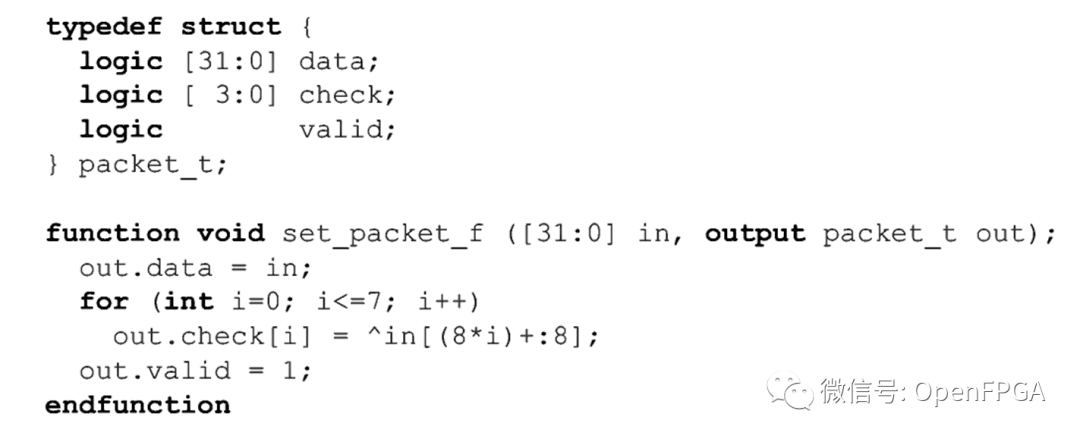

Void函數。

函數返回類型可以聲明為void。Void函數不返回值,不能像其他函數一樣用作表達式。void函數被稱為語句,而不是表達式。

| 最佳實踐指南6-9 |

|---|

| 使用void函數代替任務進行RTL建模。僅在驗證代碼中使用任務。 |

void函數和任務之間的唯一區別是函數必須在零時間內執行。大多數綜合編譯器不支持任務中任何形式的時鐘延遲。使用void函數代替任務使得這種綜合限制成為語法要求,并且可以防止編寫可以仿真但不可以綜合的RTL模型。

函數參數。函數定義中的參數稱為形式參數(formal arguments)。函數調用中的參數稱為實際參數(actual arguments)。形式參數可以是input、output或inout,并使用與模塊端口相同的語法聲明,默認方向(如果未定義)為input,上面fill_packet示例中的形式參數是32-bit 4-state輸入,用戶定義的packet_t類型的輸出形式參數。

形式參數也可以聲明為ref(reference的縮寫)代替端口方向(direction),ref參數是指向函數調用的實際參數的指針形式,函數必須聲明為自動函數(automaticfunction)才能使用ref參數。

| 最佳實踐指南6-10 |

|---|

| 在RTL模型中使用的函數中只使用輸入和輸出(input 和 output)形式參數,不要使用inout或ref形式參數。 |

所有RTL綜合編譯器都支持輸入和輸出(input 和 output)函數參數。某些RTL綜合編譯器不支持inout和ref參數。

調用函數。

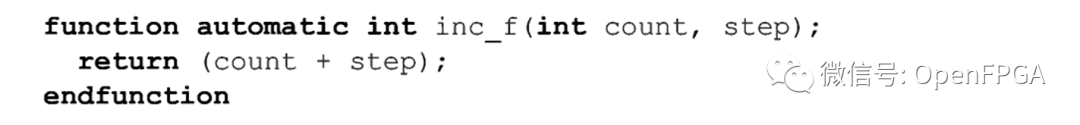

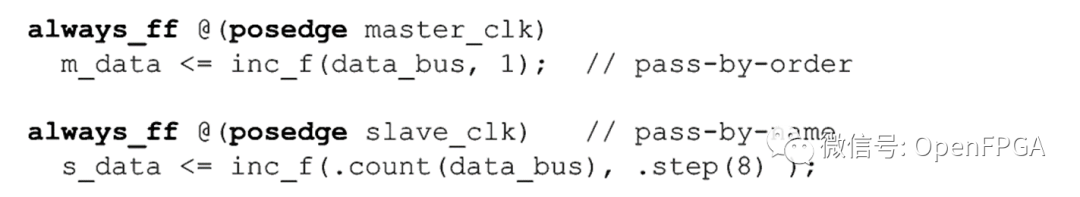

調用函數時,將實際參數傳遞給形式參數有兩種編碼樣式:按順序傳遞和按名稱傳遞。按順序傳遞時,第一個實際參數傳遞給第一個形式參數,第二個實際參數傳遞給第二個形式參數,依此類推。按名稱傳遞使用與按名稱連接模塊相同的語法。形式參數的名稱前面有逗號(.),后跟括號中的實際參數。

給定函數定義:

傳遞實際參數的兩種方式是:

函數輸入默認值。

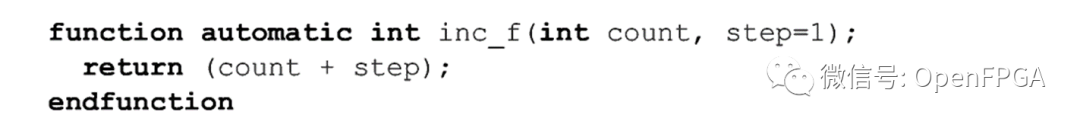

可以為形式參數指定默認值,如下所示:

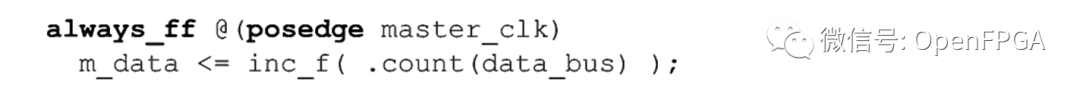

具有默認值的參數不需要傳遞實際參數,如果沒有傳遞實際參數,則使用默認值。例如:

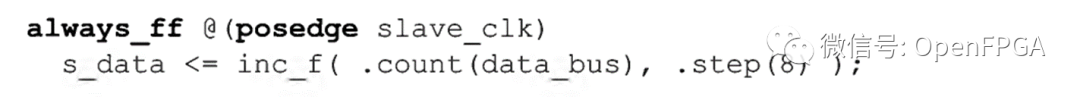

如果傳入實際值,則使用實際值,如下所示:

| 筆記 |

|---|

| 在編寫本文時,一些綜合編譯器不支持默認輸入值,工程師應該確保項目中使用的設計流程中的所有工具在RTL模型中使用之前都支持默認參數值。 |

使用return提前退出函數。

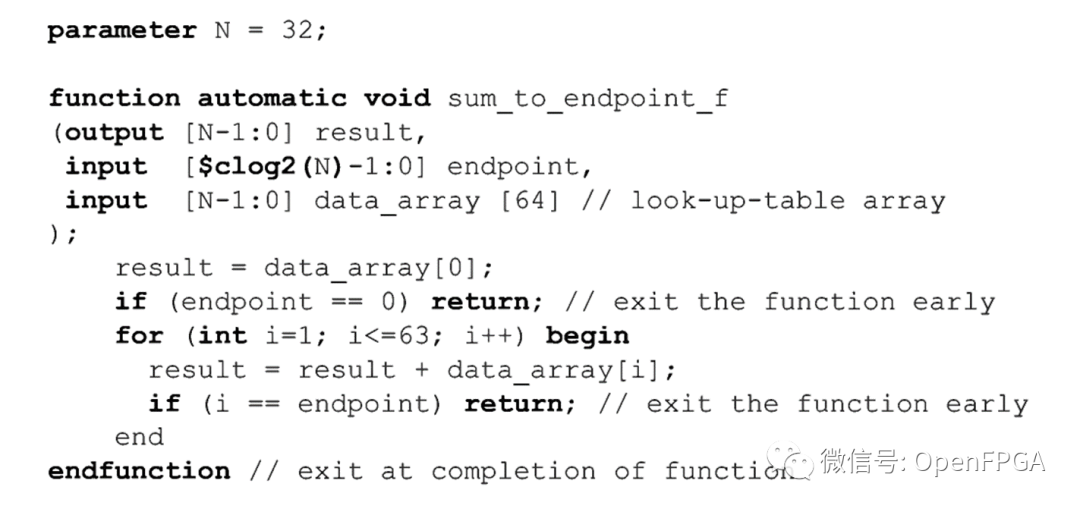

return語句也可以用于在函數中的所有語句都執行之前退出函數,下面的示例可以在3個不同的點退出函數。如果 max 輸入為0,則函數在執行for循環之前退出;如果for循環迭代器達到max值,則函數在到達循環末尾之前退出;如果for循環完成,則函數在到達endfunction時退出。

參數化函數(Parameterized function)。

參數化函數是SystemVerilog中功能強大且廣泛使用的功能。可以為模塊的每個實例重新定義參數,使模塊易于配置和重用。模塊級參數可以在函數定義中使用,如前面的sum_to_endpoint_f函數示例所示。使用模塊級參數意味著對函數的所有調用將具有相同的向量大小。如果調用函數的每個位置使用不同的向量大小,則無法對函數進行配置。

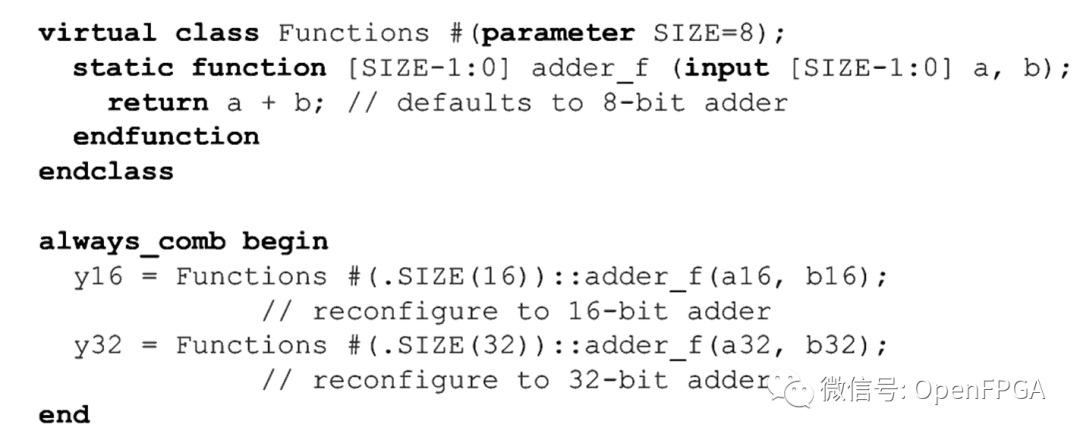

函數不能像模塊那樣進行參數化,SystemVerilog不允許函數定義具有內部參數,這些參數可以在調用函數的每個地方重新定義——這限制了編寫可重用、可配置函數的能力。但是,對于這個限制,有一個解決方法,即在參數化虛擬類中聲明靜態函數,可以使用范圍解析操作符(無需創建對象)直接調用類定義中的靜態函數。

在調用函數的每個地方,都可以重新定義類(class)參數,如下例所示:

參數化函數可以只創建和維護函數的一個版本,而不必定義具有不同數據類型、向量寬度或其他特征的多個版本。

請注意,在類定義中,static關鍵字位于function關鍵字之前,而在模塊中,static或automatic關鍵字位于function關鍵字之后。有一個重要的語義差異,在類中,靜態函數聲明類中函數的生存期,并限制函數在類中可以訪問的內容,在模塊中,靜態函數或自動函數指函數中參數和變量的生存期。

| 筆記 |

|---|

| 在寫這本文的時候,并不是所有的綜合編譯器都支持參數化虛擬類中的靜態函數。在RTL模型中使用靜態函數之前,工程師應該確保項目中使用的所有工具都支持參數化虛擬類中的靜態函數。 |

任務-Task

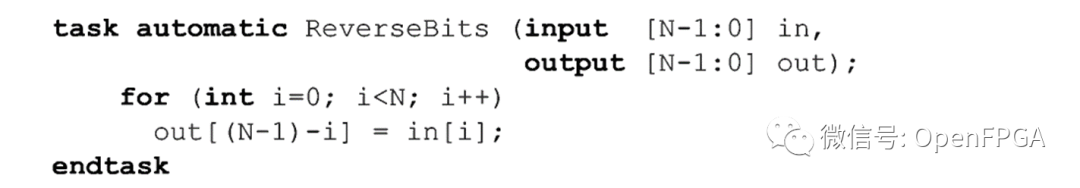

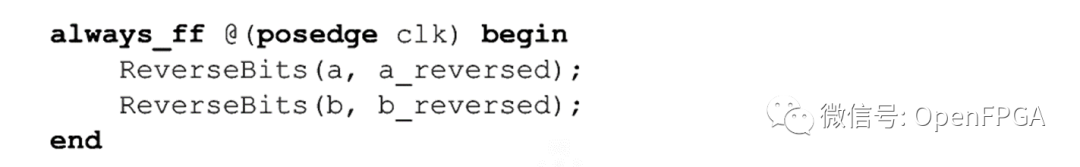

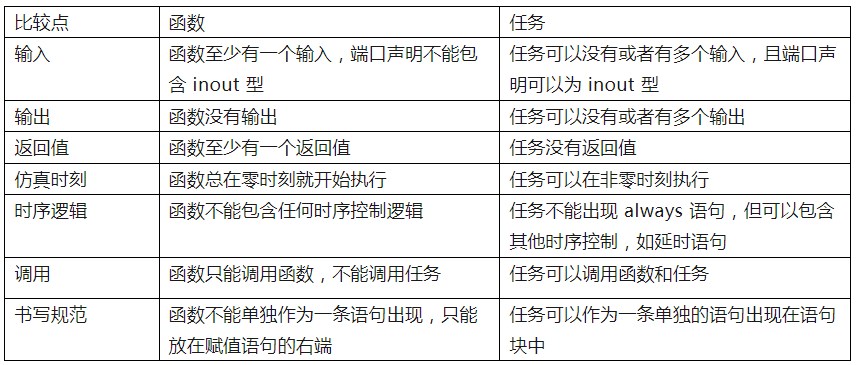

任務是封裝一條或多條編程語句的子例程,因此可以從不同的位置調用封裝的語句,或在其他項目中重用。與函數不同,任務沒有返回值。一個例子是:

任務被稱為編程語句,并使用輸出形式參數從任務中傳遞值。

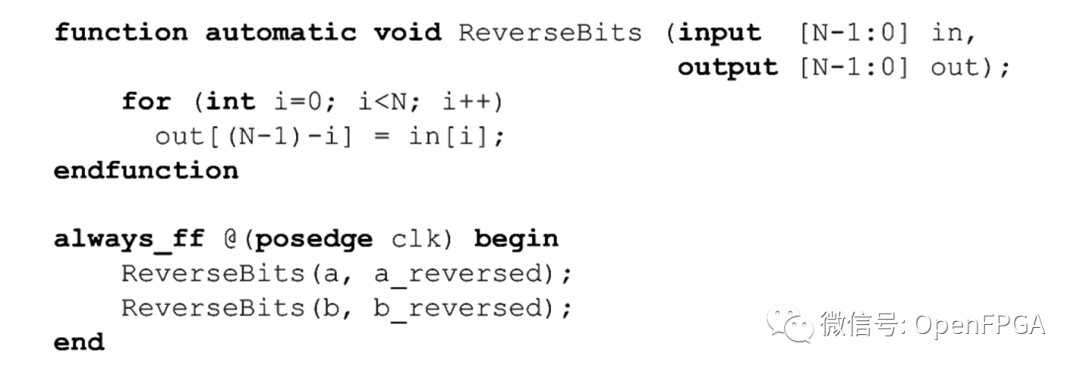

語法上;任務與函數非常相似,只是任務沒有返回類型。任務和函數之間的一個重要區別是,任務可能包含時鐘周期和傳播延遲。然而,大多數綜合編譯器要求任務中的編程語句在零仿真時間內運行。這種綜合限制使任務幾乎與void函數相同,因為void函數在語法上強制零時間執行,所以最佳編碼實踐是在RTL模型中需要子例程時使用void函數而不是任務。上面的ReverseBits任務可以重寫為void函數,如下所示:

審核編輯:劉清

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602037 -

asic

+關注

關注

34文章

1195瀏覽量

120348 -

RTL

+關注

關注

1文章

385瀏覽量

59710

原文標題:SystemVerilog-Function 和 task

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

S函數建模和仿真過程的研究

如何在Zstack中實現自己的任務詳細分析和函數資料概述

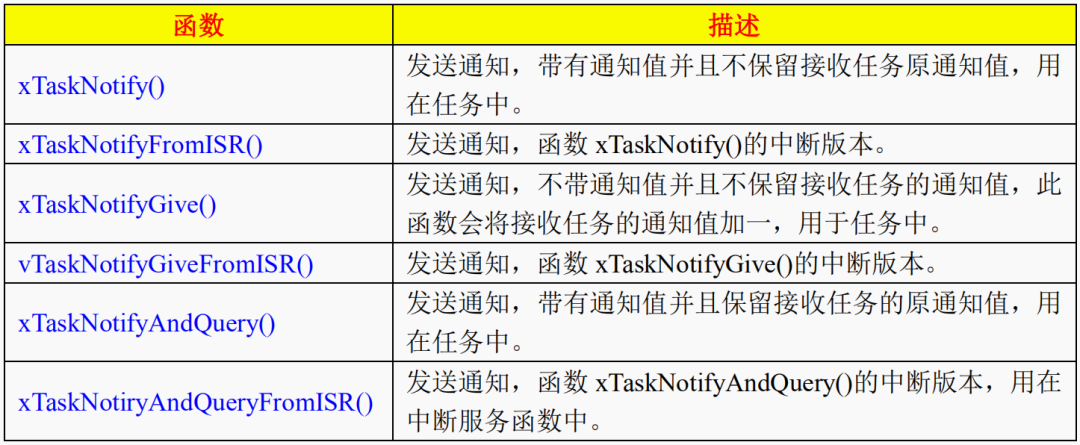

FreeRTOS任務應用函數介紹

FreeRTOS系列第12篇---FreeRTOS任務應用函數

Verilog設計中函數和任務的作用分析

如何使用Arduino millis函數執行多任務處理

RTL建模中的函數和任務討論

RTL建模中的函數和任務討論

評論