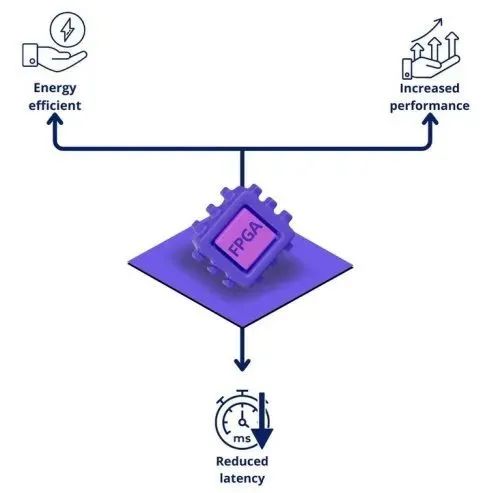

FPGA可用于處理多元計(jì)算密集型任務(wù),依托流水線并行結(jié)構(gòu)體系,F(xiàn)PGA相對(duì)GPU、CPU在計(jì)算結(jié)果返回時(shí)延方面具備技術(shù)優(yōu)勢(shì)。

計(jì)算密集型任務(wù):矩陣運(yùn)算、機(jī)器視覺、圖像處理、搜索引擎排序、非對(duì)稱加密等類型的運(yùn)算屬于計(jì)算密集型任務(wù)。該類運(yùn)算任務(wù)可由CPU卸載至FPGA執(zhí)行。

FPGA執(zhí)行計(jì)算密集型任務(wù)性能表現(xiàn):

? 計(jì)算性能相對(duì)CPU:如Stratix系列FPGA進(jìn)行整數(shù)乘法運(yùn)算,其性能與20核CPU相當(dāng),進(jìn)行浮點(diǎn)乘法運(yùn)算,其性能與8核CPU相當(dāng)。

? 計(jì)算性能相對(duì)GPU:FPGA進(jìn)行整數(shù)乘法、浮點(diǎn)乘法運(yùn)算,性能相對(duì)GPU存在數(shù)量級(jí)差距,可通過配置乘法器、浮點(diǎn)運(yùn)算部件接近GPU計(jì)算性能。

FPGA執(zhí)行計(jì)算密集型任務(wù)核心優(yōu)勢(shì):搜索引擎排序、圖像處理等任務(wù)對(duì)結(jié)果返回時(shí)限要求較為嚴(yán)格,需降低計(jì)算步驟時(shí)延。傳統(tǒng)GPU加速方案下數(shù)據(jù)包規(guī)模較大,時(shí)延可達(dá)毫秒級(jí)別。FPGA加速方案下,PCIe時(shí)延可降至微秒級(jí)別。遠(yuǎn)期技術(shù)推動(dòng)下,CPU與FPGA數(shù)據(jù)傳輸時(shí)延可降至100納秒以下。

FPGA可針對(duì)數(shù)據(jù)包步驟數(shù)量搭建同等數(shù)量流水線(流水線并行結(jié)構(gòu)),數(shù)據(jù)包經(jīng)多個(gè)流水線處理后可即時(shí)輸出。GPU數(shù)據(jù)并行模式依托不同數(shù)據(jù)單元處理不同數(shù)據(jù)包,數(shù)據(jù)單元需一致輸入、輸出。針對(duì)流式計(jì)算任務(wù),F(xiàn)PGA流水線并行結(jié)構(gòu)在延遲方面具備天然優(yōu)勢(shì)。

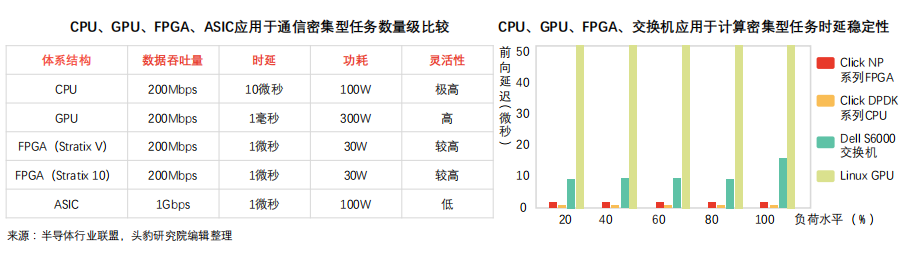

FPGA用于處理通信密集型任務(wù)不受網(wǎng)卡限制,在數(shù)據(jù)包吞吐量、時(shí)延方面表現(xiàn)優(yōu)于CPU方案,時(shí)延穩(wěn)定性較強(qiáng)。

通信密集型任務(wù):對(duì)稱加密、防火墻、網(wǎng)絡(luò)虛擬化等運(yùn)算屬于通信密集型計(jì)算任務(wù),通信密集數(shù)據(jù)處理相對(duì)計(jì)算密集數(shù)據(jù)處理復(fù)雜度較低,易受通信硬件設(shè)備限制。

FPGA執(zhí)行通信密集型任務(wù)優(yōu)勢(shì):

① 吞吐量?jī)?yōu)勢(shì):CPU方案處理通信密集任務(wù)需通過網(wǎng)卡接收數(shù)據(jù),易受網(wǎng)卡性能限制(線速處理64字節(jié)數(shù)據(jù)包網(wǎng)卡有限,CPU及主板PCIe網(wǎng)卡插槽數(shù)量有限)。GPU方案(高計(jì)算性能)處理通信密集任務(wù)數(shù)據(jù)包缺乏網(wǎng)口,需依靠網(wǎng)卡收集數(shù)據(jù)包,數(shù)據(jù)吞吐量受CPU及網(wǎng)卡限制,時(shí)延較長(zhǎng)。FPGA可接入40Gbps、100Gbps網(wǎng)線,并以線速處理各類數(shù)據(jù)包,可降低網(wǎng)卡、交換機(jī)配置成本。

② 時(shí)延優(yōu)勢(shì):CPU方案通過網(wǎng)卡收集數(shù)據(jù)包,并將計(jì)算結(jié)果發(fā)送至網(wǎng)卡。受網(wǎng)卡性能限制,DPDK數(shù)據(jù)包處理框架下,CPU處理通信密集任務(wù)時(shí)延近5微秒,且CPU時(shí)延穩(wěn)定性較弱,高負(fù)載情況下時(shí)延或超過幾十微秒,造成任務(wù)調(diào)度不確定性。FPGA無需指令,可保證穩(wěn)定、極低時(shí)延,F(xiàn)PGA協(xié)同CPU異構(gòu)模式可拓展FPGA方案在復(fù)雜端設(shè)備的應(yīng)用。

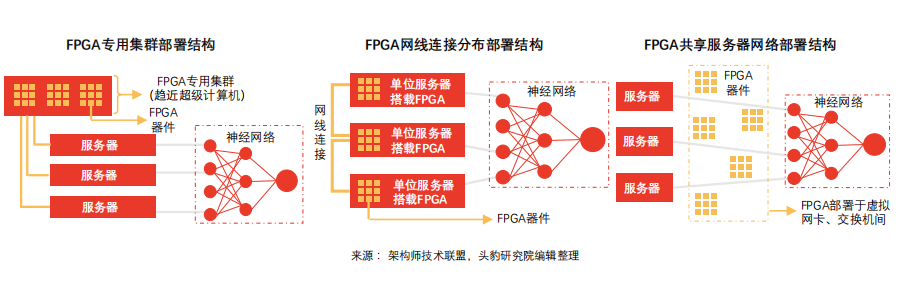

FPGA部署包括集群式、分布式等,逐漸從中心化過渡至分布式,不同部署方式下,服務(wù)器溝通效率、故障傳導(dǎo)效應(yīng)表現(xiàn)各異。

FPGA嵌入功耗負(fù)擔(dān):FPGA嵌入對(duì)服務(wù)器整體功耗影響較小,以Catapult聯(lián)手微軟開展的FPGA加速機(jī)器翻譯項(xiàng)目為例,加速模塊整體總計(jì)算能力達(dá)到103Tops/W,與10萬塊GPU計(jì)算能力相當(dāng)。相對(duì)而言,嵌入單塊FPGA導(dǎo)致服務(wù)器整體功耗增加約30W。

FPGA部署方式特點(diǎn)及限制:

① 集群部署特點(diǎn)及限制:FPGA芯片構(gòu)成專用集群,形成FPGA加速卡構(gòu)成的超級(jí)計(jì)算器(如Virtex系列早期實(shí)驗(yàn)板于同一硅片部署6塊FPGA,單位服務(wù)器搭載4塊實(shí)驗(yàn)板)。

? 專用集群模式無法在不同機(jī)器FPGA之間實(shí)現(xiàn)通信;

? 數(shù)據(jù)中心其他機(jī)器需集中發(fā)送任務(wù)至FPGA集群,易造成網(wǎng)絡(luò)延遲;

? 單點(diǎn)故障導(dǎo)致數(shù)據(jù)中心整體加速能力受限

② 網(wǎng)線連接分布部署:為保證數(shù)據(jù)中心服務(wù)器同構(gòu)性(ASIC解決方案亦無法滿足),該部署方案于不同服務(wù)器嵌入FPGA,并通過專用網(wǎng)絡(luò)連接,可解決單點(diǎn)故障傳導(dǎo)、網(wǎng)絡(luò)延遲等問題。

?類同于集群部署模式,該模式不支持不同機(jī)器FPGA間通信;

?搭載FPGA芯片的服務(wù)器具備高度定制化特點(diǎn),運(yùn)維成本較高

③ 共享服務(wù)器網(wǎng)絡(luò)部署:該部署模式下,F(xiàn)PGA置于網(wǎng)卡、交換機(jī)間,可大幅提高加速網(wǎng)絡(luò)功能并實(shí)現(xiàn)存儲(chǔ)虛擬化。FPGA針對(duì)每臺(tái)虛擬機(jī)設(shè)置虛擬網(wǎng)卡,虛擬交換機(jī)數(shù)據(jù)平面功能移動(dòng)至FPGA內(nèi),無需CPU或物理網(wǎng)卡參與網(wǎng)絡(luò)數(shù)據(jù)包收發(fā)過程。該方案顯著提升虛擬機(jī)網(wǎng)絡(luò)性能(25Gbps),同時(shí)可降低數(shù)據(jù)傳輸網(wǎng)絡(luò)延遲(10倍)。

分享服務(wù)器網(wǎng)絡(luò)部署模式下,F(xiàn)PGA加速器有助于降低數(shù)據(jù)傳輸時(shí)延,維護(hù)數(shù)據(jù)中心時(shí)延穩(wěn)定,顯著提升虛擬機(jī)網(wǎng)絡(luò)性能。

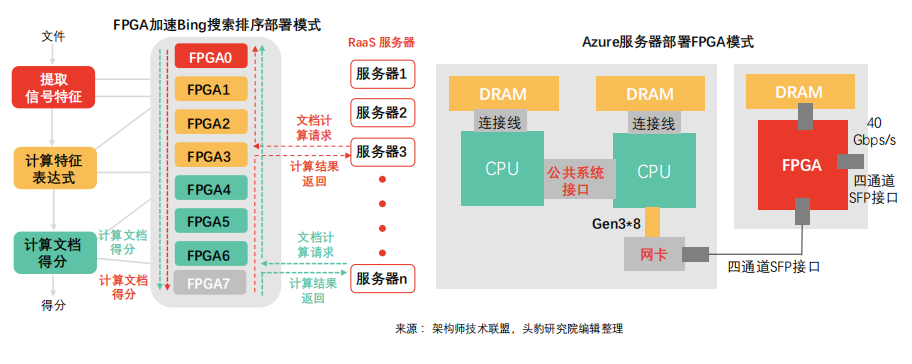

分享服務(wù)器網(wǎng)絡(luò)部署模式下FPGA加速Bing搜索排序:Bing搜索排序于該模式下采用10Gbps專用網(wǎng)線通信,每組網(wǎng)絡(luò)由8個(gè)FPGA組成。其中,部分負(fù)責(zé)提取信號(hào)特征,部分負(fù)責(zé)計(jì)算特征表達(dá)式,部分負(fù)責(zé)計(jì)算文檔得分,最終形成機(jī)器人即服務(wù)(RaaS)平臺(tái)。FPGA加速方案下,Bing搜索時(shí)延大幅降低,延遲穩(wěn)定性呈現(xiàn)正態(tài)分布。該部署模式下,遠(yuǎn)程FPGA通信延遲相對(duì)搜索延遲可忽略。

Azure服務(wù)器部署FPGA模式:Azure針對(duì)網(wǎng)絡(luò)及存儲(chǔ)虛擬化成本較高等問題采取FPGA分享服務(wù)器網(wǎng)絡(luò)部署模式。隨網(wǎng)絡(luò)計(jì)算速度達(dá)到40Gbps,網(wǎng)絡(luò)及存儲(chǔ)虛擬化CPU成本激增(單位CPU核僅可處理100Mbps吞吐量)。通過在網(wǎng)卡及交換機(jī)間部署FPGA,網(wǎng)絡(luò)連接擴(kuò)展至整個(gè)數(shù)據(jù)中心。通過輕量級(jí)傳輸層,同一服務(wù)器機(jī)架時(shí)延可控制在3微秒內(nèi),觸達(dá)同數(shù)據(jù)中心全部FPGA機(jī)架時(shí)延可控制在20微秒內(nèi)。

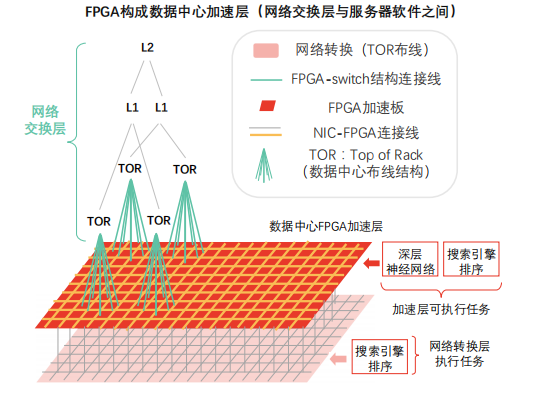

依托高帶寬、低時(shí)延優(yōu)勢(shì),F(xiàn)PGA可組成網(wǎng)絡(luò)交換層與服務(wù)器軟件之間的數(shù)據(jù)中心加速層,并隨分布式加速器規(guī)模擴(kuò)大實(shí)現(xiàn)性能超線性提升。

數(shù)據(jù)中心加速層:FPGA嵌入數(shù)據(jù)中心加速平面,位于網(wǎng)絡(luò)交換層(支架層、第一層、第二層)及傳統(tǒng)服務(wù)器軟件(CPU層面運(yùn)行軟件)之間。

加速層優(yōu)勢(shì):

? FPGA加速層負(fù)責(zé)為每臺(tái)服務(wù)器(提供云服務(wù))提供網(wǎng)絡(luò)加速、存儲(chǔ)虛擬化加速支撐,加速層剩余資源可用于深度神經(jīng)網(wǎng)絡(luò)(DNN)等計(jì)算任務(wù)。

? 隨分布式網(wǎng)絡(luò)模式下FPGA加速器規(guī)模擴(kuò)大,虛擬網(wǎng)絡(luò)性能提升呈現(xiàn)超線性特征。

加速層性能提升原理:使用單塊FPGA時(shí),單片硅片內(nèi)存不足以支撐全模型計(jì)算任務(wù),需持續(xù)訪問DRAM以獲取權(quán)重,受制于DRAM性能。加速層通過數(shù)量眾多的FPGA支撐虛擬網(wǎng)絡(luò)模型單層或單層部分計(jì)算任務(wù)。該模式下,硅片內(nèi)存完整加載模型權(quán)重,可突破DRAM性能瓶頸,F(xiàn)PGA計(jì)算性能得到充分發(fā)揮。加速層需避免計(jì)算任務(wù)過度拆分而導(dǎo)致計(jì)算、通信失衡。

嵌入式eFPGA技術(shù)在性能、成本、功耗、盈利能力等方面優(yōu)于傳統(tǒng)FPGA嵌入方案,可針對(duì)不同應(yīng)用場(chǎng)景、不同細(xì)分市場(chǎng)需求提供靈活解決方案.

eFPGA技術(shù)驅(qū)動(dòng)因素:設(shè)計(jì)復(fù)雜度提升伴隨設(shè)備成本下降的經(jīng)濟(jì)趨勢(shì)促發(fā)市場(chǎng)對(duì)eFPGA技術(shù)需求。

器件設(shè)計(jì)復(fù)雜度提升:SoC設(shè)計(jì)實(shí)現(xiàn)過程相關(guān)軟件工具趨于復(fù)雜(如Imagination Technologies為滿足客戶完整開發(fā)解決方案需求而提供PowerVR圖形界面、Eclipse整合開發(fā)環(huán)境),工程耗時(shí)增加(編譯時(shí)間、綜合時(shí)間、映射時(shí)間,F(xiàn)PGA規(guī)模越大,編譯時(shí)間越長(zhǎng))、制模成本提高(FPGA芯片成本為同規(guī)格ASIC芯片成本100倍)。

設(shè)備單位功能成本持續(xù)下降:20世紀(jì)末期,F(xiàn)PGA平均售價(jià)較高(超1,000元),傳統(tǒng)模式下,F(xiàn)PGA與ASIC集成設(shè)計(jì)導(dǎo)致ASIC芯片管芯面積、尺寸增大,復(fù)雜度提升,早期混合設(shè)備成本較高。21世紀(jì),相對(duì)批量生產(chǎn)的混合設(shè)備,F(xiàn)PGA更多應(yīng)用于原型設(shè)計(jì)、預(yù)生產(chǎn)設(shè)計(jì),成本相對(duì)傳統(tǒng)集成持續(xù)下降(最低約100元),應(yīng)用靈活。eFPGA技術(shù)優(yōu)勢(shì):

更優(yōu)質(zhì):eFPGA IP核及其他功能模塊的SoC設(shè)計(jì)相對(duì)傳統(tǒng)FPGA嵌入ASIC解決方案,在功耗、性能、體積、成本等方面表現(xiàn)更優(yōu)。

更方便:下游應(yīng)用市場(chǎng)需求更迭速度快,eFPGA可重新編程特性有助于設(shè)計(jì)工程師更新SoC,產(chǎn)品可更長(zhǎng)久占有市場(chǎng),利潤(rùn)、收入、盈利能力同時(shí)大幅提升。eFPGA方案下SoC可實(shí)現(xiàn)高效運(yùn)行,一方面迅速更新升級(jí)以支持新接口標(biāo)準(zhǔn),另一方面可快速接入新功能以應(yīng)對(duì)細(xì)分化市場(chǎng)需求。

更節(jié)能:SoC設(shè)計(jì)嵌入eFPGA技術(shù)可在提高總性能的同時(shí)降低總功耗。利用eFPGA技術(shù)可重新編程特性,工程師可基于硬件,針對(duì)特定問題對(duì)解決方案進(jìn)行重新配置,進(jìn)而提高設(shè)計(jì)性能、降低功耗。

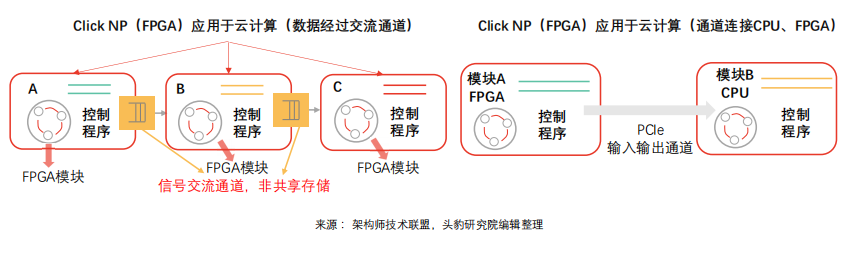

FPGA技術(shù)無需依靠指令、無需共享內(nèi)存,在云計(jì)算網(wǎng)絡(luò)互連系統(tǒng)中提供低延遲流式通信功能,可廣泛滿足虛擬機(jī)之間、進(jìn)程之間加速需求.

FPGA云計(jì)算任務(wù)執(zhí)行流程:主流數(shù)據(jù)中心以FPGA為計(jì)算密集型任務(wù)加速卡,賽靈思及阿爾特拉推出基于OpenCL的高層次編程模型,模型依托CPU觸達(dá)DRAM,向FPGA傳輸任務(wù),通知執(zhí)行,F(xiàn)PGA完成計(jì)算并將執(zhí)行結(jié)果傳輸至DRAM,最終傳輸至CPU。

FPGA云計(jì)算性能升級(jí)空間:受限于工程實(shí)現(xiàn)能力,當(dāng)前數(shù)據(jù)中心FPGA與CPU之間通信多以DRAM為中介,通過燒寫DRAM、啟動(dòng)kernel、讀取DRAM的流程完成通信(FPGADRAM相對(duì)CPU DRAM數(shù)據(jù)傳輸速度較慢),時(shí)延近2毫秒(OpenCL、多個(gè)kernel間共享內(nèi)存)。CPU與FPGA間通信時(shí)延存在升級(jí)空間,可借助PCIe DMA實(shí)現(xiàn)高效直接通信,時(shí)延最低可降至1微秒。

FPGA云計(jì)算通信調(diào)度新型模式:新通信模式下,F(xiàn)PGA與CPU無需依托共享內(nèi)存結(jié)構(gòu),可通過管道實(shí)現(xiàn)智行單元、主機(jī)軟件之間的高速通信。云計(jì)算數(shù)據(jù)中心任務(wù)較為單一,重復(fù)性強(qiáng),主要包括虛擬平臺(tái)網(wǎng)絡(luò)構(gòu)建和存儲(chǔ)(通信任務(wù))以及機(jī)器學(xué)習(xí)、對(duì)稱及非對(duì)稱加密解密(計(jì)算任務(wù)),算法較為復(fù)雜。新型調(diào)度模式下,CPU計(jì)算任務(wù)趨于碎片化,遠(yuǎn)期云平臺(tái)計(jì)算中心或以FPGA為主,并通過FPGA將復(fù)雜計(jì)算任務(wù)卸載至CPU(區(qū)別于傳統(tǒng)模式下CPU卸載任務(wù)至FPGA的模式)。

全球FPGA市場(chǎng)由四大巨頭Xilinx賽靈思,Intel英特爾(收購(gòu)阿爾特拉)、Lattice萊迪思、Microsemi美高森美壟斷,四大廠商壟斷9,000余項(xiàng)專利技術(shù),把握行業(yè)“制空權(quán)”。

FPGA芯片行業(yè)形成以來,全球范圍約有超70家企業(yè)參與競(jìng)爭(zhēng),新創(chuàng)企業(yè)層出不窮(如Achronix Semiconductor、MathStar等)。產(chǎn)品創(chuàng)新為行業(yè)發(fā)展提供動(dòng)能,除傳統(tǒng)可編程邏輯裝置(純數(shù)字邏輯性質(zhì)),新型可編程邏輯裝置(混訊性質(zhì)、模擬性質(zhì))創(chuàng)新速度加快,具體如Cypress Semiconductor 研 發(fā) 具 有 可 組 態(tài) 性 混 訊 電 路 PSoC(Programmable System on Chip),再如Actel推出Fusion(可程序化混訊芯片)。此外,部分新創(chuàng)企業(yè)推出現(xiàn)場(chǎng)可編程模擬數(shù)組FPAA(Field Programmable Analog Array)等。

隨智能化市場(chǎng)需求變化演進(jìn),高度定制化芯片(SoC ASIC)因非重復(fù)投資規(guī)模大、研發(fā)周期長(zhǎng)等特點(diǎn)導(dǎo)致市場(chǎng)風(fēng)險(xiǎn)劇增。相對(duì)而言,F(xiàn)PGA在并行計(jì)算任務(wù)領(lǐng)域具備優(yōu)勢(shì),在高性能、多通道領(lǐng)域可以代替部分ASIC。人工智能領(lǐng)域多通道計(jì)算任務(wù)需求推動(dòng)FPGA技術(shù)向主流演進(jìn)。

基于FPGA芯片在批量較小(流片5萬片為界限)、多通道計(jì)算專用設(shè)備(雷達(dá)、航天設(shè)備)領(lǐng)域的優(yōu)勢(shì),下游部分應(yīng)用市場(chǎng)以FPGA取代ASIC應(yīng)用方案。

中國(guó)FPGA芯片研發(fā)企業(yè)可以紫光同創(chuàng)、國(guó)微電子、成都華微電子、安路科技、智多晶、高云半導(dǎo)體、上海復(fù)旦微電子和京微齊力為例。從產(chǎn)品角度分析,中國(guó)FPGA硬件性能指標(biāo)相較賽靈思、Intel等差距較大。紫光同創(chuàng)是當(dāng)前中國(guó)市場(chǎng)唯一具備自主產(chǎn)權(quán)千萬門級(jí)高性能FPGA研發(fā)制造能力的企業(yè)。上海復(fù)旦微電子于2018年5月推出自主知識(shí)產(chǎn)權(quán)億門級(jí)FPGA產(chǎn)品。中國(guó)FPGA企業(yè)緊跟大廠步伐,布局人工智能、自動(dòng)駕駛等市場(chǎng),打造高、中、低端完整產(chǎn)品線。

中國(guó)FPGA企業(yè)競(jìng)爭(zhēng)突破口現(xiàn)階段中國(guó)FPGA廠商芯片設(shè)計(jì)軟件、應(yīng)用軟件不統(tǒng)一,易在客戶端造成資源浪費(fèi),頭部廠商可帶頭集中產(chǎn)業(yè)鏈資源,提高行業(yè)整體競(jìng)爭(zhēng)力。

審核編輯:郭婷

-

FPGA

+關(guān)注

關(guān)注

1626文章

21667瀏覽量

601843 -

cpu

+關(guān)注

關(guān)注

68文章

10825瀏覽量

211149 -

機(jī)器視覺

+關(guān)注

關(guān)注

161文章

4345瀏覽量

120111

原文標(biāo)題:收藏:FPGA知識(shí)及芯片技術(shù)

文章出處:【微信號(hào):FPGA研究院,微信公眾號(hào):FPGA研究院】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FPGA在圖像處理領(lǐng)域的優(yōu)勢(shì)有哪些?

人員定位系統(tǒng)對(duì)生產(chǎn)密集型企業(yè)的重要意義

廣和通端側(cè)AI解決方案驅(qū)動(dòng)性能密集型場(chǎng)景商用型場(chǎng)景商用

廣和通端側(cè)AI解決方案驅(qū)動(dòng)性能密集型場(chǎng)景商用型場(chǎng)景商用

FPGA在自動(dòng)駕駛領(lǐng)域有哪些優(yōu)勢(shì)?

FPGA在人工智能中的應(yīng)用有哪些?

鴻蒙OS開發(fā)實(shí)例:【ArkTS類庫多線程CPU密集型任務(wù)TaskPool】

鴻蒙OS開發(fā)實(shí)例:【ArkTS類庫多線程I/O密集型任務(wù)開發(fā)】

博泰“車聯(lián)網(wǎng)云服務(wù)平臺(tái)”入選2023年度專利密集型產(chǎn)品名單

鴻蒙原生應(yīng)用開發(fā)-ArkTS語言基礎(chǔ)類庫多線程I/O密集型任務(wù)開發(fā)

鴻蒙原生應(yīng)用開發(fā)-ArkTS語言基礎(chǔ)類庫多線程CPU密集型任務(wù)TaskPool

什么是FPGA?帶你初步揭開它的面紗

HarmonyOS CPU與I/O密集型任務(wù)開發(fā)指導(dǎo)

FPGA在高性能計(jì)算中的優(yōu)勢(shì)及其用例都有哪些?

FPGA執(zhí)行計(jì)算密集型任務(wù)性能表現(xiàn)及優(yōu)勢(shì)有哪些

FPGA執(zhí)行計(jì)算密集型任務(wù)性能表現(xiàn)及優(yōu)勢(shì)有哪些

評(píng)論