PCB設計之實例解析傳輸線損耗,隨著信號速率的提升和系統越來越復雜,傳輸線已經不是當年的樣子,想怎么設計就怎么設計了。PCB仿真設計也越來越難了,現在板子一大,線長輕輕松松上10inch,可能還會跨個背板,經過幾個連接器,這樣的情況,傳輸線的損耗就是我們設計中不得不考慮的問題了,不然的話,可能分分鐘就翻車了。

那么影響損耗的因素有哪些呢?有哪些又是我們在設計中可以控制的呢?相鄰線的串擾,阻抗不匹配,輻射等等因素都可能對損耗造成影響,這些也都可以從設計層面進行優化,盡量減小影響。還有一個最關鍵的損耗來源,就是我們的傳輸線不是理想傳輸線,是有損傳輸線,本身造成的損耗才是最主要的。下面我們通過一對差分線的仿真來具體說說怎么通過設計來控制損耗。

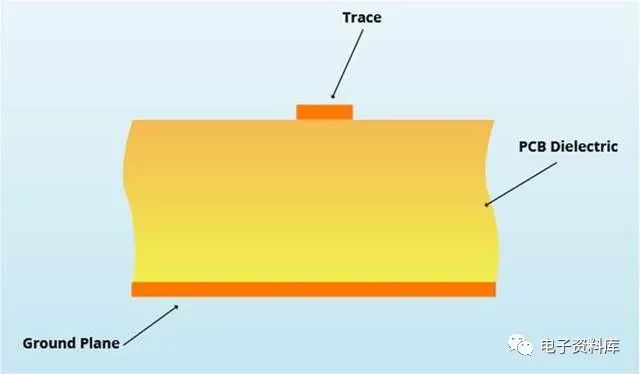

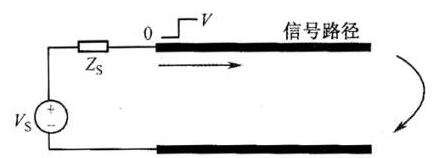

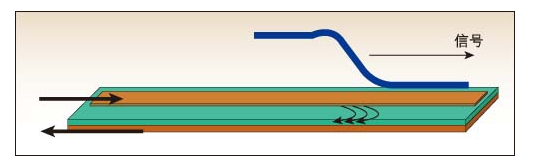

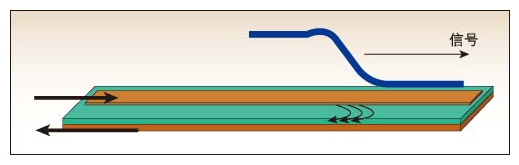

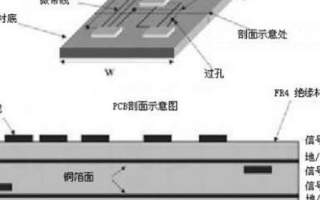

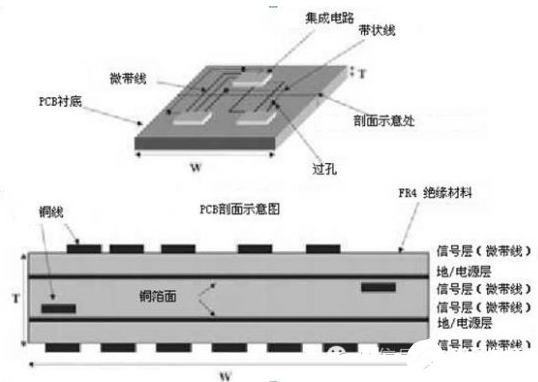

一般的傳輸線損耗分為兩個部分,一個部分是介質損耗,一個部分是導體損耗。介質損耗的話,主要是板材參數的影響。導體損耗,主要是本身傳導損耗,趨膚效應和表面粗糙度。下面兩張圖是仿真傳輸線模型時需要設置的參數,這次我們選擇的是內層差分線做演示。需要在這個界面編輯線寬,間距,銅厚,以及到參考層的介質厚度等參數,編輯完成后,點擊OK即可。

編輯完差分線的參數后,界面就如下圖所示。在這個界面,我們可以編輯材料介電常數,損耗因子,銅箔粗糙度,蝕刻因子等參數。

再設置好長度,就可以仿真得到下面的插損曲線了。

上面看到的是傳輸線的整體的損耗,下面我們看下介質損耗和導體損耗在FR4板材和目前的層疊情況下的一個比例情況,后續就可以比較方便去調整參數減小損耗了。

審核編輯:湯梓紅

-

pcb

+關注

關注

4317文章

23010瀏覽量

396344 -

傳輸線

+關注

關注

0文章

375瀏覽量

23998

發布評論請先 登錄

相關推薦

傳輸線的類型有哪些?PCB上什么樣的線才是傳輸線?

PCB傳輸線參數

印制電路板傳輸線信號損耗測量方法

從阻抗匹配的角度來解析射頻微波傳輸線的設計技術

傳輸線的損耗原理是什么?

如何避免高速PCB設計中傳輸線效應

PCB傳輸線原理_PCB傳輸線參數

高速PCB設計基礎知識:傳輸線

PCB的傳輸線結構

PCB設計之實例解析傳輸線損耗

PCB設計之實例解析傳輸線損耗

評論