晶振是數字電路設計中關鍵先生,通常在電路設計當中,晶振都當作數字電路中的心臟部分,數字電路的所有工作都離不開時鐘信號,而恰好晶振便是直接控制整個系統正常啟動的那個關鍵按鈕,可以說要是有數字電路設計的地方就可以看到晶振。

晶振的定義

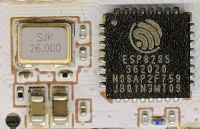

晶振一般是指石英晶體振蕩器和石英晶體諧振器兩種,也可以直接叫晶體振蕩器。都是利用石英晶體的壓電效應制作而成。

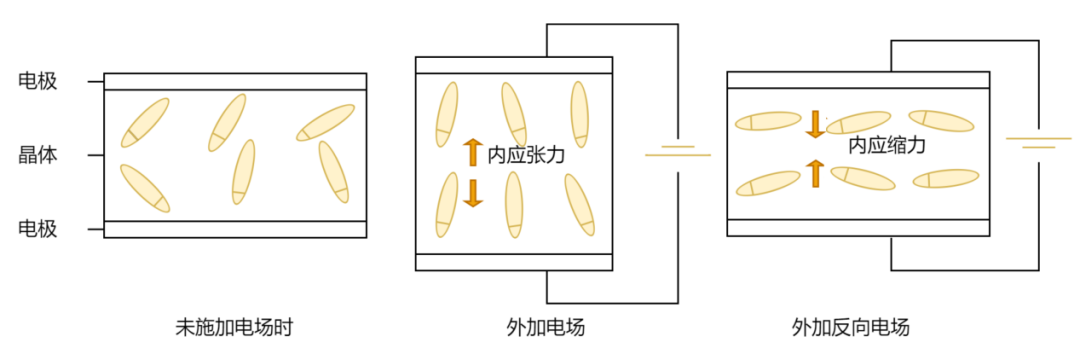

它的工作原理是這樣的:在晶體兩個電極上加上電場后,晶體會發生機械變形,相反的,若是在晶體的兩端加上機械壓力后,晶體又會產生電場。這種現象是可逆的,所以利用晶體的這種特性,在晶體兩端加上交變電壓,晶片就會產生機械振動,同時又會產生交變電場。但是晶體產生的這種振動和電場一般都會很小,但只要在某個特定頻率下,振幅就會明顯增大,就類似我們電路設計者常能見到的LC回路諧振同理。

晶振分類:①無源晶振無源晶振為晶體,一般是2引腳的無極性器件(部分無源晶振有無極性的固定引腳)。無源晶振一般需借助于負載電容形成的時鐘電路才能產生振蕩信號(正弦波信號)。

②有源晶振有源晶振為振蕩器,通常是4個引腳。有源晶振不需要CPU的內部振蕩器,產生方波信號。有源晶振供電便能產生一個時鐘信號。有源晶振信號穩定,質量較好,而且連接方式比較簡單,精度誤差比無源晶振更小,價格比無源晶振更貴。

晶振的等效電路

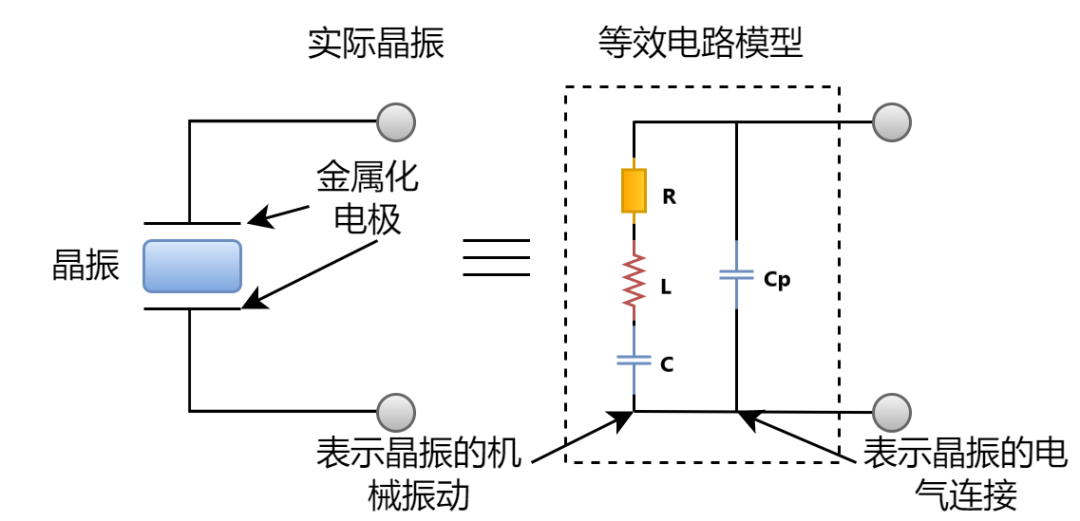

事實上,晶振的作用就像一個串聯的RLC電路。

晶振的等效電路顯示了一個串聯的RLC電路,表示晶振的機械振動,與一個電容并聯表示與晶振的電氣連接,而晶振振蕩器便朝著串聯諧振運行工作。

其中,R是ESR等效串聯電阻,L和C分別是等效電感和電容,Cp為寄生電容。

晶振的基本參數

一般晶振的基本參數有:工作溫度、精度值、匹配電容、封裝形式、核心頻率等。

晶振的核心頻率:一般晶振頻率的選擇取決于頻率元器件的要求規定,像MCU一般是一個范圍,大部分都是從4M到幾十M不等。

晶振的精度:晶振的精度普遍在±5PPM、±10PPM、±20PPM、±50PPM等,高精度的時鐘芯片一般在±5PPM之內,一般運用都會選擇在±20PPM左右。

晶振的匹配電容:通常通過調整匹配電容的值,可以更改晶振的核心頻率,目前在做高精度晶振時,都是用該方法來進行調整。

晶振在PCB的設計布局

作為數字電路中的心臟,晶振影響著整個系統的穩定性,系統晶振的選擇,決定了數字電路的成敗。

由于晶振內部存在石英晶體,受到外部撞擊等情況造成晶體斷裂,很容易造成晶振不啟振,所以通常在電路設計時,要考慮晶振的可靠安裝,其位置盡量不要靠近板邊、設備外殼等地方。PCB對晶振布局時通常注意一下幾點:

①晶振不能距離板邊太近、晶振的外殼必須接地,否則易導致晶振輻射雜訊。在板卡設計時尤其需要注意這點。外殼接地可以避免晶振向外輻射,同時可以屏蔽外來信號對晶振的干擾。如果一定要布置在PCB邊緣,可以在晶振印制線邊上再布一根GND線,同時在包地線上間隔一段距離就打過孔,將晶振包圍起來。

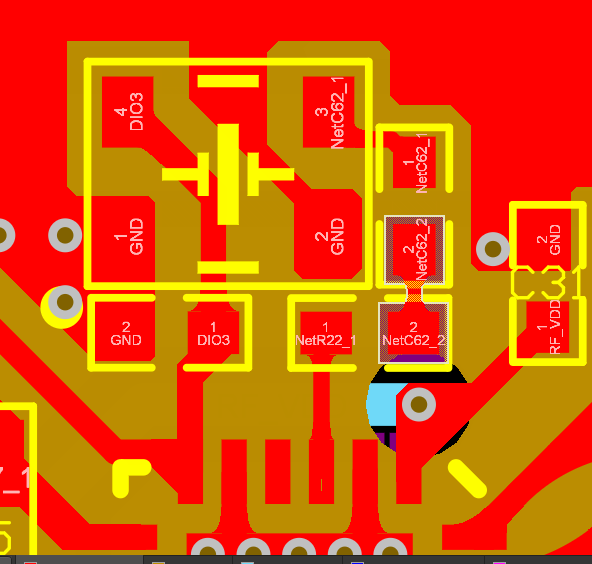

②晶振下方不能布信號線,易導致信號線耦合晶振諧波雜訊。保證完全鋪地,同時在晶振的300mil范圍內不要布線,這樣可以防止晶振干擾其他布線、元器件和層的性能。

③若濾波器件放在晶振下方,且濾波電容與匹配電阻未按照信號流向排布,會使濾波器的濾波效果變差。耦合電容應盡量靠近晶振的電源引腳,按電源流入方向,依容值從大到小順序擺放。

④時鐘信號的走線應盡量簡短,線寬大一些,在布線長度和遠離發熱源上尋找平衡。

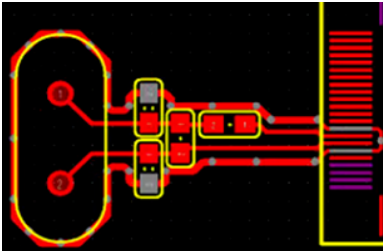

以下圖布局為例,晶振的布局方式會相對更優:①晶振的濾波電容與匹配電路靠近MCU芯片位子,遠離板邊。

②晶振的濾波電容與匹配電阻按照信號流向排布,靠近晶振擺放整齊緊湊。

③晶振靠近芯片處擺放,到芯片的走線盡量短而直。在電路系統中,高速時鐘信號線優先級最高。時鐘線是一個敏感信號,頻率越高,要求走線盡量簡短,以保證信號的失真度達到最小。

因為現在很多電路中,系統晶振時鐘頻率很高,所以干擾諧波出來的能量也強,諧波除了會從輸入與輸出兩條線導出來外,也會從空間輻射出來,這也導致若PCB中對晶振的布局不夠合理,會很容易造成很強的雜散輻射問題,并且一旦產生,很難在通過其他方法來解決,所以在PCB板布局時對晶振和CLK信號線布局非常重要。

審核編輯:湯梓紅

-

pcb

+關注

關注

4317文章

23005瀏覽量

396256 -

振蕩器

+關注

關注

28文章

3813瀏覽量

138870 -

晶振

+關注

關注

34文章

2824瀏覽量

67902

原文標題:晶振在PCB板上如何布局?都是精髓!

文章出處:【微信號:cdebyte,微信公眾號:億佰特物聯網應用專家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

晶振在PCB板上如何布局?

晶振在PCB板上如何布局?

評論