packed union相比unpacked union最大的一個區別就是,在packed union中,所有成員的大小必須相同,這就保證了不管union中存儲了哪一個成員,最終這個union的大小是一樣的。也正是加了這個限制,所以packed union是可綜合的。

類似于packed struct,我們可以對這個union整體進行算法、切分等運算。

typedef union packed {

int a;

bit [31:0] c;

} data;

上面的union聲明加入了packed關鍵字。因為兩個成員的大小相同:“int”是32位,“bit [31:0] c”是32位。所以聲明為unpacked union是沒問題的。

typedef union packed {

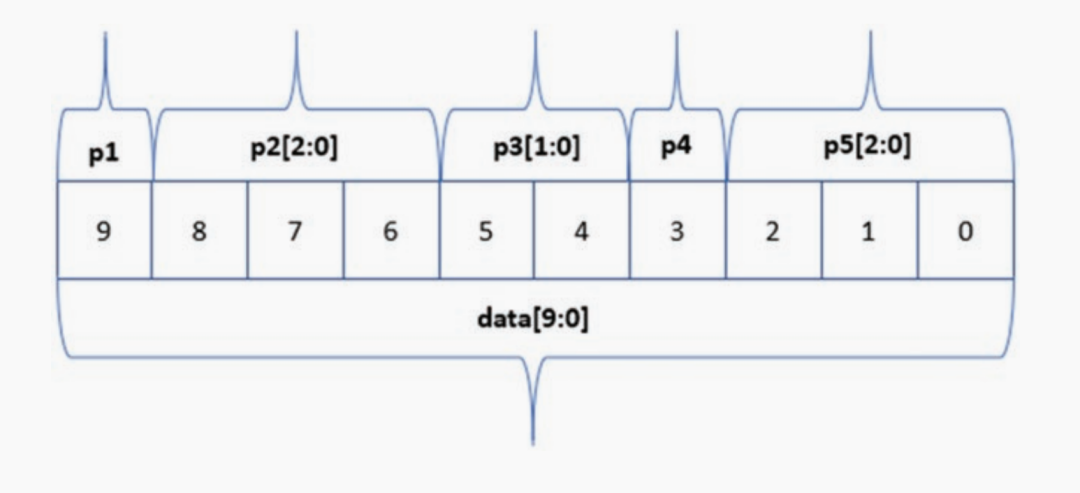

logic [9:0] data;

struct packed {

bit p1;

bit [2:0] p2;

bit [1:0] p3;

bit p4;

bit [2:0] p5;

} p_modes;

} myUnion

myUnion Union1;

在上面的union中有2個成員,分別都是10比特大小 “struct” “p_modes” 和“data” ,在物理內存中分配如下:

審核編輯:湯梓紅

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

Verilog

+關注

關注

28文章

1345瀏覽量

109995 -

System

+關注

關注

0文章

165瀏覽量

36887 -

union

+關注

關注

0文章

10瀏覽量

4253

原文標題:SystemVerilog中的Packed Union

文章出處:【微信號:芯片驗證工程師,微信公眾號:芯片驗證工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

union 的概念及在嵌入式編程中的應用

union 在中文的叫法中又被稱為共用體,聯合或者聯合體,它定義的方式與 struct 是相同的,但是意義卻與 struct 完全不同,下面是 union ...

發表于 02-07 11:30

?0次下載

SpinalHDL中Bundle數據類型的轉換

SpinalHDL中Bundle與SystemVerilog中的packed struct很像,在某些場景下,與普通數據類型之間的連接賦值可以通過asBits,assignFromBi

unpacked數組和packed數組的主要區別

unpacked數組和packed數組的主要區別是unpacked數組在物理存儲時不能保證連續,而packed數組則能保證在物理上連續存儲。

SystemVerilog中的Packed Structure

一個packed structure有很多的bits組成,這些bit在物理上連續存儲。packed structure只允許包含packed數據類型。

Systemverilog中的union

SystemVerilog union允許單個存儲空間以不同的數據類型存在,所以union雖然看起來和struct一樣包含了很多個成員,實際上物理上共享相同的存儲區域。

SystemVerilog中的tagged Unions是什么

tagged union包含一個隱式成員,該成員存儲tag,也就是標記,它表示這個union最終存儲的到底是哪一個成員。

SystemVerilog中的Semaphores

SystemVerilog中Semaphore(旗語)是一個多個進程之間同步的機制之一,這里需要同步的原因是這多個進程共享某些資源。

union和union all有什么區別

Union和Union All是SQL中的兩個關鍵字,它們用于將兩個或多個SELECT語句的結果集合并在一起。這兩個關鍵字雖然有相似的功能,但在實際使用中有一些重要的區別。下面將詳細介紹Uni

SystemVerilog中的Packed Union

SystemVerilog中的Packed Union

評論