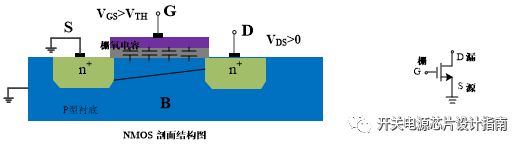

本章定性和定量分析MOS的電流IDS與柵源電壓VGS、漏源電壓VDS間的IV特性關系。NMOS的剖面結構圖以及其電路符合如下圖所示,由柵極(G),漏極(D)、源極(S)和基板(B)構成。當GS極加入正電壓,當VGS>VTH時,G極板通過柵氧電容會在D極和S極間形成帶自由電子的導電溝道;當VDS>0時,導電溝道的自由電子就會移動形成電流。

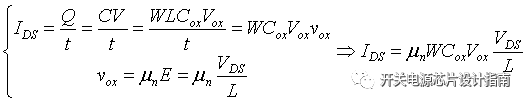

根據電流的定義單位時間流過橫截面的電荷量,可以求出IDS為總的電荷量Q處于時間t;電容的電荷量為C*Vox;下圖為NMOS 的立體結構圖,G極對B極的電容可以近似求出為WLCox(Cox為單位面積柵氧電容值),L(導電溝道長度)除以t則為電荷移動速度vox。電荷移動速度vox又可以由電場VDS/L(假設電場分布均勻)和電子遷移率μn相乘得到。

當VDS=0時即只有VGS作用:形成導電溝道的有效電壓(過驅動電壓)可表示如下:

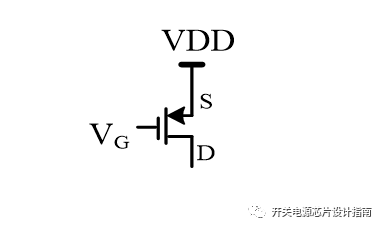

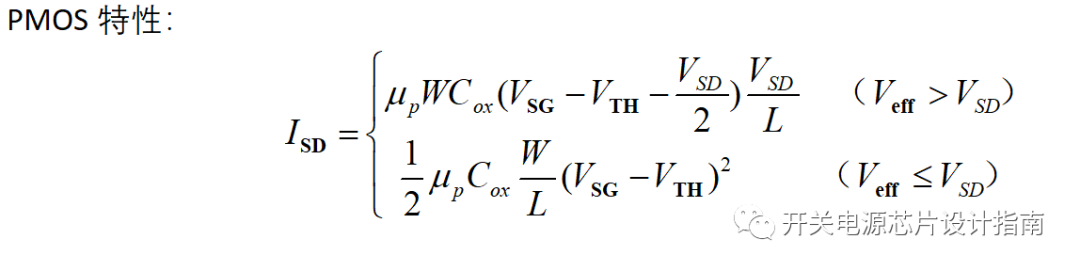

實際上由于VDS與Veff共同作用,形成的溝道電荷厚度不是均勻分布,如下圖所示,導電溝道呈斜坡狀。當VDS

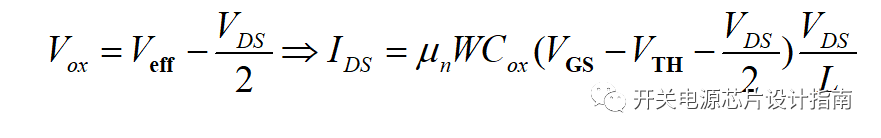

靠近VSS端有效溝道形成電壓高(Veff)電荷厚。取中間點平均電壓VDS/2來近似計算IDS:

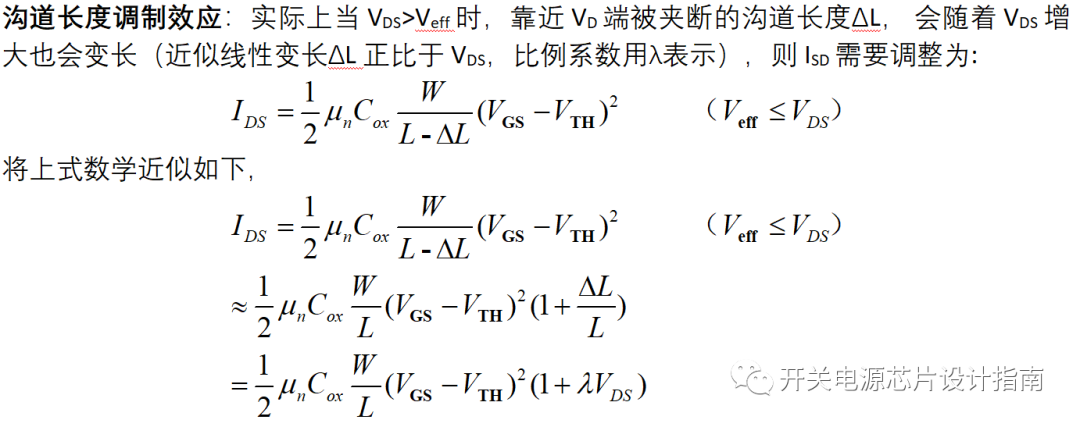

當VDS從0V繼續增大到VDS=Veff時,靠近VD端的溝道被夾斷,有效溝道形成電壓為0;再繼續增大VDS,夾斷點將向源極方向移動,VDS增加的部分全部落在夾斷區,故ID幾乎不隨VDS增大而變化,IDS可表示為:

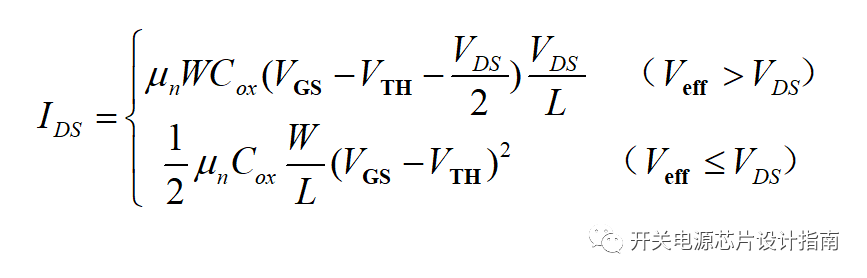

考慮以上兩種情況下的Vox, IDS可綜合如下

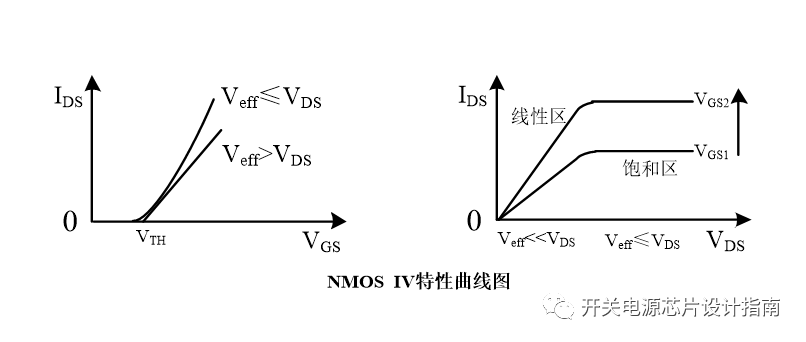

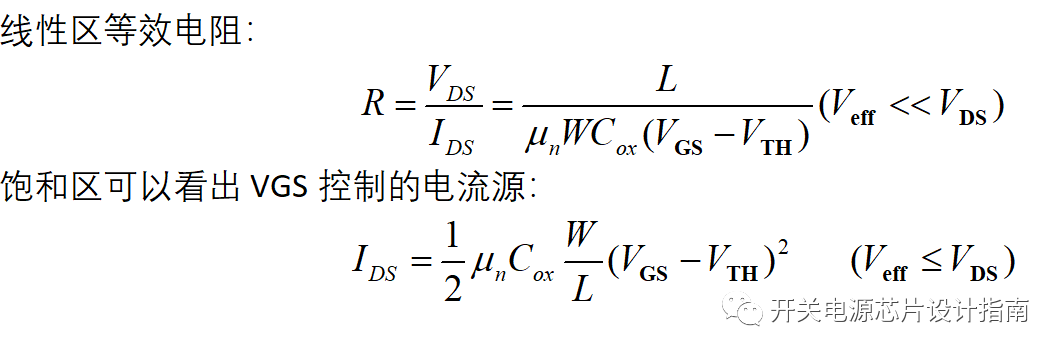

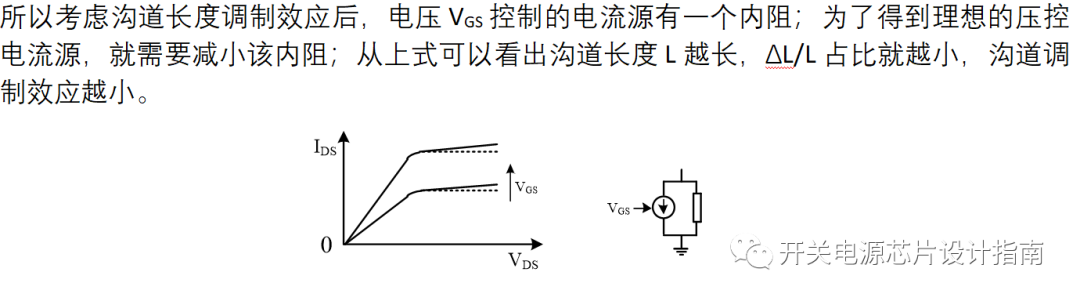

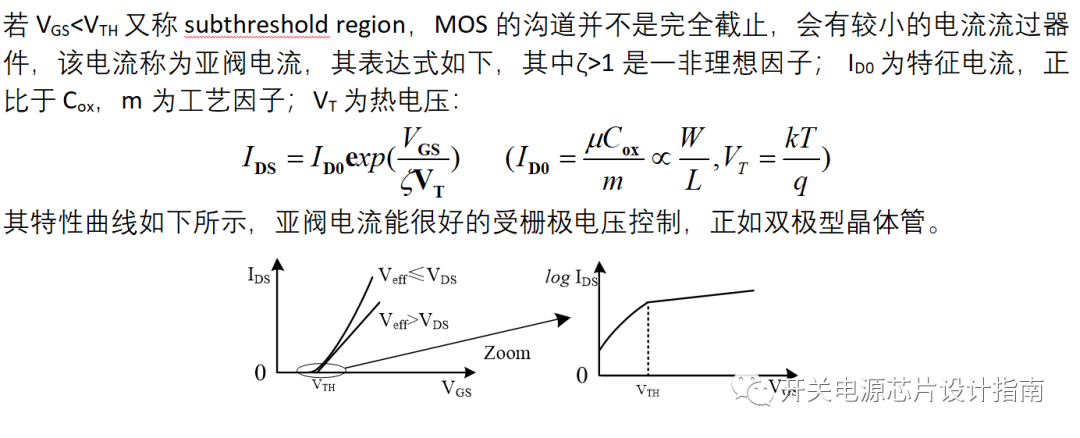

通過分析IDS與VGS和VDS的關系式,NMOS的IV特性曲線如下圖所示。左圖中當VGS

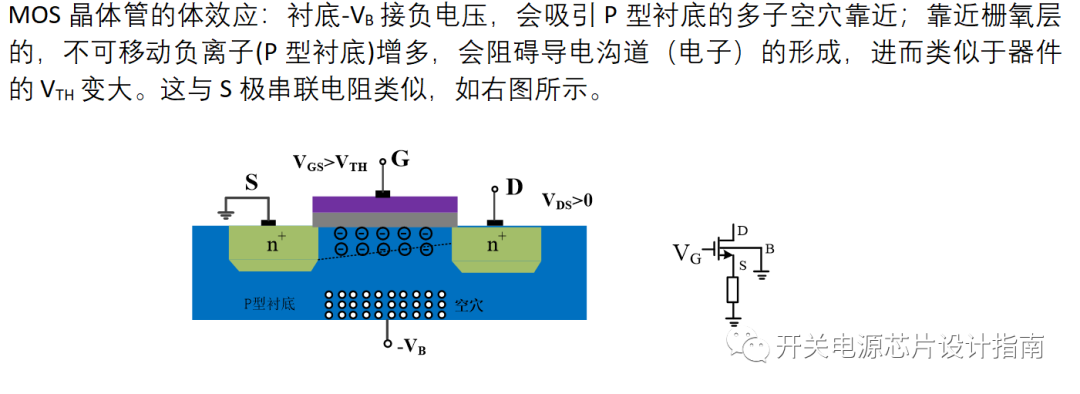

公式如下,其中VSB為源極對襯底的電壓,α為比例系數,大概0.2左右。

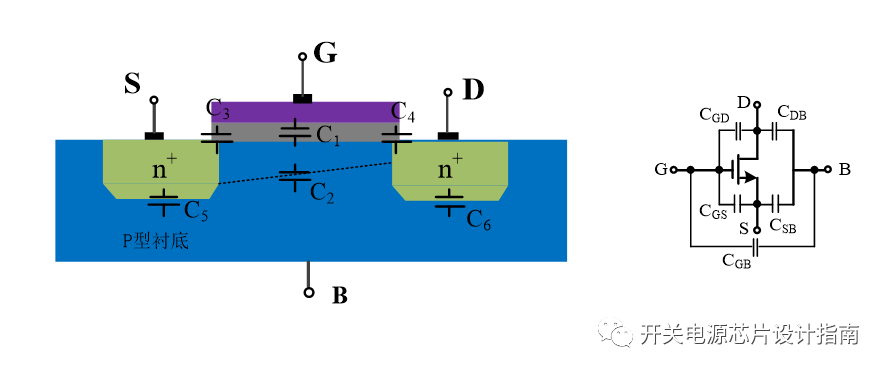

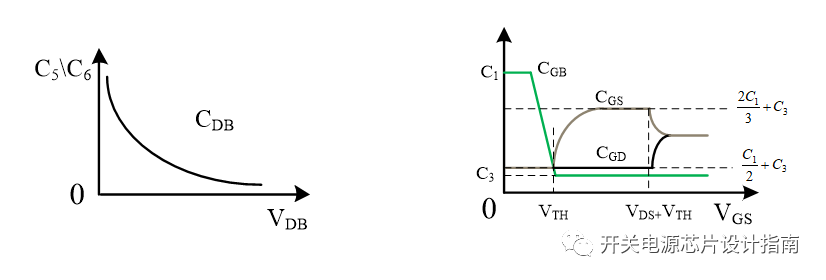

寄生電容:柵氧化層電容C1=WLCox, 襯底和溝道與襯底間的耗盡層電容C2,柵和源/漏極電容C3, C4,源/漏極與襯底間的PN結電容C5和C6。

各電容隨電壓變化趨勢如下圖所示。當VGS=0時,沒有溝道耗盡層C2=0, C3=C4, CGB=(C1串聯連接C2)=C1; 隨著VGS上升至VTH,由于C2很小,C1和C2串聯后的CGB變小;當VDS>VGS>VTH,由于飽和區溝道的存在,C1不存在,CGB=C2保持一個很小的狀態,CGD=C4不變(溝道夾斷),CGS可以看成C3并聯‘C1*2/3’(由于溝道分布不均勻,不等于WLCox); 接著增大VGS>VDS(線性區), 溝道近似線性分布,CGB由于溝道的隔離任然保持一個很小的狀態,CGS可近似認為等于CGD=C3+C1/2=C4+C1/2。源/漏極與襯底間的PN結電容C5與C6,即CDB隨VDB增大而變小,如果S接地,CSB的耗盡層電壓不變也不變。

審核編輯:湯梓紅

-

NMOS

+關注

關注

3文章

291瀏覽量

34299 -

晶體管

+關注

關注

77文章

9641瀏覽量

137876 -

MOS

+關注

關注

32文章

1248瀏覽量

93516

原文標題:MOS晶體管I-V特性

文章出處:【微信號:開關電源芯片設計指南,微信公眾號:開關電源芯片設計指南】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

晶體管的結構特性

吉時利——半導體分立器件I-V特性測試方案

晶體硅光伏(PV)方陣I-V特性的現場測量 GB/T 122

CMOS晶體管,CMOS晶體管是什么意思

增強型MOS晶體管,增強型MOS晶體管是什么意思

數字源表可幫助提取半導體器件的基本 I-V 特性參數

熟透雙極性晶體管(BJT) 輕松做手機射頻PA

MOS晶體管I-V特性

MOS晶體管I-V特性

評論