作者:Henrik Nyholm,Jacob Lunn Lassen

在設(shè)計(jì)安全關(guān)鍵系統(tǒng)時(shí),國際安全標(biāo)準(zhǔn)對我們選擇適當(dāng)?shù)墓に嚭瓦m當(dāng)?shù)募夹g(shù)來檢測和避免最終產(chǎn)品中的危險(xiǎn)故障至關(guān)重要。這些標(biāo)準(zhǔn)確保我們不會(huì)陷入與之前的安全工程師同行相同的坑。

然而,這些標(biāo)準(zhǔn)的危險(xiǎn)在于,它們假設(shè)你對底層硬件(比如微控制器)有詳細(xì)的了解,這可能會(huì)導(dǎo)致經(jīng)驗(yàn)不足的安全工程師實(shí)施不安全的設(shè)計(jì)。例如,IEC(國際電工委員會(huì))60730標(biāo)準(zhǔn)建議使用棋盤格內(nèi)存測試來檢測B類軟件可變存儲(chǔ)器中的直流故障,這比看起來更具挑戰(zhàn)性。

本文描述了SRAM的邏輯和物理布局之間未記錄的差異如何導(dǎo)致我們無意中錯(cuò)誤地實(shí)施諸如棋盤格算法之類的內(nèi)存測試。標(biāo)準(zhǔn)微控制器的數(shù)據(jù)表中通常沒有必要的信息,但幸運(yùn)的是,有些存儲(chǔ)器測試算法不受SRAM邏輯和物理布局差異的影響。

在運(yùn)行時(shí)測試 SRAM 是否存在缺陷

SRAM存儲(chǔ)器顯然由IC供應(yīng)商在生產(chǎn)中進(jìn)行測試,有缺陷的產(chǎn)品不會(huì)運(yùn)送給消費(fèi)者。盡管如此,在IC的使用壽命期間,隨機(jī)硬件缺陷可能并且將會(huì)出現(xiàn),這也是在安全關(guān)鍵應(yīng)用中需要在運(yùn)行時(shí)測試微控制器中的硬件的原因之一。

棋盤格內(nèi)存測試

IEC 60730 (H.2.19.6.1) 等安全標(biāo)準(zhǔn)表明,對于必須符合 B 類安全等級(jí)的應(yīng)用,可以使用棋盤算法來識(shí)別 SRAM 中的某些缺陷(直流故障)。通常選擇棋盤格測試,因?yàn)樗w了SRAM中最可能的故障,并且速度相對較快,可以方便地將對應(yīng)用本身的性能影響降至最低。除了位永久卡在高電平或低電平的直流故障外,棋盤格算法還可以檢測相鄰位相互影響的缺陷。

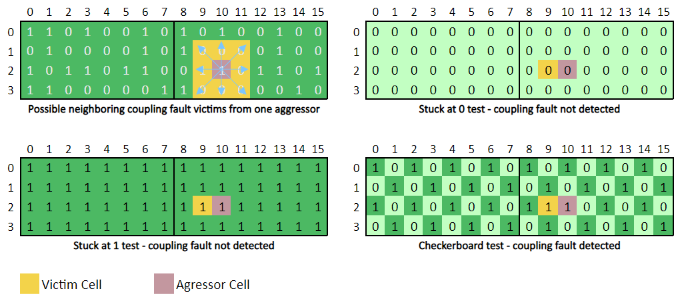

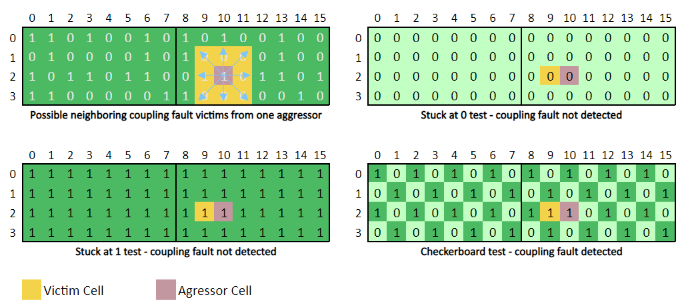

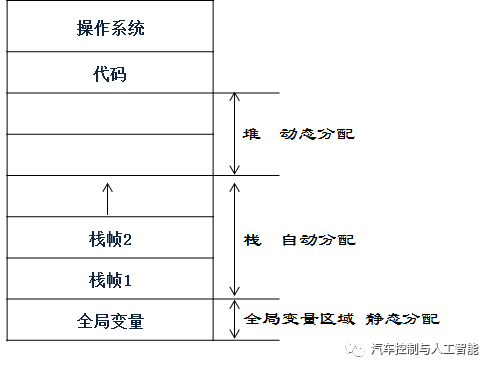

SRAM在邏輯上由許多用單詞組織的位組成。這些字通常為 8 位、16 位或 32 位寬,但也可以更長。從物理上講,這些位被組織成數(shù)組,其中每個(gè)位通常有八個(gè)相鄰位(參見圖1)。位中的物理缺陷會(huì)影響單個(gè)位,使其卡在高電平或低電平(直流故障),或者缺陷可能位于兩個(gè)位的分離中,在這種情況下,相鄰的侵略者單元(在圖1中以紫色標(biāo)記)可能會(huì)影響受害單元(在圖1中以黃色標(biāo)記)。侵略者-受害者場景通常稱為耦合故障。從統(tǒng)計(jì)學(xué)上看,直流故障更有可能發(fā)生,但檢測最可能的耦合故障仍然相關(guān)。

圖1 - 相鄰位之間的潛在耦合故障。

如果故障影響單個(gè)位,導(dǎo)致該位卡在高電平或低電平,則可以通過寫入值 1,通過讀回來驗(yàn)證 1,然后寫入值零并通過讀回來驗(yàn)證零來顯示它,如圖 1 所示。另一方面,如果缺陷是兩個(gè)相鄰位之間的耦合錯(cuò)誤,例如第 2 行中的位列 9 和 10,則某些模式(例如所有 1 或所有 0)不會(huì)顯示耦合故障,因?yàn)閱卧裨跍y試期間具有相同的值。

相鄰單元(側(cè)面、上方和下方)的耦合故障具有相反的二進(jìn)制值。圖1(右下)說明位10中的位污染了位9,由于位9未保持預(yù)期值為零,因此揭示了耦合故障。

SRAM 的物理布局與邏輯布局

為了使棋盤格算法正常工作,需要知道哪些位是相鄰位。事實(shí)證明這是一個(gè)問題,因?yàn)閿?shù)據(jù)手冊通常只描述SRAM的邏輯布局,而不是SRAM的物理組織方式。

要了解SRAM的物理布局,必須區(qū)分面向位的存儲(chǔ)器(BOM)和面向字的存儲(chǔ)器(WOM),前者當(dāng)時(shí)可以訪問一位,后者當(dāng)時(shí)讀取和寫入n位字。雖然大多數(shù)現(xiàn)實(shí)世界的內(nèi)存都是以口碑形式實(shí)現(xiàn)的,但科學(xué)文獻(xiàn)中的經(jīng)典內(nèi)存測試算法通常假設(shè)BOM實(shí)現(xiàn)。

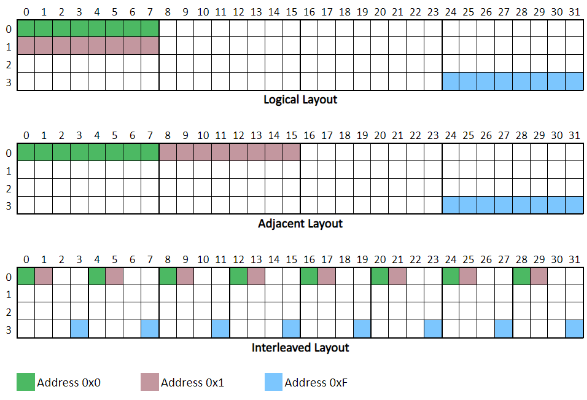

對于口碑記憶,構(gòu)成單詞的位的物理組織主要分為三類:相鄰、交錯(cuò)和子數(shù)組。邏輯布局將每個(gè)單詞放在同一列中前一個(gè)單詞的下方(類似地址空間),而相鄰的存儲(chǔ)器將每個(gè)單詞放在同一行中,彼此相鄰,如圖 2 所示。交錯(cuò)架構(gòu)將字的每個(gè)位分隔到SRAM陣列的不同列和行中。最后,子陣列組織將字的每個(gè)位放置在SRAM的不同物理上獨(dú)立的塊中。現(xiàn)實(shí)情況是,您不知道物理布局,這是正確實(shí)施棋盤格測試所必需的。

圖 2 - 面向單詞的存儲(chǔ)器的物理布局示例。

棋盤格測試的特性和缺點(diǎn)

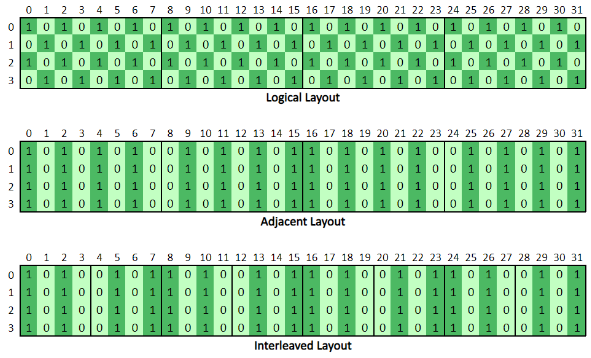

實(shí)現(xiàn)棋盤格算法的簡單方法是交替地將值0xAA(假設(shè)是 8 位數(shù)據(jù)字)寫入第一個(gè)地址,0x55寫入下一個(gè)地址,直到所有被測地址都填充了棋盤格模式 1 和 0。然后驗(yàn)證該模式以檢測相鄰電池之間的任何直流或耦合故障。然后使用反向模式重復(fù)該過程。如前所述,有一個(gè)問題:內(nèi)存邏輯布局中的棋盤圖案可能不是底層物理布局中的棋盤圖案,如圖 3 所示。

圖3 - 邏輯SRAM與物理SRAM的數(shù)據(jù)模式。

補(bǔ)償邏輯布局和物理布局之間的差異似乎很明顯,但器件的數(shù)據(jù)表中很少提供必要的信息。那么,你會(huì)怎么做呢?接受較低的覆蓋率,畢竟診斷仍然會(huì)覆蓋直流故障和相鄰位之間的一些耦合故障?向 IC 供應(yīng)商請求布局,并為每個(gè)器件定制棋盤格測試?還是選擇其他算法?

現(xiàn)在您已經(jīng)意識(shí)到棋盤測試的潛在缺點(diǎn),您可以做出明智的決定。

SRAM 運(yùn)行時(shí)測試的替代算法

IEC 60730中針對C類安全級(jí)別提出的存儲(chǔ)器測試技術(shù)具有更高的故障檢測覆蓋率,但這些算法屬于可以被認(rèn)為是生產(chǎn)測試算法的算法:它們需要更長的運(yùn)行時(shí)間,也可以檢測罕見的故障類型,但通常會(huì)破壞存儲(chǔ)在SRAM中的數(shù)據(jù),因?yàn)樗鼈冊谡麄€(gè)SRAM上運(yùn)行,而不是在子塊中運(yùn)行。

一般來說,對于我們的嵌入式設(shè)計(jì),我們不太能容忍這種情況。因此,我們建議您考慮從生產(chǎn)測試三月算法改編的混合三月算法:這些算法可用于 WOM 優(yōu)化實(shí)現(xiàn)并提供高測試覆蓋率。此外,可以實(shí)現(xiàn)這些混合March算法,以便它們在SRAM的較小重疊部分上運(yùn)行,以避免一次擦除SRAM中的所有數(shù)據(jù),這意味著可以避免重新啟動(dòng)嵌入式系統(tǒng)。March算法的缺點(diǎn)是它們比傳統(tǒng)的棋盤格算法計(jì)算量更大,但這是安全關(guān)鍵系統(tǒng)中可能需要的費(fèi)用。

如果您考慮將傳統(tǒng)的棋盤格測試換成三月測試,您可以從一些微控制器供應(yīng)商那里找到這樣的實(shí)現(xiàn)。Microchip是提供March C-算法的性能優(yōu)化實(shí)現(xiàn)的公司之一,作為其軟件診斷庫的一部分。Microchip實(shí)現(xiàn)支持整個(gè)SRAM的測試,通常在啟動(dòng)時(shí)完成,只是為了獲得最大的測試覆蓋率,以及較小的存儲(chǔ)器塊的測試,旨在減少對應(yīng)用的實(shí)時(shí)影響。

審核編輯:郭婷

-

微控制器

+關(guān)注

關(guān)注

48文章

7496瀏覽量

151086 -

嵌入式

+關(guān)注

關(guān)注

5072文章

19026瀏覽量

303532 -

sram

+關(guān)注

關(guān)注

6文章

764瀏覽量

114638

發(fā)布評論請先 登錄

相關(guān)推薦

嵌入式電子控制單元(ECU)中如何準(zhǔn)確找出運(yùn)行時(shí)使用的RAM量?

如何在運(yùn)行時(shí)禁用IWDG

如何在運(yùn)行時(shí)更新RAM?

嵌入式系統(tǒng)能耗怎么實(shí)現(xiàn)動(dòng)態(tài)管理?

Touchgfx在運(yùn)行時(shí)如何更改整個(gè)屏幕?

運(yùn)行時(shí)軟件故障注入器的設(shè)計(jì)與實(shí)現(xiàn)

嵌入式系統(tǒng)安全處理器的解決方案與設(shè)計(jì)

嵌入式零功耗系統(tǒng)設(shè)計(jì)研究

紫金橋組態(tài)軟件新的功能_運(yùn)行時(shí)組態(tài)

多核對嵌入式設(shè)計(jì)原則造成哪些影響

設(shè)計(jì)安全關(guān)鍵型嵌入式系統(tǒng):在運(yùn)行時(shí)檢測SRAM故障的挑戰(zhàn)

在運(yùn)行時(shí)檢測SRAM故障的挑戰(zhàn)

嵌入式系統(tǒng)中函數(shù)如何調(diào)用

如何在AUTOSAR OS系統(tǒng)運(yùn)行時(shí)使用事件Event呢?

設(shè)計(jì)安全關(guān)鍵型嵌入式系統(tǒng):在運(yùn)行時(shí)檢測SRAM故障的挑戰(zhàn)

設(shè)計(jì)安全關(guān)鍵型嵌入式系統(tǒng):在運(yùn)行時(shí)檢測SRAM故障的挑戰(zhàn)

評論