摘要:現(xiàn)場(chǎng)可編程門陣列(FPGA)具有低功耗、高性能和靈活性的特點(diǎn)。FPGA神經(jīng)網(wǎng)絡(luò)加速的研究正在興起,但大多數(shù)研究都基于國外的FPGA器件。為了改善國內(nèi)FPGA的現(xiàn)狀,提出了一種新型的卷積神經(jīng)網(wǎng)絡(luò)加速器,用于配備輕量級(jí)RISC-V軟核的國產(chǎn)FPGA(紫光同創(chuàng)PG2L100H)。所提出的加速器的峰值性能達(dá)到153.6 GOP/s,僅占用14K LUT(查找表)、32個(gè)DRM(專用RAM模塊)和208個(gè)APM(算術(shù)處理模塊)。所提出的加速器對(duì)于大多數(shù)邊緣AI應(yīng)用和嵌入式系統(tǒng)具有足夠的計(jì)算能力,為國內(nèi)FPGA提供了可能的AI推理加速方案。

背景

卷積神經(jīng)網(wǎng)絡(luò)在機(jī)器視覺任務(wù)中越來越流行,包括圖像分類和目標(biāo)檢測(cè)。如何在有限的條件下充分發(fā)揮FPGA的最大性能是各研究者的主要方向。如今,大多數(shù)CCN使用外國FPGA器件。由于國內(nèi)FPGA起步較晚,其相關(guān)開發(fā)工具和設(shè)備落后于其他外國制造商。因此,在國內(nèi)FPGA上構(gòu)建高性能CNN并替換現(xiàn)有成熟的異構(gòu)方案是一項(xiàng)具有挑戰(zhàn)性的任務(wù)。

Zhang[1]于2015年首次對(duì)卷積網(wǎng)絡(luò)推理中的數(shù)據(jù)共享和并行性進(jìn)行了深入分析和探索。Guo[2]提出的加速器在214MHz下達(dá)到了84.3 GOP/s的峰值性能。2016年,Qiu[3]更深入地探索了使用行緩沖器的加速器。本文提出了一種更高效、更通用的卷積加速器。提出的加速器峰值性能達(dá)到153.6GOP/s,僅占用14K LUT、32個(gè)DRM和208個(gè)APM。本文的章節(jié)安排如下,第2節(jié)介紹了我們提出的加速器的詳細(xì)設(shè)計(jì)以及基于RISC-V的加速器實(shí)現(xiàn)的控制調(diào)度方案。第3節(jié)給出了實(shí)驗(yàn)結(jié)果。

系統(tǒng)設(shè)計(jì)

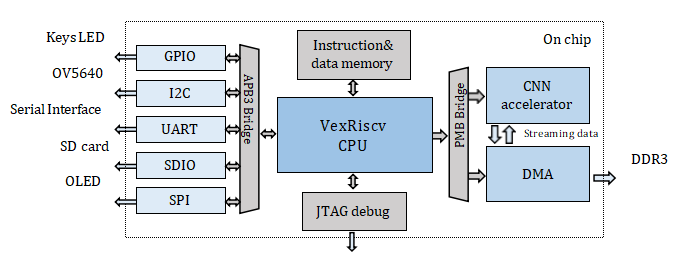

整個(gè)RISC-V片上系統(tǒng)設(shè)計(jì)如圖1所示。該系統(tǒng)主要由RISC-V軟核CPU、指令/數(shù)據(jù)存儲(chǔ)器、總線橋、外圍設(shè)備、DMA(直接存儲(chǔ)器訪問)和卷積加速器組成。

Fig. 1. 片上RISC-V系統(tǒng)設(shè)計(jì)圖

我們的工作主要在三個(gè)方面。首先,我們使用軟核CPU作為片上系統(tǒng)的主控,控制外設(shè),DMA,CNN加速器來實(shí)現(xiàn)數(shù)據(jù)調(diào)度和操作。其次,1D(一維)加速器被設(shè)計(jì)用于改變緩沖機(jī)制。第三,為紫光同創(chuàng)的FPGA設(shè)備設(shè)計(jì)了一個(gè)DMA IP,用于卷積加速的應(yīng)用。

A、RISC-V 軟核CPU 架構(gòu)

軟核。使用RISC-V軟核VexRiscv代替Ibex[4]構(gòu)建RISC-V的片上系統(tǒng)和面向軟件的方法可以使VexRiscv具有高度的靈活性和可擴(kuò)展性。

接口。I2C和SPI等外圍設(shè)備通過APB3總線連接到RISC-V軟核。DMA和加速器通過PMB總線連接到RISC-V軟核。

指令與數(shù)據(jù)存儲(chǔ)。程序被交叉編譯以獲得一個(gè)特定的文件,該文件由JTAG燒錄到片上指令/數(shù)據(jù)存儲(chǔ)器中。

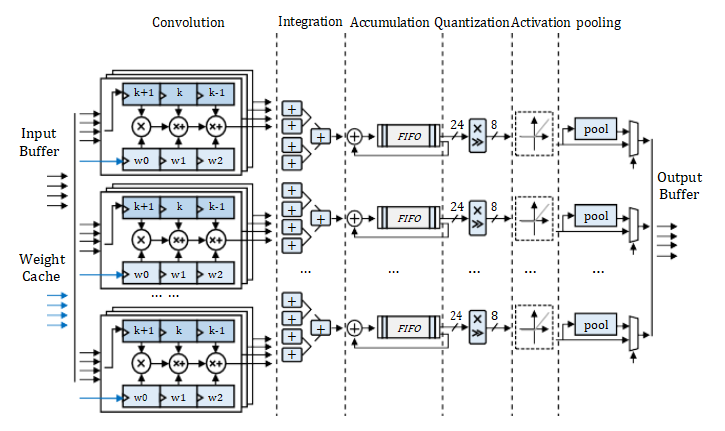

B、CNN 加速器結(jié)構(gòu)

輸入緩存。使用乒乓緩存來實(shí)現(xiàn)緩沖區(qū),可以有效地提高吞吐量。

輸出緩存。權(quán)重緩存模塊由一系列分布式RAM和串行到并行單元組成。

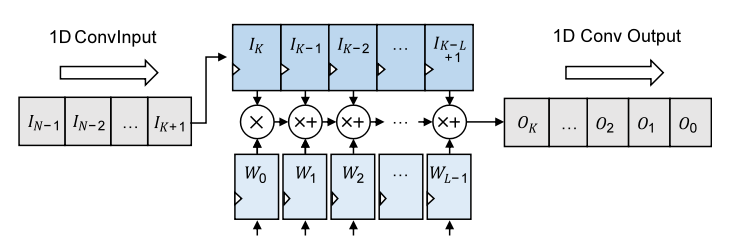

卷積。圖2中的1D卷積模塊分為四組,其中包含四個(gè)1D卷曲單元。每個(gè)單元負(fù)責(zé)1D卷積的一個(gè)信道。

合并。積分模塊有四組加法器樹。每組加法器樹將每組卷積運(yùn)算單元的結(jié)果相加,得到單向輸出結(jié)果。

累加。累加模塊中有四組FIFO和四個(gè)加法器。加速器一次只能接收四個(gè)通道的輸入特征圖數(shù)據(jù)。

量化。該量化模塊由乘法單元和移位單元組成。它通過比例變換將24位累加結(jié)果重新轉(zhuǎn)換為8位[5]。

激活。激活功能通過查找由一系列分布式RAM組成的表來實(shí)現(xiàn)。它存儲(chǔ)ReLu、Leaky ReLu和sigmoid函數(shù)的INT8函數(shù)表。

池化。確定當(dāng)前卷積層是否與池化層級(jí)聯(lián),然后決定是否使用池化模塊來完成池化操作。

輸出緩存。輸出緩沖器由FIFO而不是乒乓緩存實(shí)現(xiàn)。輸出高速緩存FIFO將結(jié)果存儲(chǔ)回片外存儲(chǔ)器,作為下一卷積層的輸入。

Fig. 2. CNN 加速器實(shí)現(xiàn)

C、DMA 結(jié)構(gòu)

神經(jīng)網(wǎng)絡(luò)不僅對(duì)計(jì)算能力有很高的要求,而且對(duì)內(nèi)存也有很大的需求。中低端FPGA通常需要DDR SRAM(雙數(shù)據(jù)速率同步動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器)來承載整個(gè)神經(jīng)網(wǎng)絡(luò)和所有中間運(yùn)算結(jié)果的權(quán)重。紫光同創(chuàng)的FPGA的DDR3內(nèi)存驅(qū)動(dòng)器IP為用戶提供了簡化AXI4總線的內(nèi)存訪問接口。

由于Simpled AXI和AXI之間的標(biāo)準(zhǔn)差異,需要新的DMA設(shè)計(jì)。DMA設(shè)計(jì)如下。讀和寫地址通道由RISC-V軟核直接控制。讀寫數(shù)據(jù)通道的FIFO用作卷積加速器和DDR3驅(qū)動(dòng)器IP的緩沖器,以完成端口轉(zhuǎn)換。

D、實(shí)現(xiàn)細(xì)節(jié)

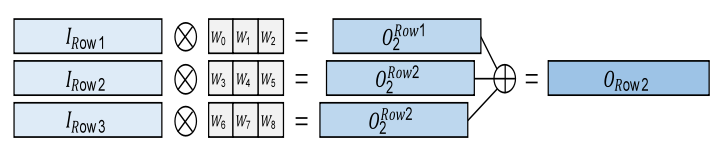

1、一維卷積單元陣列設(shè)計(jì)

神經(jīng)網(wǎng)絡(luò)不僅對(duì)計(jì)算能力有很高的要求,而且對(duì)內(nèi)存也有很大的需求。中低端FPGA通常需要DDR SRAM(雙數(shù)據(jù)速率同步動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器)來承載整個(gè)神經(jīng)網(wǎng)絡(luò)和所有中間運(yùn)算結(jié)果的權(quán)重。紫光同創(chuàng)的FPGA的DDR3內(nèi)存驅(qū)動(dòng)器IP為用戶提供了簡化AXI4總線的內(nèi)存訪問接口。

由于Simpled AXI和AXI之間的標(biāo)準(zhǔn)差異,需要新的DMA設(shè)計(jì)。DMA設(shè)計(jì)如下。讀和寫地址通道由RISC-V軟核直接控制。讀寫數(shù)據(jù)通道的FIFO用作卷積加速器和DDR3驅(qū)動(dòng)器IP的緩沖器,以完成端口轉(zhuǎn)換。

2、卷積加速器控制

本文提出了一種基于指令隊(duì)列的設(shè)計(jì),以減少RISC-V軟核中DMA和加速器的響應(yīng)延遲。RISC-V CPU可以連續(xù)發(fā)送多個(gè)存儲(chǔ)器讀寫請(qǐng)求指令和多個(gè)操作調(diào)度控制指令,而不用等待DMA和加速器的反饋。DMA和加速器從隊(duì)列中獲取指令,任務(wù)完成后直接從隊(duì)列中取出下一條指令,無需等待相應(yīng)的CPU,從而實(shí)現(xiàn)低延遲調(diào)度。

Fig. 3. 1X3 一維卷積原理圖

Fig. 4. 一維卷積單元硬件實(shí)現(xiàn)

實(shí)現(xiàn)結(jié)果和備注

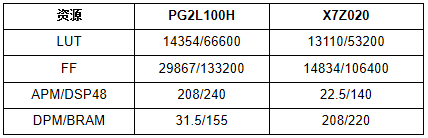

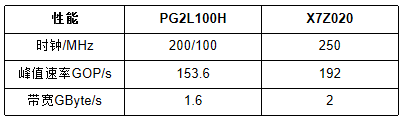

通過在PG2L100H和X7Z020上實(shí)現(xiàn)相同配置的CNN加速器,完成了CNN加速器的性能測(cè)試,驗(yàn)證了國產(chǎn)FPGA CNN加速方案的可行性。加速器的資源消耗和性能如表I和表II所示。

TABLE I 資源利用

PG2L100H和X7Z020的資源消耗相似。PG2L100H需要額外的邏輯資源來構(gòu)建VexRiscv CPU,而X7Z020為AXI DMA IP使用更多的邏輯資源。就加速器性能而言,可從表II中看出。由于FPGA器件架構(gòu)的差異,與X7Z020相比,加速器的卷積運(yùn)算在PG2L100H上只能在200MHz下實(shí)現(xiàn)更好的收斂。RISC-V軟核只能在100MHz下實(shí)現(xiàn)定時(shí)收斂。

TABLE II 性能對(duì)比

我們提出了一種基于RISC-V的一維卷積運(yùn)算的新設(shè)計(jì)。該加速器在國內(nèi)FPGA上的實(shí)現(xiàn)和部署已經(jīng)完成,其性能與具有相同規(guī)模硬件資源的國外FPGA相當(dāng)。

本文論證了基于國產(chǎn)FPGA的CNN異構(gòu)方案的可行性,該研究是國產(chǎn)FPGA應(yīng)用生態(tài)中CNN加速領(lǐng)域的一次罕見嘗試。

審核編輯 :李倩

-

FPGA

+關(guān)注

關(guān)注

1626文章

21667瀏覽量

601858 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7452瀏覽量

163606 -

RISC-V

+關(guān)注

關(guān)注

44文章

2229瀏覽量

46032

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

飛凌嵌入式T113-i開發(fā)板RISC-V核的實(shí)時(shí)應(yīng)用方案

RISC-V發(fā)展及FPGA廠商為什么選擇RISC-V

FET113i-S核心板已支持RISC-V,打造國產(chǎn)化降本的更優(yōu)解

國產(chǎn)RISC-V案例分享,基于全志T113-i異構(gòu)多核平臺(tái)!

國產(chǎn)RISC-V基于全志T113-i異構(gòu)多核平臺(tái)

基于國產(chǎn)異構(gòu)雙核(RISC-V+FPGA)處理器,AG32開發(fā)板開發(fā)資料

淺談國產(chǎn)異構(gòu)雙核RISC-V+FPGA處理器AG32VF407的優(yōu)勢(shì)和應(yīng)用場(chǎng)景

Imagination CPU 系列研討會(huì) | RISC-V 平臺(tái)的性能分析和調(diào)試

國產(chǎn)RISC-V芯片性能穩(wěn)定嗎?

國產(chǎn)RISC-V MCU推薦

Achronix與Bluespec聯(lián)合宣布推出一款支持Linux的RISC-V軟處理器

品讀《基于FPGA與RISC-V的嵌入式系統(tǒng)設(shè)計(jì)》

瑞薩推出采用自研CPU內(nèi)核的通用32位RISC-V MCU 加強(qiáng)RISC-V生態(tài)系統(tǒng)布局

Imagination:RISC-V CPU的重要力量

基于RISC-V軟核CPU的國產(chǎn)FPGA CNN異構(gòu)方案的實(shí)現(xiàn)

基于RISC-V軟核CPU的國產(chǎn)FPGA CNN異構(gòu)方案的實(shí)現(xiàn)

評(píng)論