集成電路的接觸孔工藝是用于將前段(FEOL)所制好的有源和無源器件與后段(BEOL)的第一層互連金屬在物理和電學上連接起來的工藝。它是多個集成電路制造工藝的集成:

①CVD生長SiO2或 Si3N4介質層,CMP 磨平 SiO2介質層的平坦化工藝;

②光刻工藝曝光接觸孔圖形,刻蝕 SiO2或Si3N4介質打開接觸孔,熱退火回流形成光滑的接觸孔形狀;

③PVD 生長阻擋層(如Ti/TiN),CVD 金屬鎢栓塞(W-Plug),CMP 金屬鎢;

④為了形成良好的金屬與硅襯底的歐姆接觸而進行的中溫(約 400°)退火。

接觸孔工藝是集成電路制造中的關鍵工藝,也是技術難度最高的工藝之一。接觸孔的尺寸是集成電路工藝中最小的尺寸之一,是決定芯片面積的關鍵尺寸。

考慮到接觸孔有的是在源漏硅襯底上,有的是在多晶硅柵上,這樣就導致需要被干法刻蝕掉的 Si3N4或 SiO20的厚度不同,也就是說,接觸孔的深度不一致,容易引起淺的接觸孔下面的材料被損傷或刻蝕掉,所以要求干法刻蝕的選擇比很高,既要將介質膜刻體完,又不能損壞其下面的材料。

為此,通常在介質層中加入 Si3N4作為阻擋層(Barrier Layer)。干法刻蝕的氣體通常是 CF4、 C2F3、C3F8、 NF3、He 等氣體,以及它們的混合氣體。

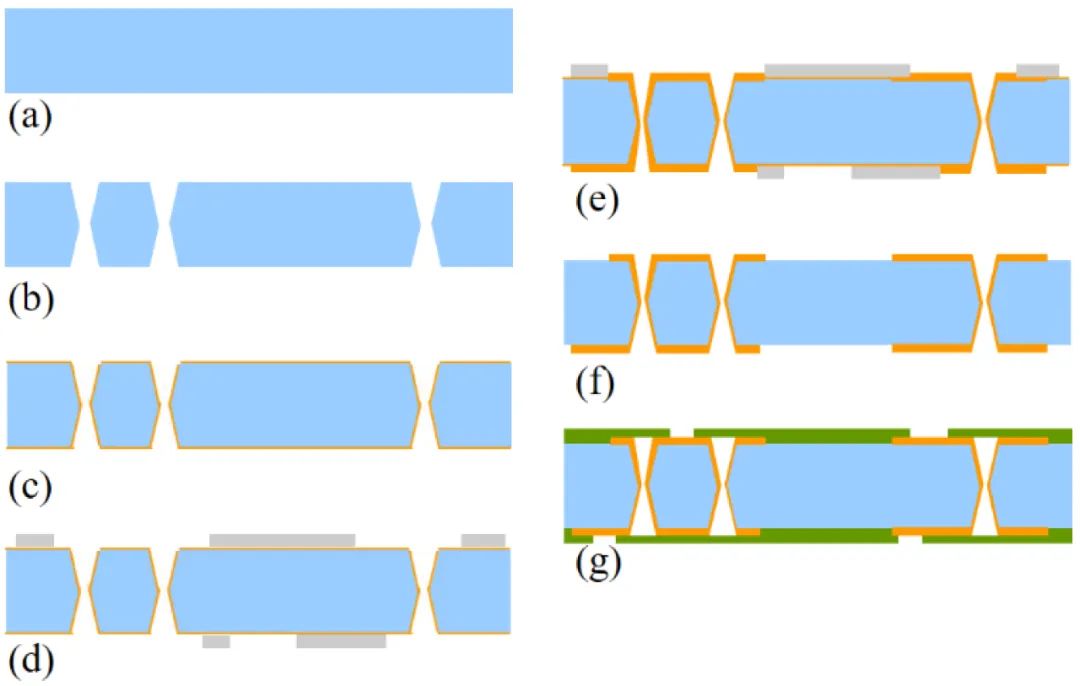

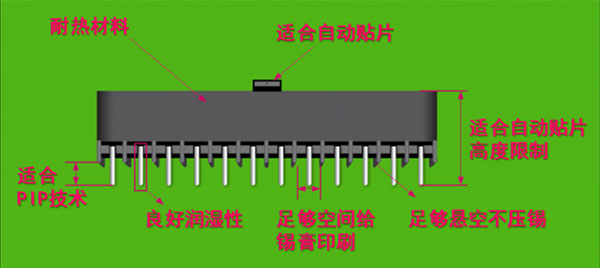

接觸孔的形狀也是需要重點關注的,上、下尺寸要求基本一樣,孔的表面平滑,上開口稍微打開(像一個喇叭口),以確保阻擋層的均勻性,并形成良好的覆蓋。為了形成接觸孔開口良好、光滑的形狀,通常在 SiO2介質層中摻雜硼和磷,形成硼磷硅玻璃或磷硅玻璃(用熱退火回流形成)。

最后的 CMP 金屬鎢或干法刻蝕金屬鎢,是為了去除殘留在氧化層表面的多余的鎢,以便形成互相隔離的接觸孔(通常其形狀是圓形的)。

審核編輯 :李倩

-

集成電路

+關注

關注

5381文章

11389瀏覽量

360880 -

SiO2

+關注

關注

0文章

20瀏覽量

8509 -

CVD

+關注

關注

1文章

72瀏覽量

10724

原文標題:接觸孔工藝(Contact Process)

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

一文詳解肖特基接觸和歐姆接觸

PCB盲孔、埋孔和通孔是什么

HDI線路板盤中孔處理工藝

pcb板樹脂塞孔和油墨塞孔的區別?

PCB郵票孔設計及工藝要點總結

pcb樹脂塞孔工藝,你知道如何操作嗎

詳解盤中孔工藝與空洞的關系

捷多邦帶你了解:PCB盲孔與埋孔的不同制造流程,工藝差異大揭秘!

激光增強接觸優化(LECO)工藝:光伏電池效率提升的關鍵

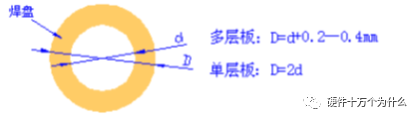

PCB 焊盤與孔設計工藝規范

接觸孔工藝(Contact Process)

接觸孔工藝(Contact Process)

評論