隨著摩爾定律的放緩,Chiplet成為持續(xù)提高SoC集成度和算力的重要途徑。目前業(yè)內(nèi)已有多家企業(yè)發(fā)布了基于Chiplet技術(shù)的芯片,Chiplet儼然已成為各芯片廠商進入下一個關(guān)鍵創(chuàng)新階段,并打破功率-性能-面積(PPA)天花板的一個絕佳技術(shù)選擇。

所謂Chiplet,可將不同功能的裸片(Die)通過2D或2.5D/3D的封裝方式組裝在一起,其好處是不同功能的Die可以采用不同的工藝制造,然后以異構(gòu)的方式集成在一起。但是到目前為止,實現(xiàn)Chiplet架構(gòu)一直非常困難。為了做到這一點,采用這一技術(shù)的早期廠商已將單片式芯片設(shè)計方法應(yīng)用于內(nèi)部定義的設(shè)計與驗證流程,并開發(fā)了自己的接口技術(shù)。但是,非聚合Die市場(即具備類似即插即用的靈活性及互操作性)的發(fā)展離不開行業(yè)標準和生態(tài)系統(tǒng)。通用Chiplet互連技術(shù)(UCIe)規(guī)范可以實現(xiàn)Chiplet的可定制與封裝級集成,可以說是Chiplet發(fā)展前路的一大助推劑,UCIe正在幫助我們迅速緊跟這種面向先進應(yīng)用的全新設(shè)計方式。

Chiplet技術(shù)為何騰飛?

隨著對芯片性能的要求日益提高,需要在更小的空間里集成更多的晶體管,SoC的尺寸正在接近芯片制造的上限。傳統(tǒng)的單片SoC變得太大且成本過高,無法通過先進設(shè)計進行生產(chǎn),并且良率風(fēng)險也隨之攀升。而Chiplet技術(shù)將SoC組件分開制造,再封裝到一起,則可以降低成本,減少浪費,并大大改善可靠性。 除了支持不同功能的組件選用不同工藝節(jié)點外,Chiplet架構(gòu)還允許將數(shù)字、模擬或高頻工藝的不同裸片集成到一起,甚至可以在設(shè)計中加入高度密集的3D內(nèi)存陣列,即高帶寬內(nèi)存(HBM)。

假設(shè)您需要開發(fā)一部設(shè)備,該設(shè)備的I/O接口(如以太網(wǎng)接口等)可能并不需要最前沿的工藝。按照Chiplet技術(shù)的思路,您可以在一個細化的層面以“形式遵循功能”的思路優(yōu)化PPA,如果在不同的設(shè)備上使用的I/O子系統(tǒng)是一樣的,還可以一次性制造所有I/O接口,從而借助生產(chǎn)規(guī)模獲得更低成本。相比之下,如果整個SoC都位于同一裸片上,無論功能如何,I/O接口都要與您最先進的功能采用相同的工藝,除了制作成本增加外,一旦設(shè)計中的某個組件出現(xiàn)故障,就會導(dǎo)致整體失效。

規(guī)模和模塊化所帶來的靈活性,也將幫助您應(yīng)對不斷縮小的上市時間窗口。具有標準功能的裸片可以混合并匹配,即獲得一種硬IP,從而讓您的工程人才專注于設(shè)計的差異化因素,以加快產(chǎn)品上市速度。 雖然上面的方式聽起來十分理想,但各個獨立的裸片在帶寬、互操作性和數(shù)據(jù)完整性方面具有很大差異,目前只有那些擁有足夠資源來支持裸片間定制互連開發(fā)的大公司才會采用這種技術(shù)。但是隨著這種更前沿設(shè)計方法的普及,裸片間的互連在本質(zhì)上已經(jīng)與互操作性相抵觸。 盡管存在這些挑戰(zhàn),預(yù)計到2024年,Chiplet市場的規(guī)模將增長至500億美元;而UCIe則是這一增長的關(guān)鍵推動力。

UCle為何成為Chiplet設(shè)計的首選標準?

其實為了應(yīng)對Chiplet設(shè)計中所面臨的挑戰(zhàn),行業(yè)出現(xiàn)了幾種不同的標準。但是UCIe是唯一具有完整裸片間接口堆棧的標準,其他標準都沒有為協(xié)議棧提供完整裸片間接口的全面規(guī)范,大多僅關(guān)注在特定層。而且UCIe支持2D、2.5D和橋接封裝,預(yù)計未來還會支持3D封裝。 UCIe不僅能滿足大部分每引腳8Gbps至16Gbps的設(shè)計,還能滿足從網(wǎng)絡(luò)到超大規(guī)模數(shù)據(jù)中心等高帶寬應(yīng)用中每引腳32Gbps的設(shè)計;換言之,該標準將滿足當前和未來的帶寬發(fā)展。UCIe有兩種不同的封裝類型:

用于先進封裝的UCIe,如硅襯墊、硅橋或再分配層(RDL)扇出

用于標準封裝的UCIe,如有機襯底或?qū)訅喊?/p>

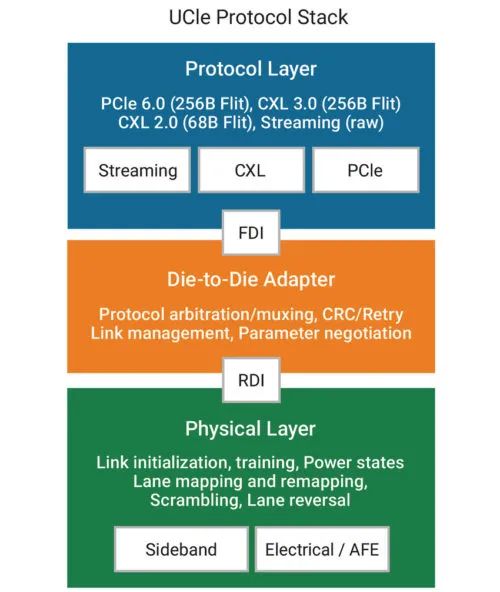

UCIe堆棧本身擁有三層:

最上端的協(xié)議層通過基于流量控制單元(FLIT)的協(xié)議實現(xiàn),確保最大效率和降低延遲,支持最流行的協(xié)議,包括PCI Express(PCIe)、Compute Express Link(CXL)和/或用戶定義的流協(xié)議。

第二層用于對協(xié)議進行仲裁與協(xié)商,以及通過裸片間適配器進行連接管理。基于循環(huán)冗余檢查(CRC)和重試機制,該層還包括可選的錯誤糾正功能。

第三層為物理層(PHY),規(guī)定了與封裝介質(zhì)的電氣接口,是電氣模擬前端(AFE)、發(fā)射器和接收器以及邊帶通道允許兩個裸片之間進行參數(shù)交換與協(xié)商的層級。邏輯PHY實現(xiàn)了連接初始化、訓(xùn)練和校準算法,以及測試和修復(fù)功能。

▲圖:UCIe協(xié)議棧示意圖

EDA廠商推動UCle的發(fā)展

作為EDA和IP解決方案的領(lǐng)導(dǎo)者,新思科技已成為UCIe的成員之一,我們期待著未來對UCIe規(guī)范做出貢獻,與廣大UCIe的支持者們積極推動構(gòu)建健康的UCIe生態(tài)系統(tǒng)。為了簡化UCIe設(shè)計路徑,新思科技推出了完整的UCIe設(shè)計解決方案,包括PHY、控制器和驗證IP(VIP):

PHY──支持標準和高級封裝選項,可采用先進的FinFET工藝,獲得高帶寬、低功耗和低延遲的裸片間連接。

控制器IP──支持PCIe、CXL和其它廣泛應(yīng)用的協(xié)議,用于延遲優(yōu)化的片上網(wǎng)絡(luò)(NoC)間連接及流協(xié)議;例如與CXS接口和AXI接口的橋接。

VIP──支持全棧各層的待測設(shè)計(DUT);包括帶有/不帶有PCIe/CXL協(xié)議棧的測試平臺接口、用于邊帶服務(wù)請求的應(yīng)用編程接口(API),以及用于流量生成的API。協(xié)議檢查和功能覆蓋位于每個堆棧層和信令接口,實現(xiàn)了可擴展的架構(gòu)和新思科技定義的互操作性測試套件。

新思科技的解決方案不僅帶來了穩(wěn)健、可靠的裸片間連接,并具有可測試性功能,可用于已知良好的裸片,和用于糾錯的CRC或奇偶校驗。它將使芯片設(shè)計企業(yè)能夠在Die間建立無縫互連,實現(xiàn)最低的延遲和最高的能效。

對于Chiplet設(shè)計,由于多個流協(xié)議而增加的有效載荷可能需要數(shù)天甚至數(shù)月的時間來實現(xiàn)仿真,從而限制了其實用性。對此,新思科技還推出了UCIe的驗證IP,用戶需要首先創(chuàng)建各種單節(jié)點和多節(jié)點模型,模擬這些簡化的系統(tǒng)以檢查數(shù)據(jù)的完整性。利用新思科技 ZeBu仿真系統(tǒng)在具有多協(xié)議層的更高級別系統(tǒng)場景中進行測試,然后再使用新思科技 HAPS原型驗證系統(tǒng)進行原型設(shè)計。也就是說,新思科技的驗證IP從模型到仿真、模擬,再到原型驗證,確保了芯片投產(chǎn)前的無縫互操作性。

在摩爾定律逼近極限的今天,Chiplet的發(fā)展已是大勢所趨,不過其前路仍然面臨著不少挑戰(zhàn),需要產(chǎn)業(yè)界各個產(chǎn)業(yè)鏈的廠商支持,才能最終迎來其發(fā)展騰飛。

-

chiplet

+關(guān)注

關(guān)注

6文章

416瀏覽量

12558 -

UCIe

+關(guān)注

關(guān)注

0文章

44瀏覽量

1619

原文標題:Chiplet是大勢所趨,完整UCIe解決方案應(yīng)對設(shè)計挑戰(zhàn)

文章出處:【微信號:elecfans,微信公眾號:電子發(fā)燒友網(wǎng)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

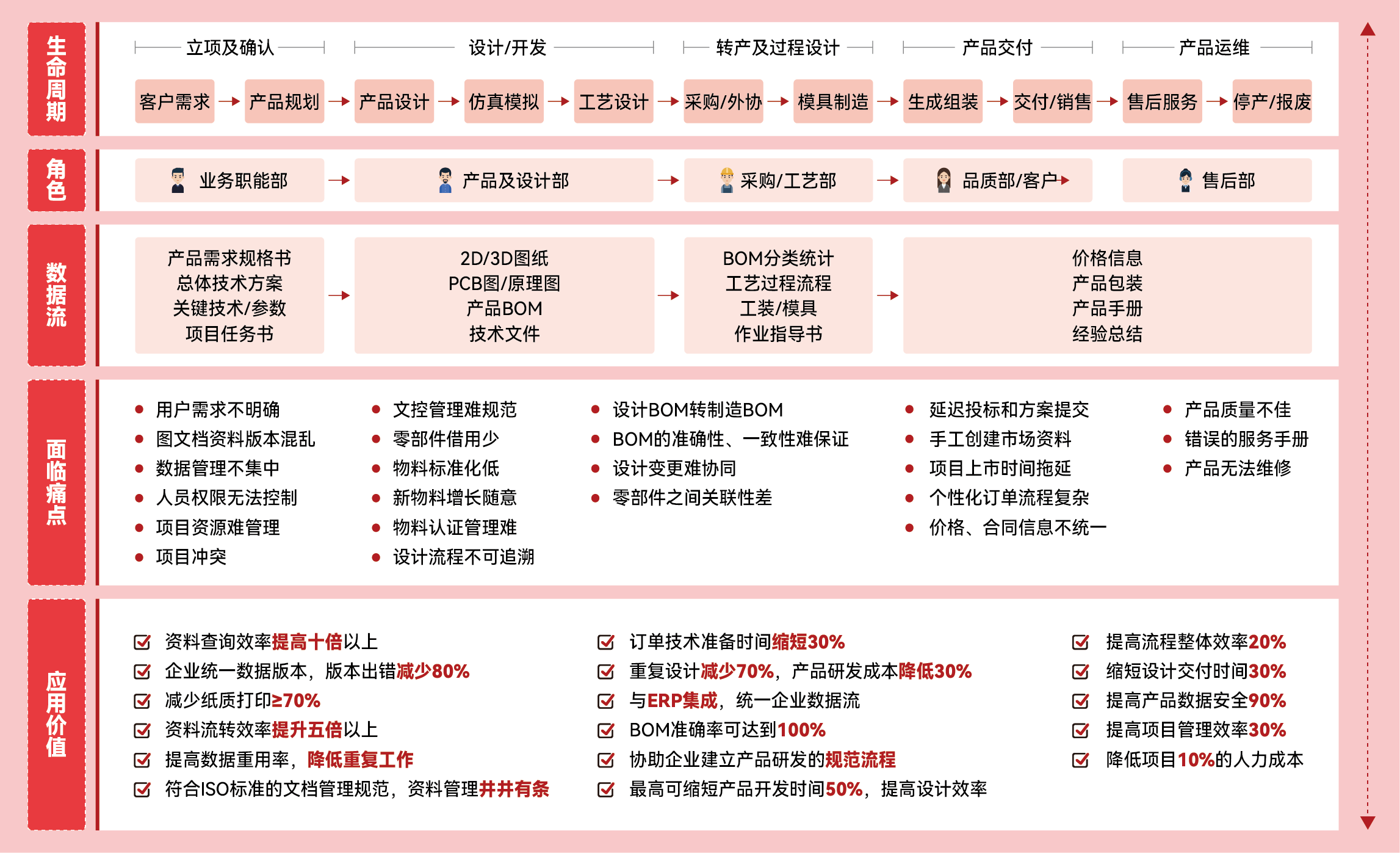

PLM制造業(yè)解決方案:應(yīng)對挑戰(zhàn),提升效率與競爭力

UCIe規(guī)范引領(lǐng)Chiplet技術(shù)革新,新思科技發(fā)布40G UCIe IP解決方案

降本增效大勢所趨,電控MCU內(nèi)卷加劇,本土廠商如何破局?

新思科技發(fā)布40G UCIe IP,加速多芯片系統(tǒng)設(shè)計

新思科技發(fā)布全球領(lǐng)先的40G UCIe IP,助力多芯片系統(tǒng)設(shè)計全面提速

天合光能:TOPCon組件成為主流,700W+大勢所趨

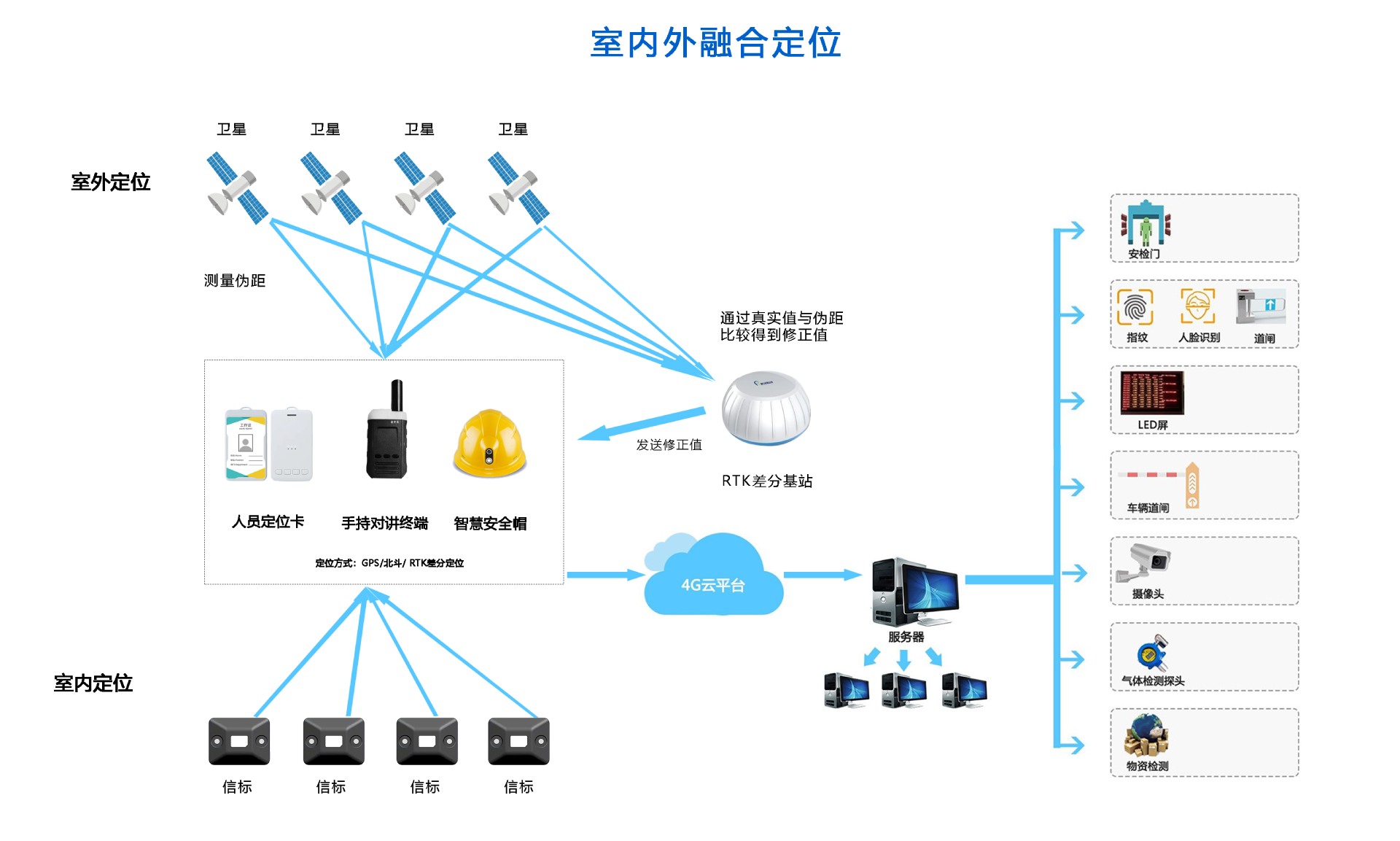

園區(qū)人員定位怎么做?分享智慧園區(qū)人員定位系統(tǒng)解決方案

西門子EDA創(chuàng)新解決方案確保Chiplet設(shè)計的成功應(yīng)用

瑞薩基于IEC61508的功能安全解決方案介紹(1)

IPv6 是大勢所趨,也是機遇所在

你計算過車輛線束的最大繞線長度嗎?

惡劣環(huán)境對互連解決方案的影響及應(yīng)對思路

Chiplet 互聯(lián):生于挑戰(zhàn),贏于生態(tài)

深度詳解UCIe協(xié)議和技術(shù)

Chiplet是大勢所趨,完整UCIe解決方案應(yīng)對設(shè)計挑戰(zhàn)

Chiplet是大勢所趨,完整UCIe解決方案應(yīng)對設(shè)計挑戰(zhàn)

評論