在SV功能覆蓋率中通常coverpoint中變量的某些比特我們并不關心。例如對于addr[3:0],我們只希望其中的每一個比特都覆蓋過“0”和“1”。

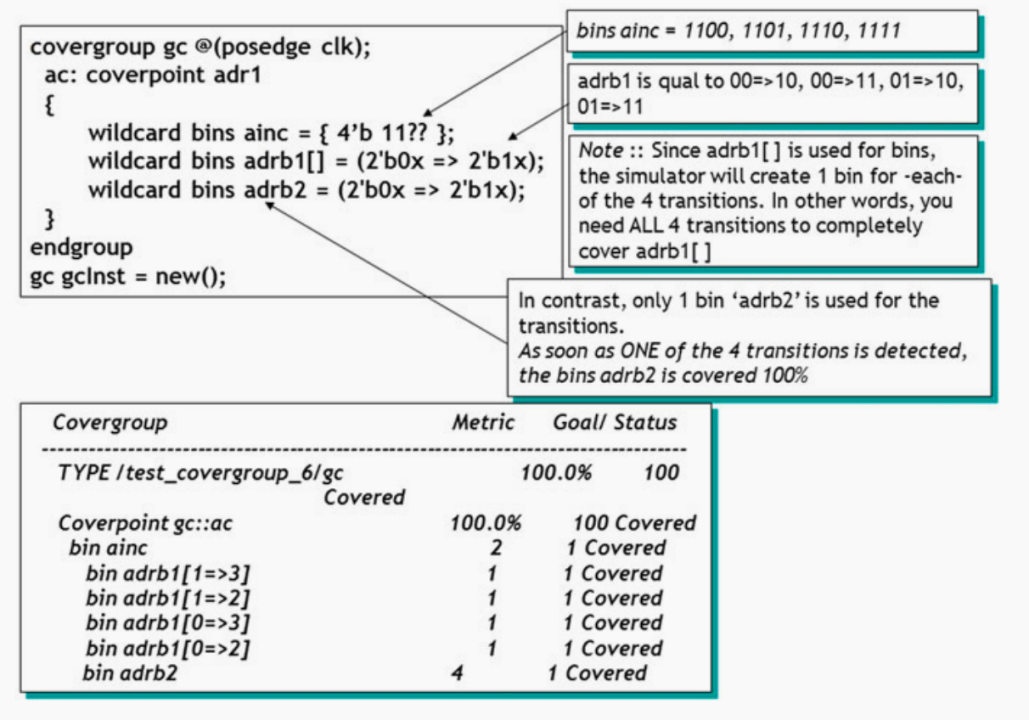

在上圖中,可以用wildcard ' x '或' z '或' ?’表明某些比特我們并不關心,不管它是“0”還是“1”。

wildcard bins ainc = {4’b11??}

表示我們希望能夠覆蓋比特[3:2]為2’b11的場景,不關心比特[1:0],所以

4’b1100、4’b1101、4’b1110、4’b1111

都算完成了對于4’b11??的覆蓋。

審核編輯:劉清

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

Address

+關注

關注

0文章

6瀏覽量

7561 -

BIN文件

+關注

關注

0文章

26瀏覽量

8268

原文標題:SV 功能覆蓋率中的wildcard bin

文章出處:【微信號:芯片驗證工程師,微信公眾號:芯片驗證工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

關于SpinalHDL中的驗證覆蓋率收集簡單說明

SpinalHDL 1.4.2中開始支持,在我們通過sbt構建項目時,build.sbt的依賴項配置如下:開啟覆蓋率收集功能 有注意上文所給例子的小伙伴或許已經注意到,我們已經開啟了覆蓋率

發表于 06-24 15:56

重點厘清覆蓋率相關的概念以及在芯片開發流程中跟覆蓋率相關的事項

較麻煩,工程師們需要針對各種各樣的功能和應用場景,使用SV等驗證語言去實現覆蓋率模型(Coverage Model)或斷言(Assertion),并且從大量的回歸測試(Regression)中

發表于 09-14 11:57

Systemverilog覆蓋率的合并和計算方式

說下sv里覆蓋率的計算方式。 說明下,coverpoint有兩種,1種是用戶自動指定bins,另1種是系統自動生成bins。1個bin如果沒有轉換或者值,那么這個bin的結果會從Ci

發表于 03-21 14:24

針對功能覆蓋率的驗證過程

針對功能覆蓋率的驗證過程神州龍芯集成電路設計公司徐偉俊 楊鑫 陳先勇 夏宇聞[摘要]:本文在介紹傳統驗證過程及其局限性的基礎上,闡述了針對功能覆蓋率

發表于 12-23 16:12

?13次下載

基于覆蓋率的功能驗證方法

隨著半導體技術的發展,驗證已經逐漸成為大規模集成電路設計的主要瓶頸。首先介紹傳統的功能驗證方法并剖析其優缺點,然后引入傳統方法的一種改進基于覆蓋率的驗證方法,最后

發表于 06-29 10:46

?22次下載

Verilog代碼覆蓋率檢查

Verilog代碼覆蓋率檢查是檢查驗證工作是否完全的重要方法,代碼覆蓋率(codecoverge)可以指示Verilog代碼描述的功能有多少在仿真過程中被驗證過了,代碼覆蓋率分析包括以

發表于 04-29 12:35

?8349次閱讀

IP開發時如何考慮復用覆蓋率

如何在開發IP的同時去鞏固集成和復用覆蓋率?IP的某些功能和性能是可以配置的,需要考慮的是IP被各種合理配置后的工作是否都能夠正常,將功能覆蓋率先整理為層次化的抽象

汽車功能安全診斷覆蓋率的評估

例一種安全機制可以在本附件中具有較高的通用典型診斷覆蓋率,但如果所使用的診斷測試間隔大于符合相關容錯時間間隔所需的診斷測試間隔,則避免違反安全目標的具體診斷覆蓋率將低得多。

嵌入式代碼覆蓋率統計方法和經驗

代碼覆蓋率是衡量軟件測試完成情況的指標,通常基于測試過程中已檢查的程序源代碼比例計算得出。代碼覆蓋率可以有效避免包含未測試代碼的程序被發布。 1. 問題背景 代碼覆蓋(Code cov

統計嵌入式代碼覆蓋率的方法和經驗

代碼覆蓋率是衡量軟件測試完成情況的指標,通常基于測試過程中已檢查的程序源代碼比例計算得出。代碼覆蓋率可以有效避免包含未測試代碼的程序被發布。 1. 問題背景 代碼覆蓋(Code cov

怎么才能寫出高覆蓋率的Verilog代碼?

芯片前端工程中,測試驗證的核心理念:以提高覆蓋率為核心。設計工程師需要關心的主要有行覆蓋率(Block),條件覆蓋率(Expression),翻轉覆

高覆蓋率的Verilog代碼的編寫技巧

設計工程師需要關心的主要有行覆蓋率(Block),條件覆蓋率(Expression),翻轉覆蓋率(Toggle),狀態機覆蓋率。本文從ASIC設計的角度上來討論,如何寫出高

SV功能覆蓋率中的wildcard bin介紹

SV功能覆蓋率中的wildcard bin介紹

評論