現在,這些芯片的性能和時鐘頻率越來越高,以滿足互聯網上的高速數據流量或密集型CPU任務本身。

集成電路是任何電子設備的核心。現在,這些芯片的性能和時鐘頻率越來越高,以滿足互聯網上的高速數據流量或密集型CPU任務本身。時序/速度是這些設備最重要的方面,公司正在推動自己在更短的時間內實現這一高性能目標。因此,時序/簽核是解決ASIC芯片設計高吞吐量要求以決定整體上市時間的一個非常關鍵的階段。

有多種 EDA 工具可用于通過數據路徑優化進行時序分析和時序修復。但是,本文的主要重點是提供使用延遲時鐘技術的剩余設置時序修復的見解/算法,而不會影響其他時序分析矩陣。

修復安裝程序沖突的基本方法

當數據路徑與捕獲翻牌時捕獲的時鐘相比緩慢時,會發生安裝沖突。考慮到這一點,有各種方法可以修復設置。

數據路徑優化

有很多方法可以修復優化的數據路徑,如 Upsize、vtswap 和在數據路徑中插入緩沖區中繼器等。這可以使用簽核工具的生態生成功能來實現。運行一輪計時修復后,簽核計時工具已應用所有可能的數據路徑優化技術。它無法通過進一步優化數據路徑來修復剩余的違規,要么可能導致其他路徑的質量下降,要么沒有進一步的優化數據路徑的范圍。

使用有用的傾斜

為了修復剩余的設置沖突,我們別無選擇,只能在簽核工具中修復路徑。

觸摸時鐘路徑是這里的解決方案之一。

如果數據路徑已基本優化,則修復設置沖突的最后一個選項仍然是使用“有用的傾斜”概念。有用的偏斜涉及兩種方法:早時鐘和晚時鐘。減少啟動時鐘延遲或增加捕獲時鐘延遲。但是,要更改時鐘,必須確保上游(對于早時鐘)和下游(對于晚時鐘)的路徑不違規。

早期發射時鐘

較早的時鐘需要在PnR實現工具中檢查物理網絡/小區位置,然后確定早期時鐘的適當候選者。同樣為了在簽核工具中實現早期時鐘生態,提取的r / c對于新網絡將有更大的差異。因此,早期時鐘在實現和簽核工具之間的RC中產生最大的影響。為了實現早期時鐘,除了物理更改外,還使用了斷開連接/連接等邏輯更改,因此請始終運行形式。

延遲捕獲時鐘

對于較晚的時鐘,新添加的時鐘單元將被放置在附近以捕獲翻牌,并且新創建的網絡的凈長度將非常小。因此,R/C提取數據仍然有效,因為RC值變化的影響很小。最好使用“延遲時鐘”方法創建生態。

為什么我們專注于晚時鐘而不是早時鐘

如前所述,延遲時鐘對eco實現工具和簽核定時工具之間的RC相關性的影響最小。如果有多個路徑匯聚在同一終結點上,則很容易根據終結點分離路徑并在終結點上應用安裝程序修復,可以修復大多數設置路徑。

多場景分析功能可以輕松檢查同一會話中的設置/保持違規。

?實現

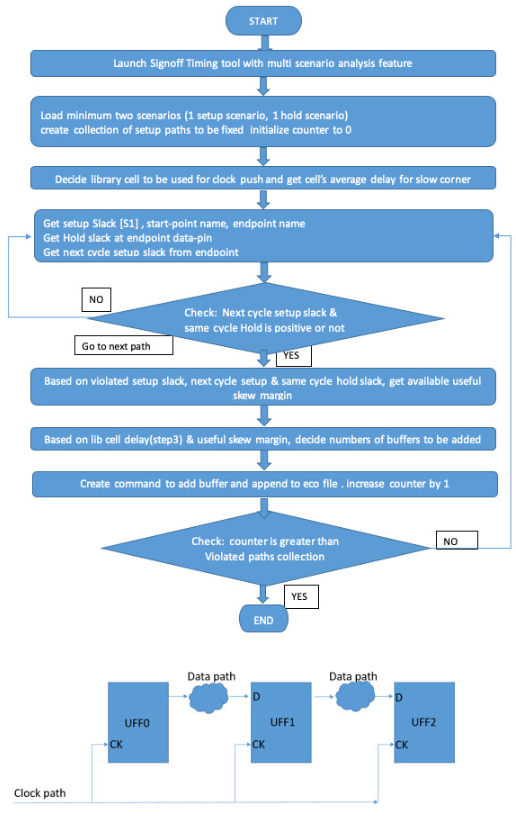

我們遵循以下算法,使用延遲時鐘創建設置生態。

將上述流程圖步驟合并到腳本中需要一次性工作。生成腳本后,它會減少分析所有路徑和生成時序生態的總時間。

我們能夠部署上述算法中的所有步驟,并在采用深亞微米技術的設計上運行它。腳本可以分析所有設置路徑并創建兩個輸出文件。1. 總結.csv 和 2.late_clock_eco.tcl

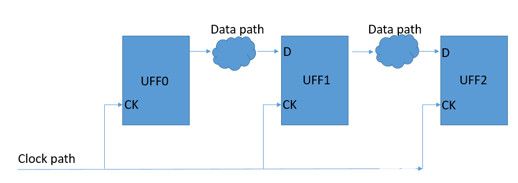

考慮從 UFF0/CK 到 FFF1/D 違反設置的映像 2 場景。 [示例輸出如下所示]。

summary.csv

startpoint,endpoint,slack,setup_from_ep,hold_on_ep,late_clock_count

UFF0/CK,UFF1/D,-0.040,-0.051,0.080,0

late_clock_eco.tcl

add_buffer_on_flop_clock_pin UFF1

add_buffer_on_flop_clock_pin UFF1

add_buffer_on_flop_clock_pin UFF1

對于具有設置/保持的設計,跨多個場景違規。感興趣的設置/保持場景可以加載到簽核工具中,腳本可以在不干擾未違反的設置/保持路徑的情況下生成 eco。

如果違反下一個周期設置,腳本將不會在 UFF1/CK 上添加任何緩沖區。同樣,如果在 UFF1/D 上違反了保留,腳本將不會在 UFF1/CK 上添加任何緩沖區。

在增加下一個周期路徑 [UFF1/CK 到 UFF2/D] 的設置裕量后,增加同一周期的保持裕量 [UFF1/D] 和運行腳本將增加緩沖區。

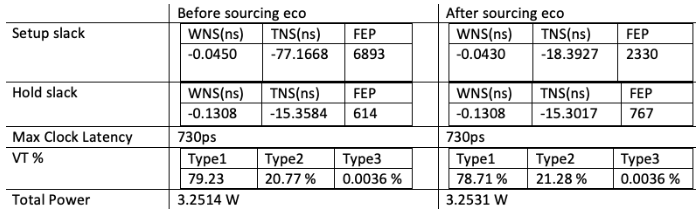

個案研究

上述流/腳本在一個塊上使用,以修復設置沖突。在使用此腳本之前,進行了以下假設:

參考塊在 PnR 中具有中度擁塞。對于高度擁擠的設計,緊湊的布線資源或高利用率的設計將沒有足夠的空間來實現生態。

實施/PNR 工具和簽核計時工具之間的關聯是正確的。

STA工程師了解后端實現工具,如果遇到任何問題來實現eco,能夠進行調試。

以下是設計復雜性:

技術:深亞微米

放置的細胞數(大約) : 1100 K

利用率(標準單元格行/總計):40%/50%

添加的遲到時鐘單元總數:7250

QOR比較

在上述算法中進一步添加

對于復雜的高速設計,目標插入延遲/最大延遲至關重要。限制是在修復時序沖突時不超過最大延遲。這種特殊情況也可以添加到上面的算法中。

STA 分析變得越來越重要,并且是滿足高性能計算、高級圖形和網絡 SOC的高吞吐量要求的關鍵領域,以決定當今具有挑戰性的低節點技術時代的總體上市時間。創建新的算法和腳本來修復建立/保持時序問題。這將有助于減少時序簽核關閉,從而縮短上市時間。即使在數據路徑完全優化之后,使用延遲時鐘進行有用的偏斜確實有助于更快、更準確地收斂時序,而無需任何手動操作。

審核編輯:郭婷

-

芯片

+關注

關注

454文章

50460瀏覽量

421971 -

集成電路

+關注

關注

5382文章

11396瀏覽量

360952

發布評論請先 登錄

相關推薦

請問lmk04828-EP設置DCLKx的模擬延遲失敗,導致時鐘不穩定的原因?怎么解決?

PLC的IP沖突如何解決(NAt物聯網解決方案)

使用延遲時鐘的時序關鍵復雜設計中的設置沖突修復

使用延遲時鐘的時序關鍵復雜設計中的設置沖突修復

評論