精確的熱分析在很多電子產品設計中都有著舉足輕重的作用,在高端的PCB設計中尤為突出。熱分析的結果常常會影響PCB的機械層設計和產品的外殼設計:是否需要安裝散熱片、散熱風扇等。如果安裝散熱風扇,往往需要降低其噪音,這將使得機械層設計變得更加復雜。

熱分析的最終目標是要使得整個系統能夠穩定地運行,特別是保證芯片的結溫不能超過安全閾值。如果無法保證這一點,那么FPGA芯片在性能指標、可靠性、使用壽命等方面將會大打折扣,比如系統不斷的重啟,FPGA的時序無法滿足要求,甚至無法保證其功能的正確運行。熱分析必須考慮到FPGA運行的各種實際環境:從恒溫實驗室的理想環境到外太空極寒/極熱的惡劣環境。在后續介紹的功耗分析,實際上和熱分析有緊密的關系。

整個FPGA設計的總功耗由三部分功耗組成:1. 芯片靜態功耗;2. 設計靜態功耗;3. 設計動態功耗。

1、芯片靜態功耗:FPGA在上電后還未配置時,主要由晶體管的泄漏電流所消耗的功耗

2、設計靜態功耗:當FPGA配置完成后,當設計還未啟動時,需要維持I/O的靜態電流,時鐘管理和其它部分電路的靜態功耗

3、設計動態功耗:FPGA內設計正常啟動后,設計的功耗;這部分功耗的多少主要取決于芯片所用電平,以及FPGA內部邏輯和布線資源的占用。

所以,前兩部分的功耗取決于FPGA芯片及硬件設計本身,很難有較大的改善。可以優化是第3部分功耗:設計動態功耗,而且這部分功耗占總功耗的90%左右,因此所以降低設計動態功耗是降低整個系統功耗的關鍵因素

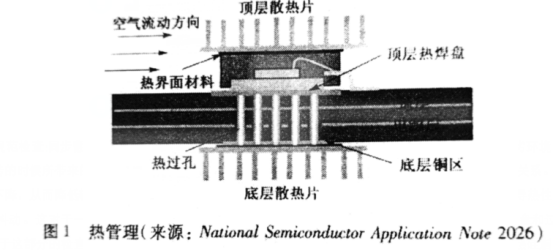

圖1顯示了對FPGA芯片導熱性能產生重要影響的機械元件:頂層和底層的散熱片、焊盤和過孔。除此之外,焊盤本身的尺寸和質量,是否使用導熱硅脂,空氣對流的大小,PCB的尺寸和層數,這些因素都會影響到最終的導熱性能指標。

靜態功耗分析

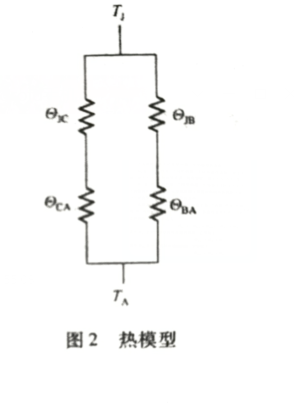

以下公式定義了環境溫度、芯片恒溫、功耗和電阻之間的關系: Tj=(θja·Pd)+Ta Tj代表芯片的結溫,反映了半導體器件能夠承受的最高溫度,每個芯片的器件手冊都有該指標。比如Virtex-6芯片的最高Tj為125℃,但是FPGA工具在做靜態時序分析和功耗計算時,其默認值通常設定為85℃。不同FPGA芯片的結溫指標,包括其工作范圍、最大最小值、默認值,在DC and Switching Characteristics數據手冊上都會有詳細的介紹。 在上述公式中,Ta代表環境溫度,PD代表功耗。而Oja是“內核-外環境”之間的熱阻,它代表了材料導熱的能力,其物理單位是"℃/W”。 在各種熱分析中經常使用圖2中的模型和參數。 θjc是“內核-外殼"之間的熱阻,不同的器件的值一般也不同。對于Virtex-6的封裝來說,其典型值一般小于0.20 ℃/W。 θca是“外殼-外環境”之間的熱阻,它等效于FPGA芯片之上的散熱片+散熱風扇+導熱硅脂+其他材料的所有熱阻之和,空氣對流所帶來的影響也要算在其中。 從圖2可以看出,整個散熱途徑有2條:“內核-外殼-外環境"和“內核- PCB -外環境”。由于這2條路徑是并行的,因此 總的熱阻θja可以表達為 θOja= (θcA x θjba)/(θjca+ θjba) 其中Ojca是封裝頂層到外環境的熱阻,它等效于 θjca= θjc+ θca 其中θjba是PCB到外環境的熱阻,它等效于 θjba=θjb+θba

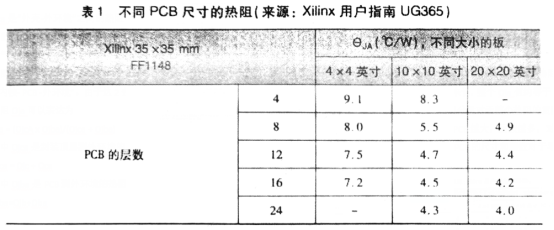

在熱分析的建模過程中,還需要將PCB本身的熱阻計算在內。對于層數較少的小PCB來說,整個θja值約等于θjca。因為當θjba足夠大的時候,該分量對于整個熱阻的貢獻將變得非常小,甚至可以忽略。PCB越大,層數越多,對應的θjba值也就越大。表1說明了PCB的尺寸和層數對于導熱性能的影響。

對于整個熱分析而言,最重要就是正確地建立熱模型。從表2可以看出,如果沒有將PCB的熱阻考慮進去,那么最后的結果將變的極不準確。

靜態功耗散熱方法

空氣散熱

對于低端、小封裝、功托大概在1-6W左右的FPGA芯片而言,一般使用空氣對流或者加裝散熱片的方式即可散熱。 散熱片的作用在于將芯片表面的熱迅速帶走,因此通常使用鋁或者銅這樣的高導熱金屬作為散熱片的材料。散熱片通常具有較大的表面積,這樣能夠更加快速地進行散熱。散熱片和芯片之間的接觸面積對于散熱來說非常重要,因此使用導熱硅脂將散熱片和芯片表面緊緊相連,則能夠更進一步地加快熱的傳導。 在較好的空氣對流環境中,功耗在4-10 W左右的芯片,使用散熱片將是非常好的選擇。

主動散熱

對于功耗在8-25W、采用離端大封裝的芯片,使用散熱片加風扇的組合能夠更好地達到散熱的效果。 舉例 通過給定的結溫和環境溫度,計算出最大允許的功耗: Tj= +85℃ Ta=+55℃ 器件為Virtex-6芯片,其中熱阻Ojc =0. 20℃/W。 散熱片和風扇的熱阻: Oca=1. 80℃/W, Ojb=0.40℃/W. Oba =2.60℃/W。 通過以下逐個公式的迭代,可以計算出功耗PD: Tj=(OjaxOd)+Ta Oja= (Ocax Ojba)/(Ojca+ Ojba) Ojca= Ojc+ Oca=0.2 + 1.8= 2.0℃/W OjBA = Ojb+OBA =0.4 +2.6 = 3. 0℃/W Oja=(2.0x3.0)/(2.0+3.0) = 1.2℃/W Pd=(Tj- Ta)/Oja= (85 -55)/1.2 = 25 w 通過上述正公式可以看出,在給定芯片結溫、環境溫度及熱阻的條件下,整個FPGA芯片的功耗不會超過25 w。

動態功耗的優化設計方法

算法優化

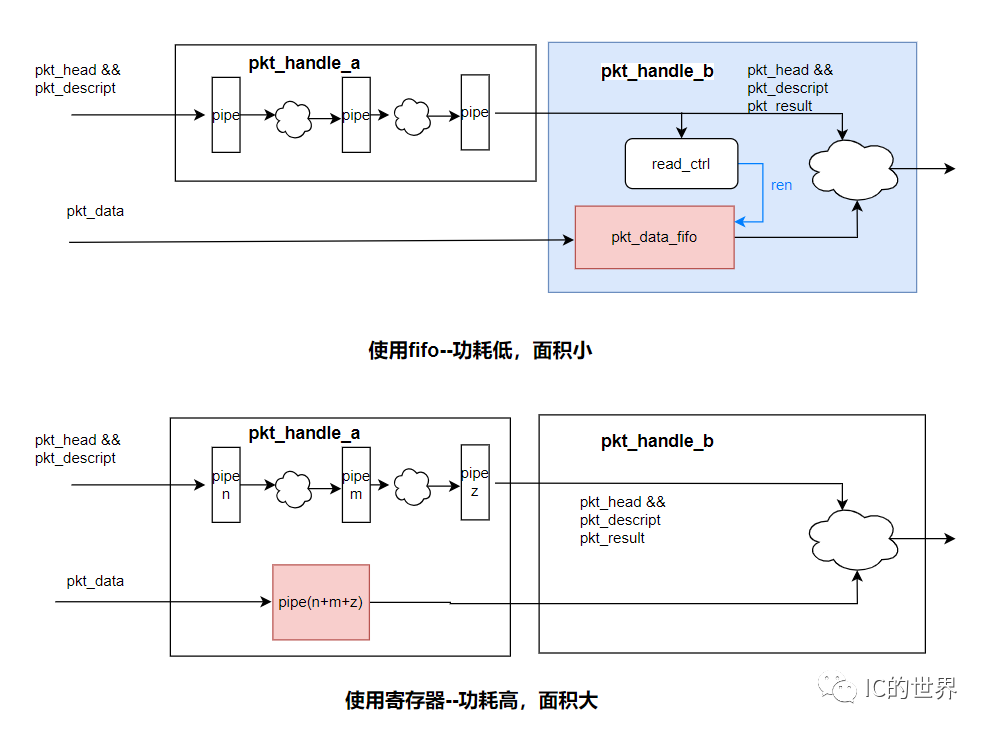

算法優化可分為兩個層次說明:實現結構和實現方法 首先肯定需要設計一種最優化的算法實現結構,設計一種最優化的結構,使資源占用達到最少,當然功耗也能降到最低,但是還需要保證性能,是FPGA設計在面積和速度上都能兼顧。比如在選擇采用流水線結構還是狀態機結構時,流水線結構同一時間所有的狀態都在持續工作,而狀態機結構只有一個狀態是使能的,顯而易見流水線結構的功耗更多,但其數據吞吐率和系統性能更優,因此需要合理選其一,使系統能在面積和速度之間得到平衡; 另一個層面是具體的實現方法,設計中所有吸收功耗的信號當中,時鐘是罪魁禍首。雖然時鐘可能運行在100MHz,但從該時鐘派生出的信號卻通常運行在主時鐘頻率的較小分量(通常為12%~15%)。此外,時鐘的扇出一般也比較高。這兩個因素顯示,為了降低功耗,應當認真研究時鐘。首先,如果設計的某個部分可以處于非活動狀態,則可以考慮禁止時鐘樹翻轉,而不是使用時鐘使能。時鐘使能將阻止寄存器不必要的翻轉,但時鐘樹仍然會翻轉,消耗功率。其次,隔離時鐘以使用最少數量的信號區。不使用的時鐘樹信號區不會翻轉,從而減輕該時鐘網絡的負載。

資源使用效率優化

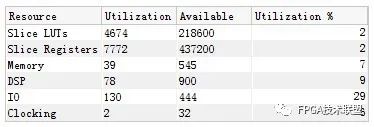

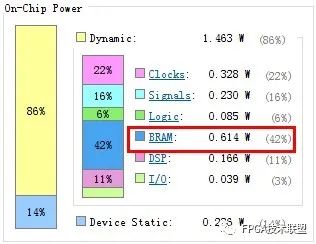

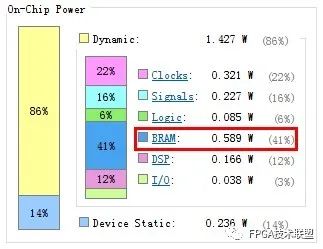

資源使用效率優化是介紹一些在使用FPGA內部的一些資源如BRAM,DSP48E1時,可以優化功耗的方法。FPGA動態功耗主要體現為存儲器、內部邏輯、時鐘、I/O消耗的功耗。 其中存儲器是功耗大戶,如xilinx FPGA中的存儲器單元Block RAM,因此在這邊主要介紹對BRAM的一些功耗優化方法。 如圖5中實例,雖然BRAM只使用了7%,但是其功耗0.601W占了總設計的42%,因此優化BRAM的功耗能有效地減小FPGA的動態功耗。

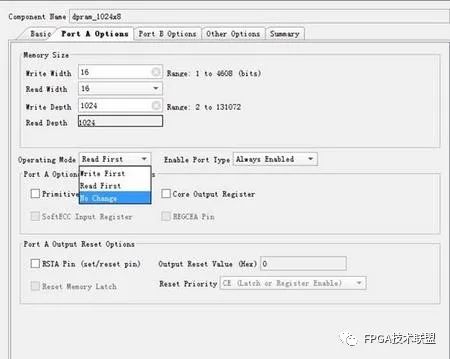

圖5 下面介紹一下優化BRAM功耗的方法: a) 使用“NO CHANGE”模式:在BRAM配置成True Dual Port時,需要選擇端口的操作模式:“Write First”,“Read First” or “NO CHANGE”,避免讀操作和寫操作產生沖突,如圖6所示;其中“NO CHANGE”表示BRAM不添加額外的邏輯防止讀寫沖突,因此能減少功耗,但是設計者需要保證程序運行時不會發生讀寫沖突。

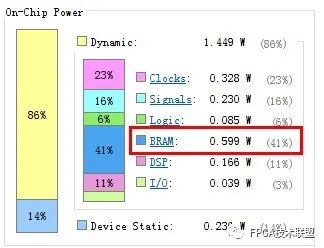

圖6 圖5中的功耗是設置成“Write First”時的,圖7中是設置成“NO CHANGE”后的功耗,BRAM的功耗從0.614W降到了0.599W,因為只使用了7%的BRAM,如果設計中使用了大量的BRAM,效果能更加明顯。

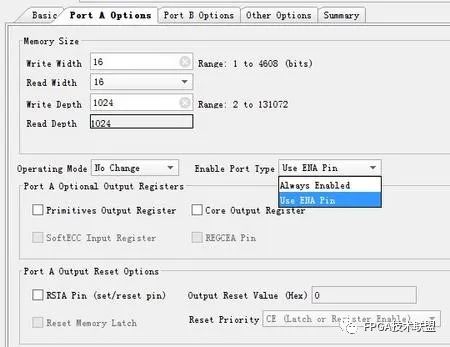

圖7 b) 控制“EN”信號:BRAM的端口中有clock enable信號,如圖8所示,在端口設置中可以將其使能,模塊例化時將其與讀/寫信號連接在一起,如此優化可以使BRAM在沒有讀/寫操作時停止工作,節省不必要的功耗。

圖8 如圖9所示為控制“EN”信號優化后的功耗情況,BRAM功耗降到了0.589W

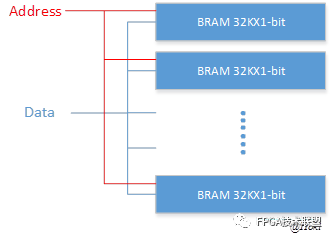

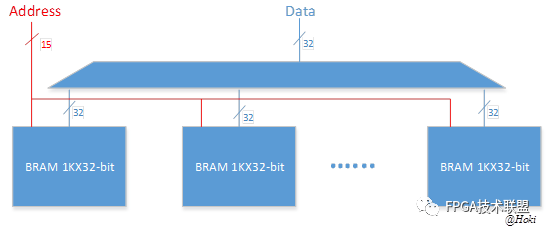

圖9 c) 拼深度:當設計中使用了大量的存儲器時,需要多塊BRAM拼接而成,如需要深度32K,寬度32-bit,32K32Bit的存儲量,但是單塊BRAM如何配置是個問題?7 series FPGA中是36Kb 的BRAM,其中一般使用32Kb容量,因此可以配置成32K1-bit或者1K*32-bit,多塊BRAM拼接時,前者是“拼寬度”(見圖10),后者是“拼深度”(見圖11)。兩種結構在工作時,“拼寬度”結構所有的BRAM需要同時進行讀寫操作;而“拼深度”結構只需要其中一塊BRAM進行讀寫,因此在需要低功耗的情況下采用“拼深度”結構, 注:“拼深度”結構需要額外的數據選擇邏輯,增加了邏輯層數,為了降低功耗即犧牲了面積又犧牲了性能。

圖10

圖11 審核編輯 :李倩

-

FPGA設計

+關注

關注

9文章

428瀏覽量

26489 -

低功耗

+關注

關注

10文章

2362瀏覽量

103605 -

焊盤

+關注

關注

6文章

548瀏覽量

38094

發布評論請先 登錄

相關推薦

stm32低功耗設計技巧

萊迪思推出全新Certus-NX FPGA器件,加強低功耗、小型FPGA的領先地位

國產藍牙模組 | 低功耗藍牙應用

低功耗藍牙技術的特點 低功耗藍牙如何實現低功耗?

ESP32-S3模組是怎么配置低功耗模式的?低功耗模式下功耗大概是多少?

數據透傳選擇低功耗WiFi模塊還是選擇低功耗藍牙模塊?

一文讀懂低功耗藍牙的應用

FPGA的低功耗設計方法總結

FPGA的低功耗設計方法總結

評論