對于當前越來越多的高速信號設計而言,高速傳輸線基本上都是差分對(DDR5 數據線還是單端的)。差分對設計的好處就是正端和負端是幅值大小相等,方向相反的進行傳遞,當外界對其有干擾時,正負相互抵消所以抗干擾能力比較強,另外共模噪聲比較小,向外輻射的能量也少。

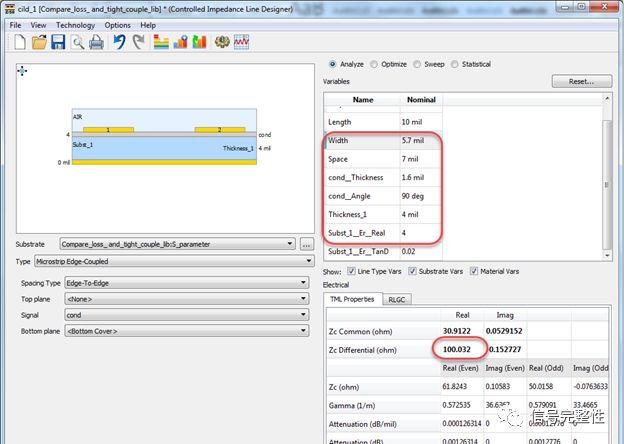

在高速電路的設計中,往往對傳輸線的阻抗有明確的要求,比如要求為100ohm,對于差分對而言,影響阻抗的因素很多,包括傳輸線的線寬、線間距、材料的介電常數、傳輸線到參考層的距離、傳輸線導體的厚度,下圖是ADSCILD的計算阻抗的示意圖,紅色圈圈出來的參數都會影響到阻抗:

所以如果只是為了保證阻抗,設計的方式有很多種。傳輸線間距寬和窄就是大家非常常見的一種設計狀況。

上圖中線寬為5.7mil,線間距為7mil,所以,為了保證阻抗不變,把線寬和線間距的值修改為4mil和3.49mil,其它參數都保持不變,計算出來的阻抗為100ohm,如下圖所示:

從上述兩組值中可以看出來,后一組可以認為是緊耦合,前一組為松耦合。下面從無源和有源兩個方向進行對比,即對比插入損耗和眼寬、眼高。

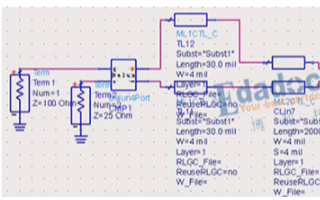

在ADS中搭建原理圖如下圖所示:

傳輸線的長度為6inch,分別針對兩組值進行仿真,獲得的仿真結果,如下圖所示為插入損耗的對比結果:

從上圖中可以看到插入損耗在低頻的時候,耦合的比較緊的時候稍微大一點,在超過5GHz之后,耦合的比較緊的時候損耗小一點。

下圖為兩種情況眼圖的對比:

從上圖中可以看到,松耦合的眼寬和眼高都比緊耦合大一點點,眼高大15mv,眼寬大0.5ps。

綜上所述,松耦合的損耗在低頻時(5GHz)稍微小一些,在高頻時(超過5GHz)大一些,但是都只相差一點點;眼圖雖然松耦合會好一點,但是相差也不大,松耦合的眼高大了15mV。理論上來講,為了保證阻抗一致性,在緊耦合時,線寬必然會細一些,在松耦合時線寬寬一點。在緊耦合時,隨著速率越高,趨膚效應越大,損耗也就會越大。

當然,以上只是從實驗上獲得的一些表象結果,也僅僅是從信號完整性的角度來分析的。如果要進一步的研究緊耦合和松耦合,可以考慮從多方面進行驗證和研究,比如保證線寬不變,改變介電常數,使線間距變化,研究結果的變化,或者再增加輻射的驗證等等。

審核編輯:劉清

-

傳輸線

+關注

關注

0文章

375瀏覽量

24003 -

ADS1220

+關注

關注

24文章

488瀏覽量

125150 -

高速信號

+關注

關注

1文章

223瀏覽量

17677 -

DDR5

+關注

關注

1文章

419瀏覽量

24104

發布評論請先 登錄

相關推薦

松耦合無線充電方案詳解

松耦合方式將成無線充電技術主流

使用Nios II緊耦合存儲器教程

PCB設計中耦合的松緊有何影響?

高速信號設計中緊耦合與松耦合之間的對比

高速信號設計中緊耦合與松耦合之間的對比

評論