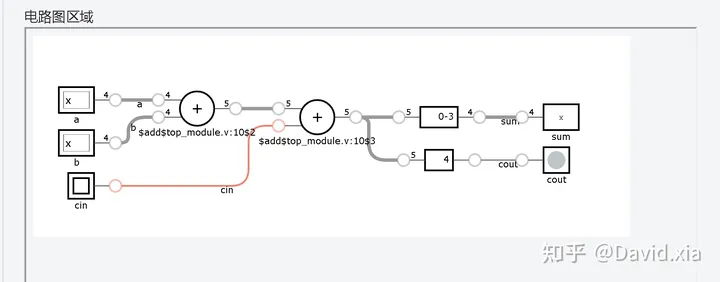

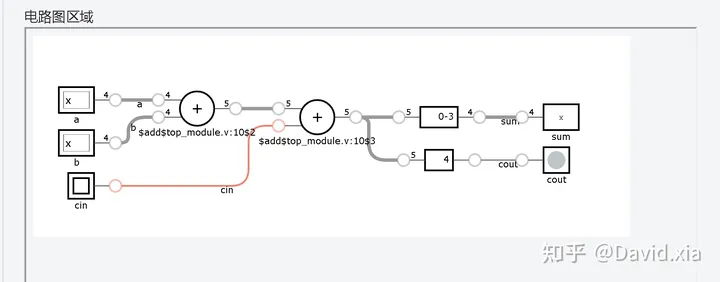

所謂邊沿檢測,就是檢測輸入信號即上升沿或者下降沿的檢測。邊沿檢測的電路很好實現(xiàn):上一時刻為低電平,而當(dāng)前時刻為高電平,此時就為上升沿;上一時刻為高電平,而當(dāng)前時刻為低電平,此時就為上升沿。通過邊沿采樣技術(shù)實現(xiàn)上升沿捕獲進(jìn)而實現(xiàn)外部信號的上升沿觸發(fā)。1、always @ (posedge signal)FPGA不便于處理此類觸發(fā)信號,除非外部輸入信號作為全局時鐘使用。另外眾所周知由于電路不能能避免抖動現(xiàn)象,所以用這個檢測方法是明顯不合理的。2、一級D觸發(fā)器實現(xiàn); 我們先看下代碼,always@(posedge clk or negedge rst_n) spi_cs_r0 <= spi_cs;? ? ? ??assign mcu_write_done = (~spi_cs_r0 & spi_cs) ? 1'b1 : 1'b0; //posedge正常工作,沒有復(fù)位的情況下,工作流程如下:(1)D觸發(fā)器經(jīng)過時鐘clk的觸發(fā),輸出spi_cs信號,保存了t0時刻的信號。(2)同時由spi_cs直接輸出到與門,保留了當(dāng)前時刻t1的觸發(fā)信號(3)經(jīng)過與門輸出信號pos_edge,neg_edgea) 只有t0時刻為高,且t1時候為低的時候,與門輸出高,此時為下降沿。b) 只有to時候為低,且t1時候為高的時候,與門輸出高,此時為上升沿。一級D觸發(fā)器在寄存器比較時,前一時刻通過D觸發(fā)器已經(jīng)統(tǒng)一到FPGA的時鐘域,而當(dāng)前時刻直接從外部輸入,與FPGA整體邏輯電路不在同一時鐘域,為提高系統(tǒng)的穩(wěn)定性我們可以采用第三種方法即二級D觸發(fā)器。3、二級D觸發(fā)器;我們?nèi)匀幌瓤创a:reg spi_cs_r0, spi_cs_r1; always@(posedge clk or negedge rst_n) spi_cs_r0 <= 1; spi_cs_r1 <= 1; spi_cs_r0 <= spi_cs; spi_cs_r1 <= spi_cs_r0;assign mcu_write_done = (~spi_cs_r1 & spi_cs_r0) ? 1'b1 : 1'b0;正常工作,沒有復(fù)位的情況下,工作流程如下:

(1)一級D觸發(fā)器經(jīng)過時鐘clk的觸發(fā),輸出當(dāng)前spi_cs信號,保存了t0時刻的信號。送往與門。(2)二級D觸發(fā)器經(jīng)過時鐘clk的觸發(fā),輸出上一時刻spi_cs信號,保存了t1時刻的信號。通過非們送往與門。(3)經(jīng)過與門輸出信號pos_edge,neg_edgea) 只有t0時刻為高,且t1時候為低的時候,與門輸出高,此時為下降沿。b) 只有to時候為低,且t1時候為高的時候,與門輸出高,此時為上升沿。利用CLK打兩拍,實現(xiàn)了上一時刻信號和本時刻信號和FPGA整體邏輯電路統(tǒng)一到同一時鐘域。這里要加兩級的觸發(fā)器的另一個原因,因觸發(fā)器跳轉(zhuǎn)產(chǎn)生滯后信號只能在時鐘的上升沿,而被檢測信號tigger并不一定是在一級觸發(fā)器跳轉(zhuǎn)的時鐘上升沿到來,這樣一級觸發(fā)器所產(chǎn)生的滯后信號與tigger相差就達(dá)不到一個CLK周期,所以產(chǎn)生的脈沖信號就小于一個CLK周期了,不利于后面電路對其的應(yīng)用。(1)將時鐘邊沿使能轉(zhuǎn)換為邊沿檢測使能,使時鐘同步化。(2)捕獲信號的突變(UART,SPI等信號使能突變)(1)增大CLK信號可以增強(qiáng)邊沿檢測的效率,但不能濾去跳變的雜波。(2)減少CLK可以有效濾去跳變的雜波,但不能及時檢測到邊沿跳變。(3)增加DFF能更好的濾除雜波,寄存信號,但同時檢測延時大。

至芯科技12年不忘初心、再度起航11月12日北京中心FPGA工程師就業(yè)班開課、線上線下多維教學(xué)、歡迎咨詢!

FPGA學(xué)習(xí)-你真的理解IIC嗎?

掃碼加微信邀請您加入FPGA學(xué)習(xí)交流群

歡迎加入至芯科技FPGA微信學(xué)習(xí)交流群,這里有一群優(yōu)秀的FPGA工程師、學(xué)生、老師、這里FPGA技術(shù)交流學(xué)習(xí)氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

原文標(biāo)題:FPGA學(xué)習(xí)-邊沿檢測技術(shù)

文章出處:【微信公眾號:FPGA設(shè)計論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

原文標(biāo)題:FPGA學(xué)習(xí)-邊沿檢測技術(shù)

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設(shè)計論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

相關(guān)推薦

FPGA(現(xiàn)場可編程門陣列)加速深度學(xué)習(xí)模型是當(dāng)前硬件加速領(lǐng)域的一個熱門研究方向。以下是一些FPGA加速深度學(xué)習(xí)模型的案例: 一、基于FPGA

![的頭像]() 發(fā)表于

發(fā)表于 10-25 09:22

?141次閱讀

今天給大俠帶來在FPAG技術(shù)交流群里平時討論的問題答疑合集(十四),以后還會多推出本系列,話不多說,上貨。

FPGA技術(shù)交流群目前已有十多個群,QQ和微信均覆蓋,有需要的大俠可以進(jìn)群,一起交流

發(fā)表于 09-27 20:53

邊沿觸發(fā)器是一種數(shù)字邏輯電路,其動作特點主要體現(xiàn)在以下幾個方面: 觸發(fā)方式:邊沿觸發(fā)器的動作是由輸入信號的邊沿變化引起的。當(dāng)輸入信號從低電平變?yōu)楦唠娖交驈母唠娖阶優(yōu)榈碗娖綍r,觸發(fā)器的狀態(tài)會發(fā)生改變

![的頭像]() 發(fā)表于

發(fā)表于 08-09 18:17

?810次閱讀

邊沿觸發(fā)器(Edge-Triggered Flip-Flop)是一種數(shù)字邏輯電路,其狀態(tài)變化由輸入信號的邊沿控制,即由輸入信號從低電平變?yōu)楦唠娖交驈母唠娖阶優(yōu)榈碗娖降乃查g觸發(fā)。邊沿觸發(fā)器廣泛應(yīng)用

![的頭像]() 發(fā)表于

發(fā)表于 08-09 17:29

?470次閱讀

隨著無人機(jī)技術(shù)的快速發(fā)展,無人機(jī)在軍事、民用、商業(yè)等多個領(lǐng)域的應(yīng)用日益廣泛。然而,無人機(jī)的廣泛使用也帶來了諸多挑戰(zhàn),如空域安全、隱私保護(hù)等問題。因此,開發(fā)高效、準(zhǔn)確的無人機(jī)檢測與識別技術(shù)顯得尤為重要。本文將深入探討基于深度

![的頭像]() 發(fā)表于

發(fā)表于 07-08 10:32

?1027次閱讀

在工業(yè)生產(chǎn)中,缺陷檢測是確保產(chǎn)品質(zhì)量的關(guān)鍵環(huán)節(jié)。傳統(tǒng)的人工檢測方法不僅效率低下,且易受人為因素影響,導(dǎo)致誤檢和漏檢問題頻發(fā)。隨著人工智能技術(shù)的飛速發(fā)展,特別是深度學(xué)習(xí)

![的頭像]() 發(fā)表于

發(fā)表于 07-08 10:30

?1143次閱讀

在計算機(jī)視覺領(lǐng)域,目標(biāo)檢測一直是研究的熱點和難點之一。特別是在小目標(biāo)檢測方面,由于小目標(biāo)在圖像中所占比例小、特征不明顯,使得檢測難度顯著增加。隨著深度學(xué)習(xí)

![的頭像]() 發(fā)表于

發(fā)表于 07-04 17:25

?746次閱讀

摘要 :本文設(shè)計了一種 基于 FPGA 的實時邊緣檢測系統(tǒng) ,使用OV5640 攝像頭模塊獲取實時的視頻圖像數(shù)據(jù),提取圖像邊緣信息并通過 VGA顯示。FPGA 內(nèi)部使用流水線設(shè)計和 并行運(yùn)算加速

發(fā)表于 05-24 07:45

FPGA的學(xué)習(xí)。

在學(xué)習(xí)中才發(fā)現(xiàn),FPGA遠(yuǎn)不是門電路那么簡單。FPGA中有各種需要的資源,比如門電路、存儲單元、片內(nèi)RAM、嵌入式乘法器、

發(fā)表于 05-22 18:27

大概10年前,大學(xué)同學(xué)建議我學(xué)習(xí)DSP。當(dāng)因為工作忙,也只是簡單學(xué)習(xí)了DSP的一些基礎(chǔ)知識,沒有進(jìn)一步深入學(xué)習(xí)和時間。結(jié)果現(xiàn)在,好像DSP已經(jīng)不再是主流了,現(xiàn)在有了FPGA。 現(xiàn)在想想

發(fā)表于 04-09 10:55

了。FPGA出現(xiàn)后,也想學(xué)習(xí)學(xué)習(xí)這方面的知識。抱著先簡單學(xué)習(xí)下的態(tài)度,在網(wǎng)上找資料看看。感覺FPGA,就像是利用芯片內(nèi)部資源,自由組合門電路

發(fā)表于 04-09 09:46

本帖最后由 1653149838.791300 于 2024-3-31 13:24 編輯

FPGA學(xué)習(xí)首先是要熟悉掌握使用硬件描述語言,這方面可以通過書籍或者這方面論壇,這里個人分享一個比較好

發(fā)表于 03-31 13:23

請問各位大佬,stm32外部中斷的邊沿檢測時,對上升沿或者下降沿是否有要求,必須小于或者大于多少時間,或者在多少時間內(nèi)必須上升或者下降多少V才算觸發(fā)。在spec中只看到了最小是10ns就可以,同時邊沿

發(fā)表于 03-20 08:31

FPGA(Field Programmable Gate Array)學(xué)習(xí)需要具備一系列的課程知識和實踐技能

![的頭像]() 發(fā)表于

發(fā)表于 03-14 15:51

?1128次閱讀

學(xué)習(xí)FPGA必須知道的社區(qū)

![的頭像]() 發(fā)表于

發(fā)表于 01-03 17:51

?357次閱讀

FPGA學(xué)習(xí)-邊沿檢測技術(shù)

FPGA學(xué)習(xí)-邊沿檢測技術(shù)

評論