超異構芯片最近是比較火的一個名詞,其集中特性是將各類不同的芯片內核進行融合,這種集成式芯片設計可以充分整合芯片資源,進一步提升數據計算效率。并且由于芯片在設計之初就打通了相互之間互通兼容性,其內部功能劃分和交互統一構建的邏輯優化,相比單芯片功能方案而言,可以顯著降低彼此功能和交互的各種掣肘;并且很多設計原理圖上可以在芯片之間通過共享某些資源,融合型單芯片可以進一步降低成本。另外,對于自動駕駛系統設計而言,(80%-90%)的輕量級場景+10%左右的挑戰場景+10%左右的極端場景需要提供高性能以行業領先的功率/性能比計算傳統和深度學習算法,這些完全可以通過超異構的不同芯片核進行覆蓋,充分降低復雜度和系統規模。

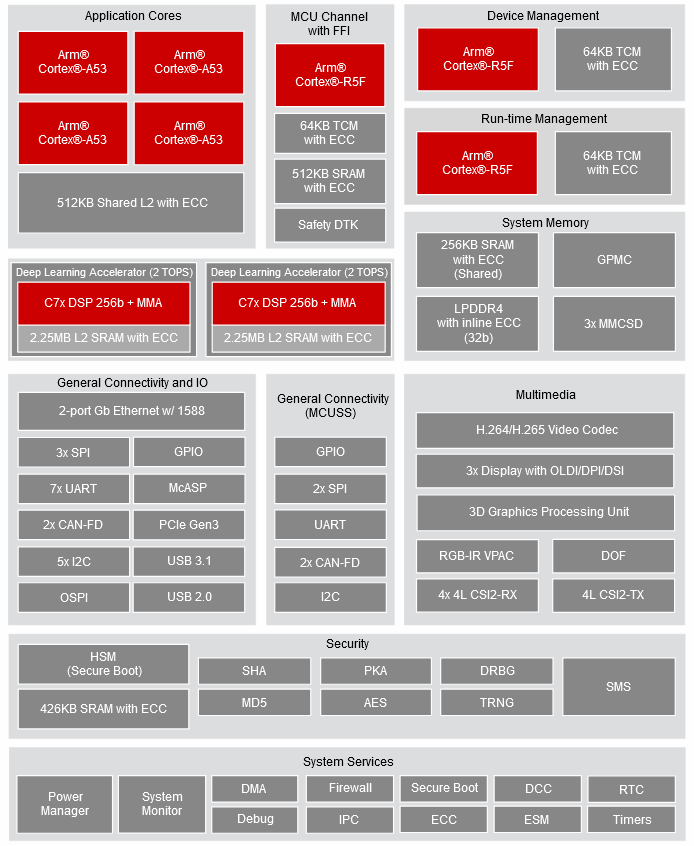

超異構芯片是具有高水平的系統集成,以實現先進汽車的可擴展性和更低成本的支持集中式 ECU。關鍵核心包括具有標量和矢量內核的下一代 DSP,專用深度學習的NN計算核和傳統算法加速器,用于通用計算的最新 ARM 和 GPU 處理器,集成的下一代生成成像子系統 (ISP),視頻編解碼器,以太網集線器和隔離的 MCU 功能安全島,所有受保護汽車級安全和安保硬件加速器等。

一般情況下,除了芯片選型外,設計超異構芯片時需還要滿足如下設計規則:

片上存儲器應設計 ECC 保護并互連

對于引腳錯誤設置故障信號模式

運行時安全診斷、電壓、溫度和時鐘監控,窗口化看門狗定時器,用于存儲器的 CRC 引擎完整性檢查

可用于應用的功能安全需要滿足 ISO26262 要求的ASIL D

啟用需要大量數據的系統帶寬、PCIe 集線器和千兆以太網交換機以及 CSI-2 端口以支持許多傳感器輸入的吞吐量。

1.超異構芯片內核解析

對于超異構芯片而言,一般是基于異構、可擴展的架構開發,多核異構的優點是各核充分發揮其處理效能的優點,再加上專用硬件加速器也可處理特定任務,從而在性能、功耗和成本上達到最佳平衡。

當前被各廠家廣泛使用比較成熟的超異構芯片當屬TI的Jacinto 7 家族的處理器了,當然這也只是初級超異構芯片。不同廠家對其使用方式不完全一致,有將其完全作為SOC芯片使用的,充分使用了其上的AI算力,有些廠家在不太考慮其安全等級要求的情況下也可能將其當做MCU來使用。

本文將以TI的這塊TDA4的芯片為例進行詳細介紹,說明相應的內部架構。

其中主要的幾個異構模塊包括如下:

1)處理器及加速器

①MCU域:

相當于異構芯片域控的MCU芯片單元所起的作用,用于啟動底層硬件驅動、同步時間,啟動操作系統及頂層應用軟件中控制執行類部分邏輯運算。這里MCU域主要是指MCU Island中用于鎖步功能的Arm Cortex-R5F充當;TI這類超異構芯片而言,CPU模塊(Cortex R5F)用于對SOC域核周邊對應的模塊需要單獨進行電壓和時鐘設計,同時,采用專用內存和接口確保其能夠與更大的 SoC 隔離。

②SOC域:

此類模塊通常使用高度定制化的NN加速器來實現。在環境感知模塊中都會涉及大量的典型神經網絡(NN)的運算,過程中深度學習算力主要被消耗掉。包括常見的各類圖像、激光點云檢測算法,比如物體檢測、車道線檢測、紅綠燈識別等。

以TI為例設計的異構芯片中,微處理器系統端包括:Arm Cortex-A72和Arm Cortex-R5F、C71、C66幾大模塊。

其中,在各家域控Tier1開發過程中一般會考慮在A72上運行HLOS(如Linux或QNX),其余核則運行RTOS,整個運行核均可支持AutoSar。使用A72獨立雙核集群配置有助于多操作系統應用對軟件管理程序的最低需求。

R5F子系統支持低級時序關鍵處理任務,用于實時性要求比較高的硬件驅動。使用C71(MMA)進行深度學習神經網絡NN和模型運算,所以說MMA主要計算單位主要是以Tops為計算單位。

DSP處理器(C66)功能包含前端和后端視覺處理兩方面。前端視覺主要是NV12轉BGR、環視拼圖,后端進行浮點運算用以充當AI加速器的CNN后處理。

如上這種結構是一種典型的AI運算模塊(又稱為AI-DSA),適用于對AI運算性能要求高,算法相對穩定的情況。由于AI-DSA模塊在整個智能駕駛場景運算上使用更為普遍,性能更加敏感,對于云端、邊緣計算及自動駕駛幾段場景的工程化落地更加具有可使用性。

③GPU域:

用于圖像處理加速單元,包含大量浮點運算和實現動態 3D 渲染以增強觀看效果應用程序。同時GPU域也可以認為是高效率的AI運算平臺,對于異形場景CornerCase的適配計算效率是最高的。

如上如果兼顧執行效率和執行性能上,可以做自適應的AI算力分配,普通場景的AI運算可以采用常規CPU+DSA方式進行,而特殊邊緣場景可以采用GPU加速核方式進行高效能計算。

④其他處理模塊:

VENC/ VDEC用于視頻編解碼單元,通常高性能的超異構芯片需要適配H.265/HEVC這類高清視頻編碼器。對于下一代自動駕駛系統來說可以提供更高清的視頻編碼能力,實現高清視頻壓縮傳輸。

VPAC(VisionProcessing Accelerator)用于對圖像進行去畸變、下裁剪(Crop)、重整型(Resides)。其目的是確保輸入給神經網絡單元進行處理的圖像已經被初步處理過了,這樣可以提升圖像網絡處理速度和性能。

如下圖是以簡單的圖像傳輸和處理可以講清楚在這一類超異構芯片上如何進行數據鏈路的傳輸和處理。

2)存儲單元

下圖是大多數開發板所有的一個存儲單元框架,接下來以此圖為基礎描述ARM芯片的上電啟動流程。

ROM:芯片內部固化存儲代碼的存儲器,其中固化在芯片iROM中的啟動代碼為BL0。

RAM:在ROM啟動運行的時候,只有RAM是可用的,因此必須要自動從外擴存儲器(nand/sd/usb)中拷貝的uboot.bin二進制文件的頭最大16K(一般是4K或8K)代碼(BL1)。

SDROM:芯片外部的運行內存,由運行在RAM上的BL1進行初始化,用于運行BL2與應用程序。

Nand Flash :芯片外部非易失閃存技術的存儲器,沒有地址總線,不能直接運行代碼,需要將代碼加載到RAM上面才能運行。

就舉例的TDA4芯片而言,BL1 和 BL2 沒有被集成(Jacinto7集成 了 DMSC&MCU R5 取代了 BL1 和BL2 的功能), BL31 執行 ATF,BL32 執行 OP-TEE,BL33 是SPL/U-boot。

相應的存儲單元涉及Main域和MCU域的管理,且兩域分別單獨用于片上共享存儲單元,他們分別通過多核共享存儲控制器MSMC實現相應的存儲管理。TDA4內部還存在LPDDR4 w/ECC模塊,即使未使用 DDR 接口,其VDDS_DDR均需要使用 LPDDR4 電壓范圍進行供電。

2.超異構芯片的啟動說明

對于超異構芯片而言,由于采用了多核異構的架構,因系統需求的差異,其相應的啟動流程也有一定的差異性,并且由于集成多核制會導致其啟動流程比單核和多核同構的處理器會復雜些。

Bootloader 是在操作系統運行之前執行的一段小程序。通過這段小程序,我們可以初始化硬件設備、建立內存空間的映射表,從而建立適當的系統軟硬件環境,為最終調用操作系統內核做好準備。兩種bootloader 可以選擇 SPL (Secondary Program Loader)或 SBL(Secondary bootloader)兩種驅動加載。

SPL表示程序加載,分為兩級加載程序過程。第一級Bootloader是指從ROM 里面的程序中根據啟動方式的選擇引導并加載 SPL。第二級Bootloader是指對硬件的初始化過程,引導下一級的 bootloader 核或加載并運行應用程序。

SBL表示驅動加載。可以實現對外圍設備進行配置,比如 DDR,可以加載并啟動其它核。為了滿足快速啟動 MCU 執行相關的應用,MCU可以先啟動,然后使用BOOT APP 進而引導其它應用程序。在 SBL 啟動流程中,SBL 可以直接加載 Linux內核和 DTB。

如下圖顯示了完整的異構芯片TDA4的程序加載過程。

對于如上超異構芯片而言,用的最廣的要數ARM Cortex-A72核了,因為其在整數、浮點、內存等性能皆有不同程度的提升,雖然還缺少一些細節,不過IPC性能上相對于之前的產品提升了16-30%左右。如下圖表示了芯片A72的具體啟動原理。

整個代碼啟動運行過程包括首先把BL1加載到RAM中運行,然后由BL1對SDRAM進行初始化。最后,代碼重定向完成后在內存中執行的uboot的完整代碼BL2。

從應用層面的系統需求來講,不同的應用可以部署在不同的核,不同核的啟動時序影響著系統需求是否能實現。總體來講,針對系統的應用需求,可能有如下的額外要求:提前Can信息響應、提前啟動畫面、提前啟動攝像頭、提前分配Linux使用空間、提前顯示視頻動畫等。我們應設計合理的 Soc 啟動流程來滿足系統的需求。

3.總結

超異構芯片Super SOC作為ADAS系統普遍應用的處理器,在面向 ADAS 和自動駕駛車輛 (AV) 應用過程中起著舉足輕重的作用。智駕領域中,SOC需要深度學習算法中會比傳統芯片提供提供高性能計算能力,同時可以有效優化其功耗和系統集成度。最終實現支持集中式ECU 或多種傳感器的高級汽車平臺實現可擴展性和更低的成本。

審核編輯:郭婷

-

處理器

+關注

關注

68文章

19169瀏覽量

229153 -

芯片

+關注

關注

454文章

50430瀏覽量

421866 -

PCIe

+關注

關注

15文章

1224瀏覽量

82445

原文標題:聊聊TDA4異構芯片設計、啟動及工作原理

文章出處:【微信號:eng2mot,微信公眾號:汽車ECU開發】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

J721S2/TDA4VE/TDA4VL/TDA4AL EVM用戶指南

Jacinto處理器TDA4AP/TDA4VP/TDA4AH/TDA4VH EVM用戶指南

基于Pytorch訓練并部署ONNX模型在TDA4應用筆記

軟啟動器工作原理介紹

TDA2050音頻功率放大器的工作原理是什么

芯品#TDA4AEN-Q1 具有AI功能的汽車級 ADAS SoC

超異構芯片Super SOC TDA4的設計、啟動及工作原理

超異構芯片Super SOC TDA4的設計、啟動及工作原理

評論