1. 什么叫DDS

直接數字式頻率合成器DDS(Direct Digital Synthesizer),實際上是一種分頻器:通過編程頻率控制字來分頻系統時鐘(SYSTEM CLOCK)以產生所需要的頻率。

DDS 有兩個突出的特點,一方面,DDS工作在數字域,一旦更新頻率控制字,輸出的頻率就相應改變,其跳頻速率高;另一方面,由于頻率控制字的寬度寬(48bit 或者更高),頻率分辨率高。

2. DDS工作原理

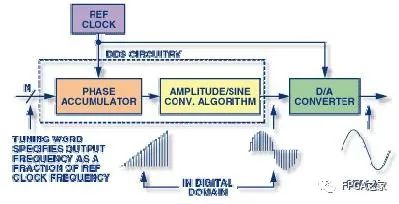

圖1 是DDS 的內部結構圖,它主要分成3 部分:相位累加器,相位幅度轉換,數模轉換器(DAC)。

圖 1,DDS的結構

(1)相位累加器

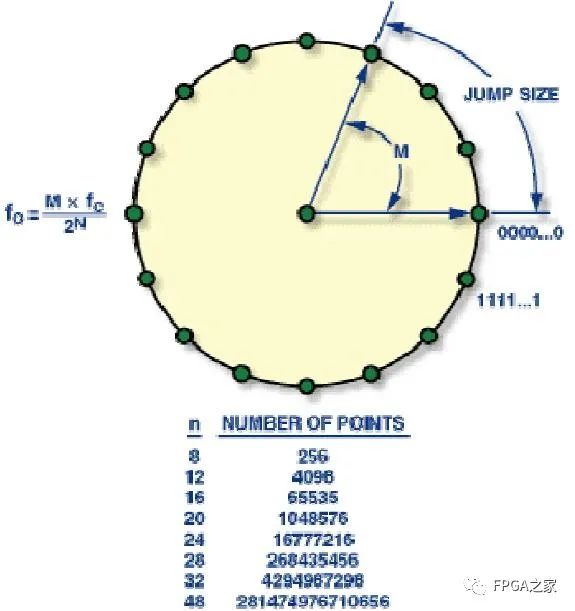

一個正弦波,雖然它的幅度不是線性的,但是它的相位卻是線性增加的。DDS 正是利用了這一特點來產生正弦信號。如圖 2,根據DDS 的頻率控制字的位數N,把360° 平均分成了2的N次等份。

圖2,相位累加器原理

假設系統時鐘為Fc,輸出頻率為Fout。每次轉動一個角度360°/2N, 則可以產生一個頻率為Fc/2N 的正弦波的相位遞增量。那么只要選擇恰當的頻率控制字M,使得 Fout / Fc= M / 2N,就可以得到所需要的輸出頻率Fout,Fout = Fc*M / 2N。

(2)相位幅度轉換

通過相位累加器,我們已經得到了合成Fout 頻率所對應的相位信息,然后相位幅度轉換器把0°~360°的相位轉換成相應相位的幅度值。比如當DDS 選擇為2V p-p 的輸出時,45°對應的幅度值為0.707V,這個數值以二進制的形式被送入DAC。這個相位到幅度的轉換是通過查表完成的。

(3)DAC

輸出代表幅度的二進制數字信號被送入DAC 中,并轉換成為模擬信號輸出。注意DAC 的位數并不影響輸出頻率的分辨率。輸出頻率的分辨率是由頻率控制字的位數決定的。直接數字式頻率合成技術(DDS)是一種先進的全數字頻率合成技術,它具有多種數字式調制能力(如相位調制、頻率調制、幅度調制以及I/Q正交調制等),在通信、導航、雷達、電子戰等領域獲得了廣泛的應用。在項目中光柵傳感系統高頻并行解調算法的FPGA實現我們的光纖通信模塊用到DDS。我們通過FPGA實現了DDS的功能。

1971年,美國學者J.Tierney等人撰寫的《A Digital Frequency Synthesizer》一文首次提出了以全數字技術,從相位概念出發直接合成所需波形的一種新的頻率合成原理。限于當時的技術和器件水平,它的性能指標尚不能與已有的技術相比,故未受到重視。近10年間,隨著微電子技術的迅速發展,直接數字頻率合成器

(Direct Digital Frequency Synthesis簡稱DDS或DDFS)得到了飛速的發展,它以有別于其它頻率合成方法的優越性能和特點成為現代頻率合成技術中的佼佼者。具體體現在相對帶寬寬、頻率轉換時間短、頻率分辨率高、輸出相位連續、可產生寬帶正交信號及其他多種調制信號、可編程和全數字化、控制靈活方便等方面,并具有極高的性價比。

DDS基本原理及性能特點

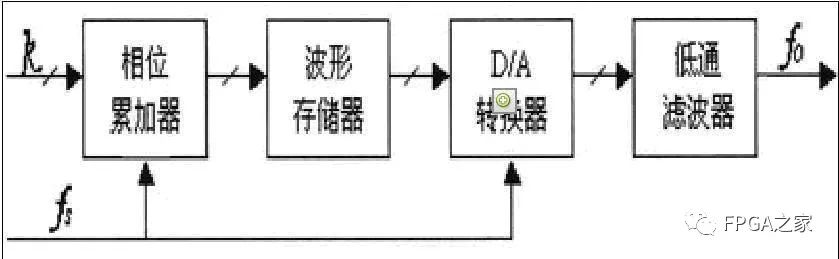

DDS的基本原理是利用采樣定理,通過查表法產生波形。DDS的結構有很多種,其基本的電路原理如圖所示。

相位累加器由N位加法器與N位累加寄存器級聯構成。每來一個時鐘脈沖fs,加法器將頻率控制字k與累加寄存器輸出的累加相位數據相加,把相加后的結果送至累加寄存器的數據輸入端。累加寄存器將加法器在上一個時鐘脈沖作用后所產生的新相位數據反饋到加法器的輸入端,以使加法器在下一個時鐘脈沖的作用下繼續與頻率控制字k相加。這樣,相位累加器在時鐘作用下,不斷對頻率控制字進行線性相位累加。由此可以看出,相位累加器在每一個時鐘脈沖輸入時,把頻率控制字累加一次,相位累加器輸出的數據就是合成信號的相位,相位累加器的溢出頻率就是DDS輸出的信號頻率。

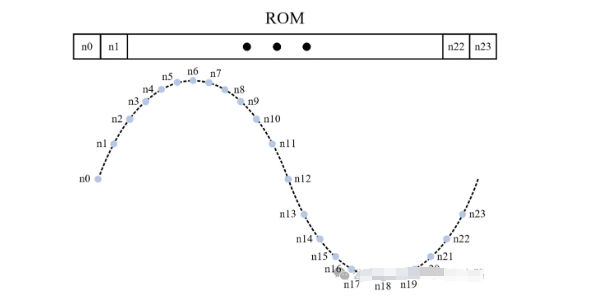

用相位累加器輸出的數據作為波形存儲器(ROM)的相位取樣地址,這樣就可把存儲在波形存儲器內的波形抽樣值(二進制編碼)經查找表查出,完成相位到幅值轉換。波形存儲器的輸出送到D/A轉換器,D/A轉換器將數字量形式的波形幅值轉換成所要求合成頻率的模擬量形式信號。低通濾波器用于濾除不需要的取樣分量,以便輸出頻譜純凈的正弦波信號。

DDS在相對帶寬、頻率轉換時間、高分辨力、相位連續性、正交輸出以及集成化等一系列性能指標方面遠遠超過了傳統頻率合成技術所能達到的水平,為系統提供了優于模擬信號源的性能。

如何用FPGA實現

相位累加寄存器是DDS的核心,在我的設計中相位寄存器的字長為23位,之所以選擇23位是因為項目要求頻率步進可以達到1Hz,我們BASYS板上有25MHz的晶振,我們將其三分頻為8.333MHz,我們相位寄存器字長23位則頻率步進最小值為F/2N =8.333*106 /223≈1Hz( 當然根據項目實際需要我們今后會通過外接晶振及DCM配合使其=1 Hz。相位步進量字長為18位,最高輸出頻率為fmax =8.333*106 /223 *218 =260416 Hz。

波形存儲器用SPATAN3E內部RAM實現,通過core generator 生成ROM,我們的設計中用ROM存取256個點,這樣到頻率達到200kHz時每個周期輸出可達到21個采樣點,若是存512個點那么就能達到42個點,具體存多少個點根據后續要求,及芯片本身的內部資源決定。用PC機的VC編寫“正弦信號查找表”,將其寫入ROM的初始化文件。當然可以把其他任意周期性波形數據寫入ROM,道理想同。

生成“正弦信號查找表”有以下步驟:首先,確定每周期采樣點數,這里256個點,計算各采樣點的數值。歸一化,由于我們后續須將數字量通過DAC輸出,所以計算所得數值的值域轉化為[0,1],以方便轉化為DAC對應的數值,由于8位的DAC的輸出值最高為255,所以須將得到的數值乘以255。

這里設計的相位累加寄存器,可根據實際需要產生無限周期個波形或1024以內個周期波形(periodn為10位)增加了設計的功能。

程序說明

dds_rom是儲存波形的儲存器;

phaseregister是相位累加寄存器;

fredevider3是三分頻電路;

sch_top是dds芯片頂層文件;

工程dds_version1是該設計的工程文件;

文件夾sin_test是生成正弦信號查找表的源文件。

測試

在這個DDS 的設計過程中我們在BASYS板上跑了程序,程序與這個在I/O 端口方面有少許差別,需將源程序I/O口作了一下修改Clk為BASYS板上的50MHz,Dout為LD0到LD7,在實際應用中將其引致I/O口外接D/A即可產生變化的電壓值(波形),這里通過LED是為了看結果直觀。Reset為sw7,reset為’1’時DDS停止工作,并把相應寄存器置零,具體見代碼。Sw6,sw5用于輸出波形周期選擇,為’00’時一直輸出波形,為’01’,’10’,’11’時分別輸出1,2,3個周期波形。Sw4到sw0為相位步進量(頻率控制字),對應于1hz到31hz。

審核編輯:郭婷

-

頻率合成器

+關注

關注

5文章

219瀏覽量

32334 -

dac

+關注

關注

43文章

2272瀏覽量

190845 -

DDS

+關注

關注

21文章

631瀏覽量

152544

原文標題:DDS(Direct Digital Synthesizer)直接數字式頻率合成器

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

14位,3.3V CMOS直接數字合成器-CBM99D10

DDS直接數字式頻率合成器基本原理及性能特點

DDS直接數字式頻率合成器基本原理及性能特點

評論