歡迎加入至芯科技FPGA微信學(xué)習(xí)交流群,這里有一群優(yōu)秀的FPGA工程師、學(xué)生、老師、這里FPGA技術(shù)交流學(xué)習(xí)氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標題:FPGA vs ASIC

文章出處:【微信公眾號:FPGA設(shè)計論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

FPGA

+關(guān)注

關(guān)注

1626文章

21665瀏覽量

601805

原文標題:FPGA vs ASIC

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設(shè)計論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

ASIC集成電路與FPGA的區(qū)別

ASIC(專用集成電路)與FPGA(現(xiàn)場可編程門陣列)是兩種不同的集成電路技術(shù),它們在多個方面存在顯著的區(qū)別。以下是兩者的主要差異: 一、設(shè)計與制造 ASIC 是為特定應(yīng)用定制設(shè)計的集成電路。 需要

FPGA和ASIC在大模型推理加速中的應(yīng)用

隨著現(xiàn)在AI的快速發(fā)展,使用FPGA和ASIC進行推理加速的研究也越來越多,從目前的市場來說,有些公司已經(jīng)有了專門做推理的ASIC,像Groq的LPU,專門針對大語言模型的推理做了優(yōu)化,因此相比GPU這種通過計算平臺,功耗更低、

FPGA與ASIC的優(yōu)缺點比較

FPGA(現(xiàn)場可編程門陣列)與ASIC(專用集成電路)是兩種不同的硬件實現(xiàn)方式,各自具有獨特的優(yōu)缺點。以下是對兩者優(yōu)缺點的比較: FPGA的優(yōu)點 可編程性強 :FPGA具有高度的可編程

FPGA仿真工具包軟件EasyGo Vs Addon介紹

EasyGo Vs Addon是一款領(lǐng)先的FPGA仿真工具包軟件,它強大地連接了VeriStand軟件與Matlab/Simulink,為實時測試和驗證領(lǐng)域帶來了前所未有的便利和效率,特別適用于汽車、航空航天和能源電力等實時測試和驗證至關(guān)重要的行業(yè)。

FPGA仿真黑科技\"EasyGo Vs Addon \",助力大規(guī)模電力電子系統(tǒng)仿真

一、EasyGo Vs AddonEasyGo Vs Addon是一款領(lǐng)先的FPGA仿真工具包軟件,它強大地連接了VeriStand軟件與Matlab/Simulink,為實時測試和驗證領(lǐng)域帶來

發(fā)表于 10-23 18:18

為低功耗FPGA、處理器和ASIC實施啟用LVDS鏈路

電子發(fā)燒友網(wǎng)站提供《為低功耗FPGA、處理器和ASIC實施啟用LVDS鏈路.pdf》資料免費下載

發(fā)表于 08-29 09:59

?0次下載

將ASIC IP核移植到FPGA上——更新概念并推動改變以完成充滿挑戰(zhàn)的任務(wù)!

本系列文章從數(shù)字芯片設(shè)計項目技術(shù)總監(jiān)的角度出發(fā),介紹了如何將芯片的產(chǎn)品定義與設(shè)計和驗證規(guī)劃進行結(jié)合,詳細講述了在FPGA上使用IP核來開發(fā)ASIC原型項目時,必須認真考慮的一些問題。文章從介紹

FPGA技術(shù)的五大優(yōu)勢

各行各業(yè)紛紛采用FPGA芯片是源于FPGA融合了ASIC和基于處理器的系統(tǒng)的最大優(yōu)勢。 FPGA能夠提供硬件定時的速度和穩(wěn)定性,且無需類似自定制AS

發(fā)表于 04-23 15:50

?1062次閱讀

到底什么是ASIC和FPGA?

上一篇文章,小棗君給大家介紹了CPU和GPU。今天,我繼續(xù)介紹計算芯片領(lǐng)域的另外兩位主角——ASIC和FPGA。█ASIC(專用集成電路)上篇提到,GPU的并行算力能力很強,但是它也有缺點,就是功耗

fpga與asic在概念上有什么區(qū)別

FPGA(現(xiàn)場可編程門陣列)和ASIC(應(yīng)用特定集成電路)在概念上存在明顯的區(qū)別。

fpga和asic的區(qū)別

FPGA(現(xiàn)場可編程門陣列)和ASIC(專用集成電路)是兩種不同類型的集成電路,它們在設(shè)計靈活性、制造成本、應(yīng)用領(lǐng)域等方面有著顯著的區(qū)別。

FPGA與AISC的差異

FPGA(Field-Programmable Gate Array,現(xiàn)場可編程門陣列)和ASIC(Application-Specific Integrated Circuit,專用集成電路

發(fā)表于 02-22 09:54

到底什么是ASIC和FPGA?

Programmable Gate Array,現(xiàn)場可編程門陣列。

FPGA這些年在行業(yè)里很火,勢頭比ASIC還猛,甚至被人稱為“萬能芯片”。

其實,簡單來說,FPGA就是可以重構(gòu)的芯片。它可以根據(jù)

發(fā)表于 01-23 19:08

FPGA、ASIC、GPU誰是最合適的AI芯片?

CPU、GPU遵循的是馮·諾依曼體系結(jié)構(gòu),指令要經(jīng)過存儲、譯碼、執(zhí)行等步驟,共享內(nèi)存在使用時,要經(jīng)歷仲裁和緩存。 而FPGA和ASIC并不是馮·諾依曼架構(gòu)(是哈佛架構(gòu))。以FPGA為例,它本質(zhì)上是無指令、無需共享內(nèi)存的體系結(jié)

發(fā)表于 01-06 11:20

?1404次閱讀

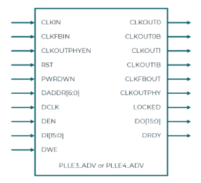

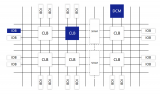

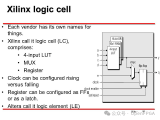

FPGA vs ASIC

FPGA vs ASIC

評論