工程界常常使用保護地線進行隔離,來抑制信號間的相互干擾。的確,保護地線有時能夠提高信號間的隔離度,但是保護地線并不是總是有效的,有時甚至反而會使干擾更加惡化。使用保護地線必須根據實際情況仔細分析,并認真處理。

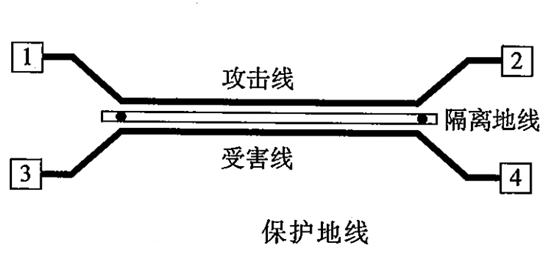

保護地線是指在兩個信號線之間插入一根網絡為GND的走線,用于將兩個信號隔離開,地線兩端打GND過孔和GND平面相連,如圖所示。有時敏感信號的兩側都放置保護地線。

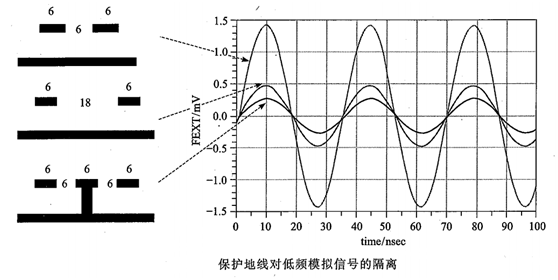

要想加入保護地線,首先必須把兩個信號線的間距拉開到足以容納一根保護地線的空間,由于拉開了信號線的間距,即使不插入保護地線,也會減小串擾。插入保護地線會有多大的作用? 低頻模擬信號包地我們來看表層微帶線情況下串擾的大小。假設走線是50Ω阻抗控制的,線寬為6mil,介質厚度為3.6mil,介電常數為4.5。并假設兩路信號都是載波頻率為30Mhz,帶寬為2Mhz的模擬信號。

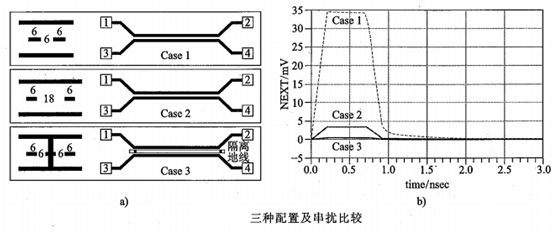

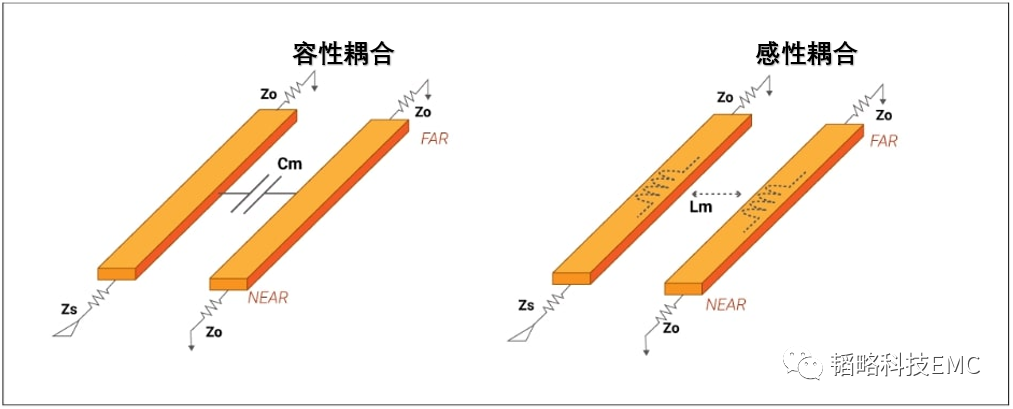

下圖顯示了三種情況下的遠端串擾情況。當線間距為6mil時,由于兩條線緊密耦合,遠端串擾較大。把間距增加到18mil,遠端串擾明顯減小。進一步,在兩條線之間加入保護地線,地線兩端使用過孔連接到地面,遠端串擾進一步減小。

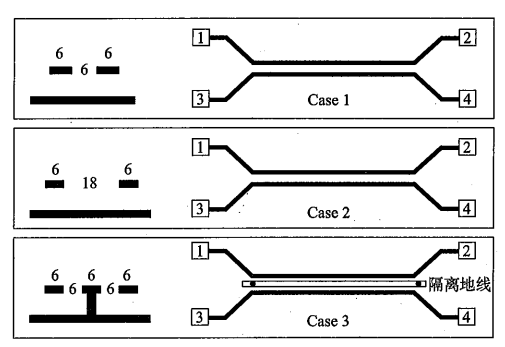

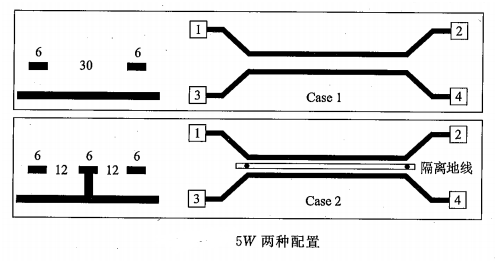

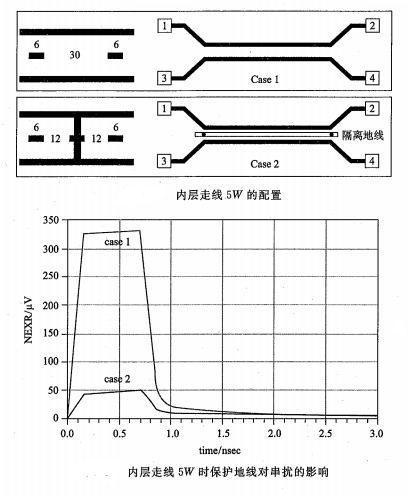

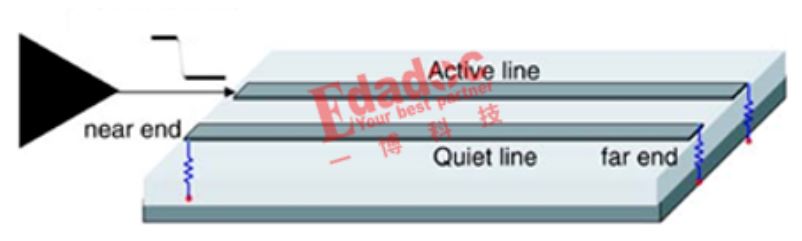

對于低頻模擬信號之間的隔離,保護地線的確很有用。這也是很多低頻板上經常見到的“包地”的原因。但是如果需要隔離的數字信號,情況會有所不同。我們分表層微帶線和內層帶狀線兩種情況來討論保護地線對數字信號的隔離效果。以下討論我沒假定PCB走線都是50Ω阻抗控制的。 表層走線仍然使用上面的表層走線疊層結構,線寬為6mil,介質厚度為3.6mil,介電常數為4.5。攻擊信號為上升時間Tr=200ps的階躍波形。考慮以下三種情況下的近端串擾和遠端串擾的情況,如下圖所示,其中耦合段長度為2000mil。

Case1:兩條走線間距gap=1w(w=6mil表示線寬) Case2:兩條走線間距gap=3w,僅僅拉大道能夠放下一條保護線的間距,但不適用保護線。 Case3:兩條線間距gap=3w,中間使用保護地線,并在兩端打GND過孔。

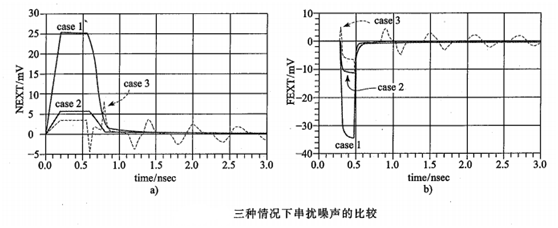

下圖顯示了三種情況下串擾波形,無論是近端串擾還是遠端串擾,走線間距從1w增加到3w時,串擾都明顯減小。在此基礎上,走線間插入保護地線,串擾如下圖中Case 3所示,相比Case 2,插入保護地線,不但沒有起到進一步減小串擾的作用,反而增大了串擾噪聲。

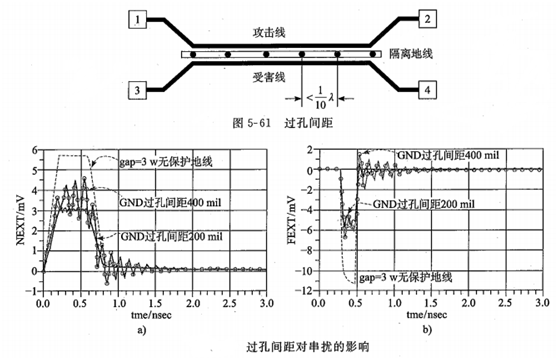

這個例子表明拉開走線間距是最有效的的減小串擾的方法。保護地線如果使用不當,可能反而會惡化串擾,因此,在使用保護地線時需要根據實際情況仔細分析。保護地線要想起到應有的隔離作用,需要再地線上添加很多GND過孔,過孔間距應小于1/10λ,如圖所示。λ為信號中最高頻率成分對應的波長。

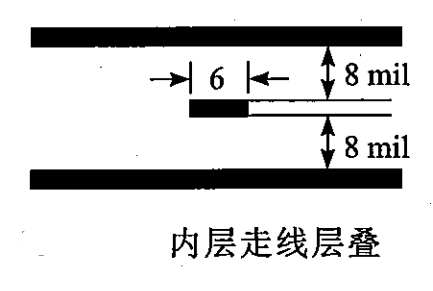

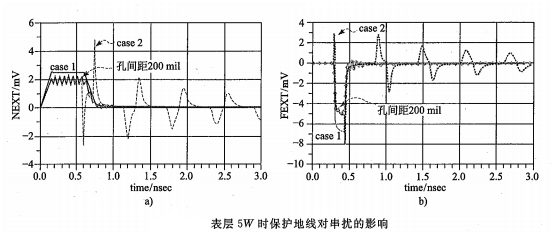

內層走線對于內層走線,如下圖

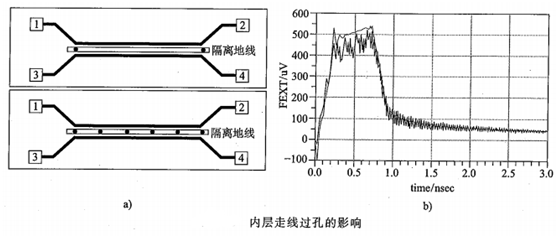

介電常數為4.5,阻抗為50Ω。考慮到下圖三種情況。攻擊信號為上升時間Tr=200ps的階躍波形,入射信號幅度500mv,耦合長度為2000mil,近端串擾如圖所示,加入了保護地線,近端串擾從3.44mV進一步減小到了0.5mV。信號隔離度提高了16B。對于內層走線,加入保護地線能夠獲得更大的隔離度。

對于表層走線來說,使用密集型的GND過孔,對提升隔離效果是有好處的。但是對于內層走線來說,使用密集型的GND過孔幾乎得不到額外的好處,下圖對比了GND過孔間距為2000mil(保護地線兩端打GND過孔)和GND過孔間距為400mil時的近端串擾情況,串擾量幾乎沒有變化。

間距增加到5w時情況如何

當走線間距進一步加大,保護地線仍保持在6mil的線寬時,對于表層走線來說,保護地線的作用減小。下圖中,兩條線間距拉到5w時,兩種情況下近端串擾和遠端串擾量和不使用保護地線情況相當,沒有明顯改善。因此對于表層走線來說,走線間距很大時,中間再加入保護地線,幾乎沒有什么效果,如果處理不好反而會使串擾惡化。

對于內層走線來說,保護地線仍然會起很大作用。如下圖,內層間距為5W,兩種情況下近端串擾噪聲波形如圖。中間加入了保護地線,能明顯改善近端串擾。

結論:保護地線對低頻模擬信號的隔離通常都是有效的。但是在數字信號之間的保護走線并不是那么有用,有時反而會使情況更惡化。 對于表層走線,如果保護地線的GDN孔間距很大,可能會使串擾更加嚴重,必須使用非常密集的GND孔才能起到隔離的效果。 對于內層走線,保護地線可以減小近端串擾。

審核編輯:郭婷

-

pcb

+關注

關注

4317文章

23009瀏覽量

396320 -

信號線

+關注

關注

2文章

168瀏覽量

21422

原文標題:包地與串擾

文章出處:【微信號:EMC_EMI,微信公眾號:電磁兼容EMC】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

高頻電路設計中的串擾問題

PCB產生串擾的原因及解決方法

如何使用SigXplorer進行串擾的仿真

怎么樣抑制PCB設計中的串擾

保護地線減小近端串擾

保護地線減小近端串擾

評論