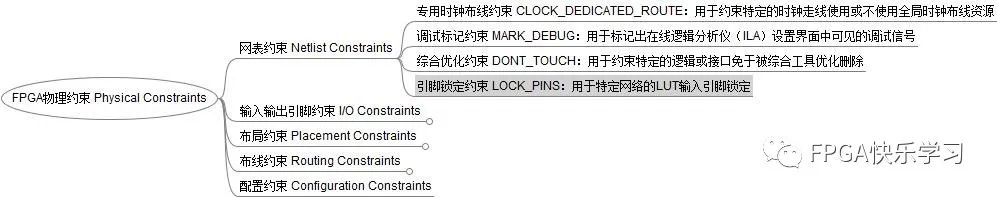

概述

話說網表約束中的CLOCK_DEDICATED_ROUTE、MARK_DEBUG和DONT_TOUCH,在實際工程中常常都可能遇上。MARK_DEBUG和DONT_TOUCH在設計和調試中可能常常要用到,CLOCK_DEDICATED_ROUTE偶爾能夠應應急。而這里要介紹的LOCK_PINS,筆者至今沒有碰過,估計大家在實踐中恐怕也很難有機會或必要用上它。但誰知道呢?存在即是合理,相信Xilinx把這樣一個非常底層的約束搬上臺面,也一定有它的用場,本著萬一哪天能夠應應急的想法,我們也來了解一下這個LOCK_PINS的使用吧。

原理探究

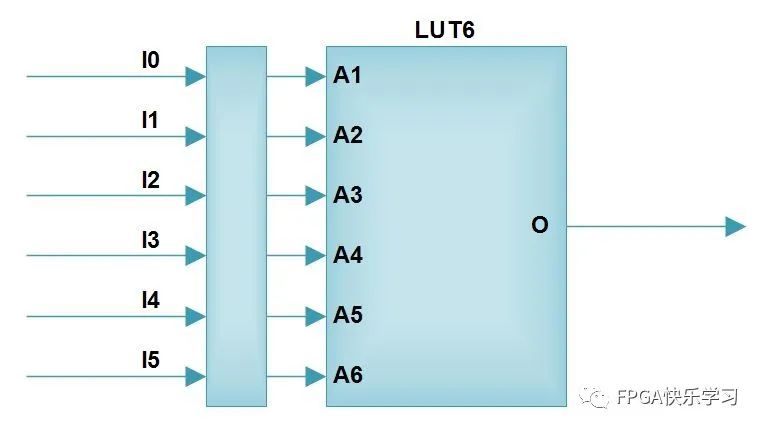

網表約束LOCK_PINS約束的對象是Xilinx FPGA器件中LUT物理輸入端口和邏輯輸入端口的映射關系。關于LUT結構,大家可以參考Xilinx的ug474文檔,該文檔詳細介紹了Artix-7系列FPGA器件的邏輯資源。當然,文檔中對于LUT的結構描述中,只提及輸入端口,并沒有所謂物理輸入端口和邏輯輸入端口的概念。筆者認為,ug474所涉及的LUT結構的輸入端口,其實是包括邏輯輸入端口和物理輸入端口的,它們之間的連接也是可以布線算法的需要進行靈活調整的。

如圖所示,LUT6中的物理輸入端口有A1~A6,邏輯輸入端口有I0~I5。在邏輯輸入端口和物理輸入端口之間,存在著一塊布線池(官方沒有這方面的介紹,筆者根據自己的理解進行描述,僅供參考)。

也就是說,物理輸入端口和邏輯輸入端口并不是固定I0-A1、I1-A2……這樣規規矩矩的成對連接的,它們的一一對應關系是可以根據布線需要進行調整的。之所以提供這樣的配對靈活性,我相信很大程度上是基于最優化外部輸入接口(即連接到I0~I5的走線)的布線而設計的。而一旦進行工程的布局布線后,LUT的邏輯輸入端口和物理輸入端口之間的一一對應關系便會被固定下來。當然了,此時,作為設計者的你,基于某些特定的優化目的,可以通過網表約束LOCK_PINS來鎖定某對或某幾對邏輯和物理輸入端口的映射關系。可以說,LOCK_PINS約束相當底層,對于所謂的特定的優化目的,筆者只在ug903文檔中找到“物理輸入端口A5和A6是最快的LUT輸入端口,所以可以使用LOCK_PINS將時序關鍵路徑約束到該端口上”這樣的描述。而筆者在ug474中并沒有找到Artix-7的LUT有類似的描述。當然,或許ug903的這個描述是針對其它某個FPGA系列器件的LUT。不管怎樣,大家先有個概念,知道有這么回事,將來真遇到類似這么細節的問題時,可以快速在這個方向上做進一步的探索,免去“眾里尋他千百度”的力氣。

工程實踐

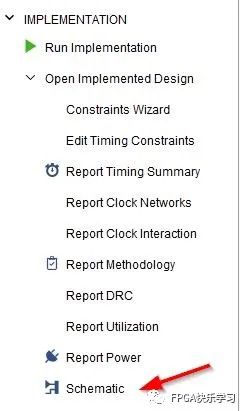

好了,原理說明白了,接著就動手實踐一把。以《Verilog邊碼邊學》教程的sim_201工程為例,打開工程后,保證工程已經做過編譯,然后點擊IMPLEMENTATION->Open Implemented Design->Schematic,打開原理視圖。

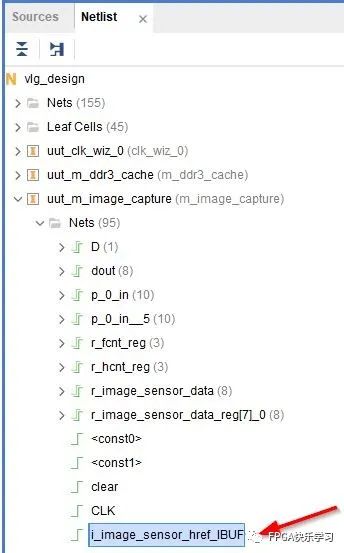

此時,可以在Netlist界面下展開具體的網表,找一個信號進行實踐。當然了,實際應用中,需要哪個信號,可能是根據具體的需要而定的,這里我們只是為了實踐一下如何使用LOCK_PINS約束,所以就隨便找到如圖所示的uut_m_image_capture->Nets下的i_image_sensor_href_IBUF這個信號。

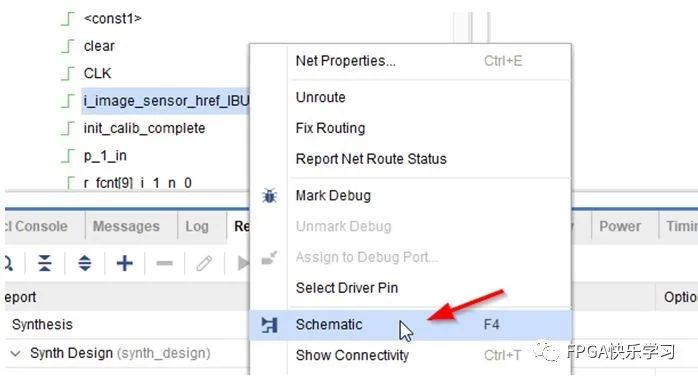

在i_image_sensor_href_IBUF信號上右鍵單擊,在彈出菜單中再單擊Schematic選項。

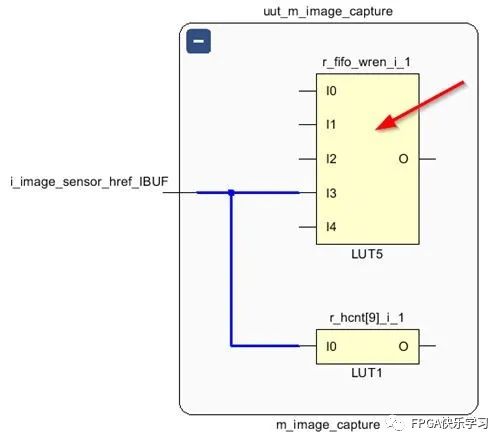

此時可以看到,Schematic(2)定位到了i_image_sensor_href_IBUF信號在原理圖中的位置。由于該信號連接的r_fifo_wren_i_1這個LUT有5個輸入端口,因此我們可以繼續雙擊r_fifo_wren_i_1這個LUT查看它所有的輸入端口。

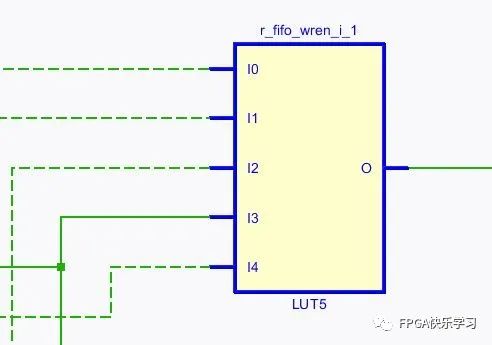

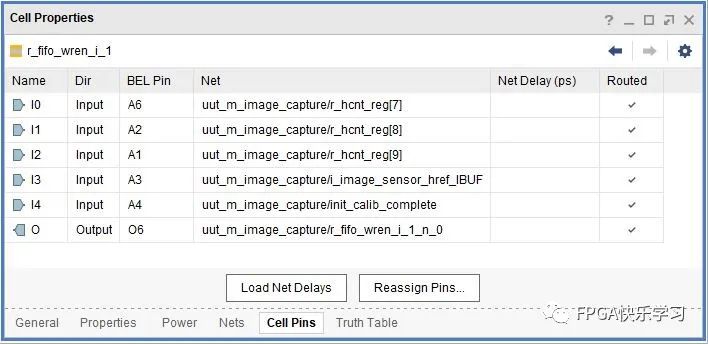

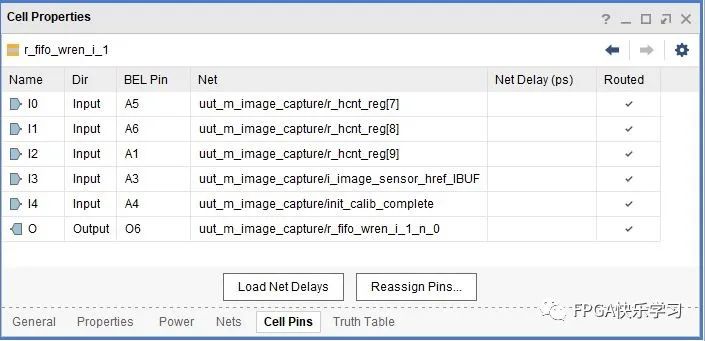

r_fifo_wren_i_1的所有5個輸入端口如圖所示。

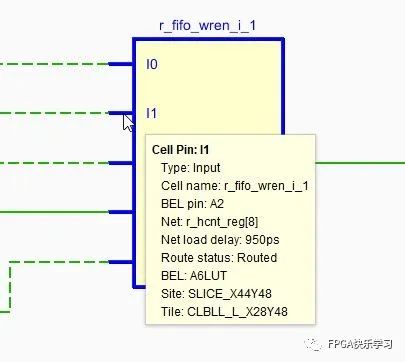

當我們把鼠標停留在LUT的某個邏輯輸入端口上,就可以看到該邏輯輸入端口的相關信息。如圖所示,I1的信息中顯示,它所對應的BEL pin,即物理輸入端口是A2。這是默認FPGA布局布線的結果。

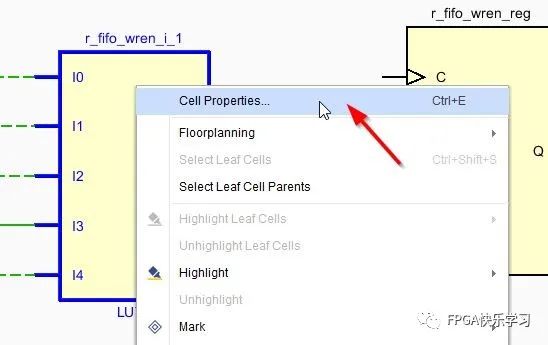

此時可以在r_fifo_wren_i_5這個LUT上右鍵單擊,彈出菜單中再點擊Cell Properties…打開它的屬性信息進行查看。

在屬性的Cell Pins頁面中,可以看到Name(即LUT邏輯輸入端口)、BELPin(即LUT物理輸入端口)以及Net(實際設計中布線信號的網絡名稱)之間的映射關系。

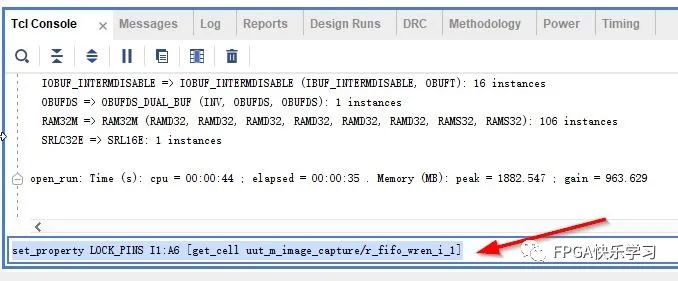

此時,我們可以在Tcl Console中輸入以下腳本并回車運行,使用LOCK_PINS約束將I1和A6映射在一起,也就是I1不再和A2連接,A6也不再和I0連接。

set_property LOCK_PINS I1:A6 [get_celluut_m_image_capture/r_fifo_wren_i_1]

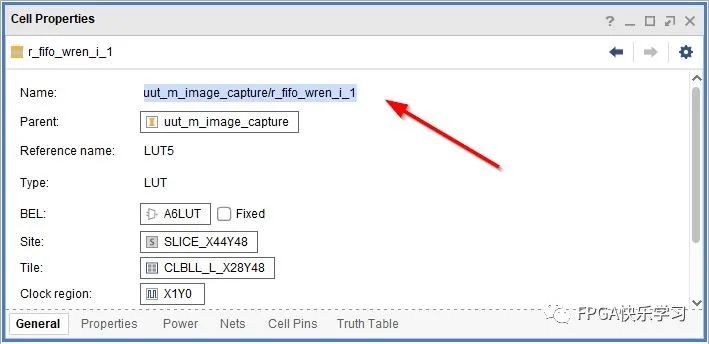

好奇的你或許想知道腳本中get_cell后接的一串路徑名稱從何而得?如圖所示,在屬性的General頁面中Name一欄,就是目標LUT的名稱uut_m_image_capture/r_fifo_wren_i_1。

在約束后,I1一定與A6連接在一起了,至于I0和A2是否會連接在一起,或者會不會因為我們的約束而打亂了其它邏輯輸入端口和物理輸入端口之間的映射關系,就由Vivado的算法自己決定了。

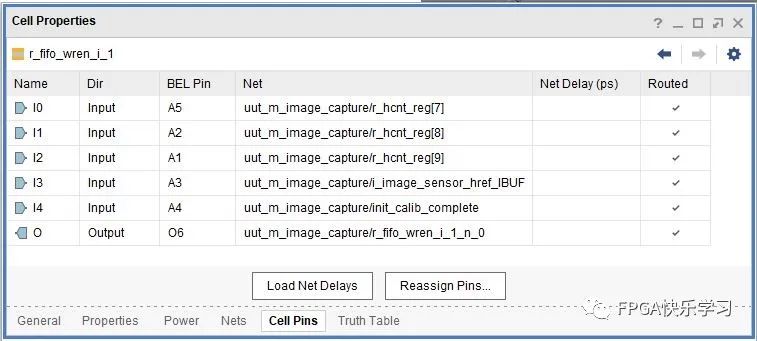

如圖所示,對于當前的實例,最終I1與A6連接在一起,而I0則連接到了A5,而不是A2。大家不用覺得奇怪,因為我們只約束了I1和A6,其它邏輯和物理端口之間任何的連接映射關系都是有可能出現的。

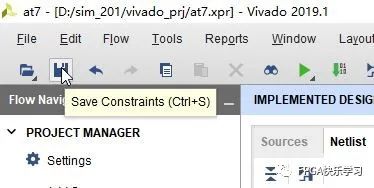

與時序約束一樣,網表約束LOCK_PINS雖然是物理約束,但本質上也是約束設計,在Tcl Console中運行后,需要點擊Save Constrains保存到.xdc約束腳本中才會最終生效。

如果我們要約束多對LUT邏輯和物理端口的映射關系,則可以運行類似如下的腳本。

set example_lut[get_cells uut_m_image_capture/r_fifo_wren_i_1]

set_property LOCK_PINS {I0:A5 I1:A2} $example_lut

get_property LOCK_PINS $example_lut

如圖所示,以上腳本將I0和A5、I1和A2分別映射連接在一起了。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601864 -

端口

+關注

關注

4文章

955瀏覽量

32014 -

約束

+關注

關注

0文章

82瀏覽量

12718 -

網表

+關注

關注

0文章

14瀏覽量

7627

原文標題:物理約束實踐:網表約束LOCK_PINS

文章出處:【微信號:FPGA快樂學習,微信公眾號:FPGA快樂學習】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

時序約束之時序例外約束

物理約束之布局約束

Adam Taylor玩轉MicroZed系列74:物理約束

FPGA時序約束案例:偽路徑約束介紹

FPGA案例之衍生時鐘約束

物理約束實踐:網表約束LOCK_PINS

物理約束實踐:網表約束LOCK_PINS

評論