1、實驗目的

在剛接觸modelsim時,被其繁復的操作流程所困,一度只能依靠在quartus中修改代碼編譯后再重啟modelsim,自動導入才能得到波形。這樣的操作最大的問題就是修改代碼的成本巨大。每次更新波形的時間在5分鐘左右。為此,通過不斷地學習,終于將波形仿真的各個事項了解清楚。這里做一下記錄,方便以后回顧。

2、實驗操作

①純modelsim的verilog仿真

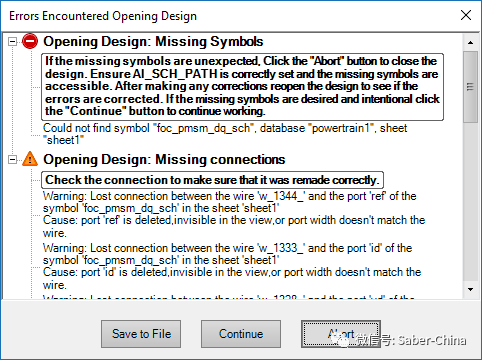

一般來說,前仿真是不需要器件的。如果使用了IP核就另論。這里先通過純modelsim仿真了解modelsim的工作目錄的結構,為后面的聯合仿真的刷新提供基礎。

這里直接使用圖片集描述:

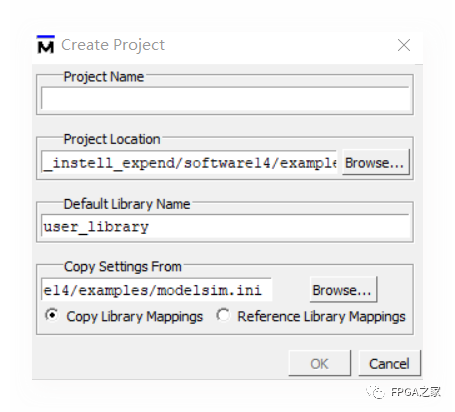

這個操作感覺意義不大,在新建工程中也也可以創建library。

這個可以添加project和library,構建設計平臺。

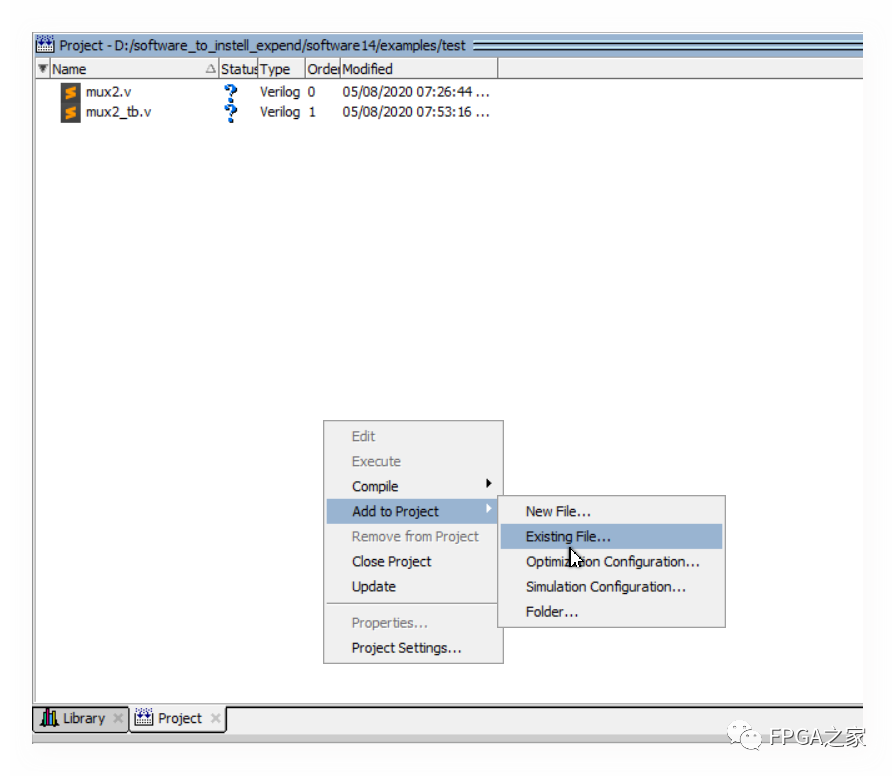

然后進入project窗口,這個窗口就是用于編輯工程的,具體操作在前面的一篇關于modelsim的操作中有,這里不具體說明。

添加本地文件和編譯都在右擊中。接下來轉到library界面,就在上圖的左下角的library中。

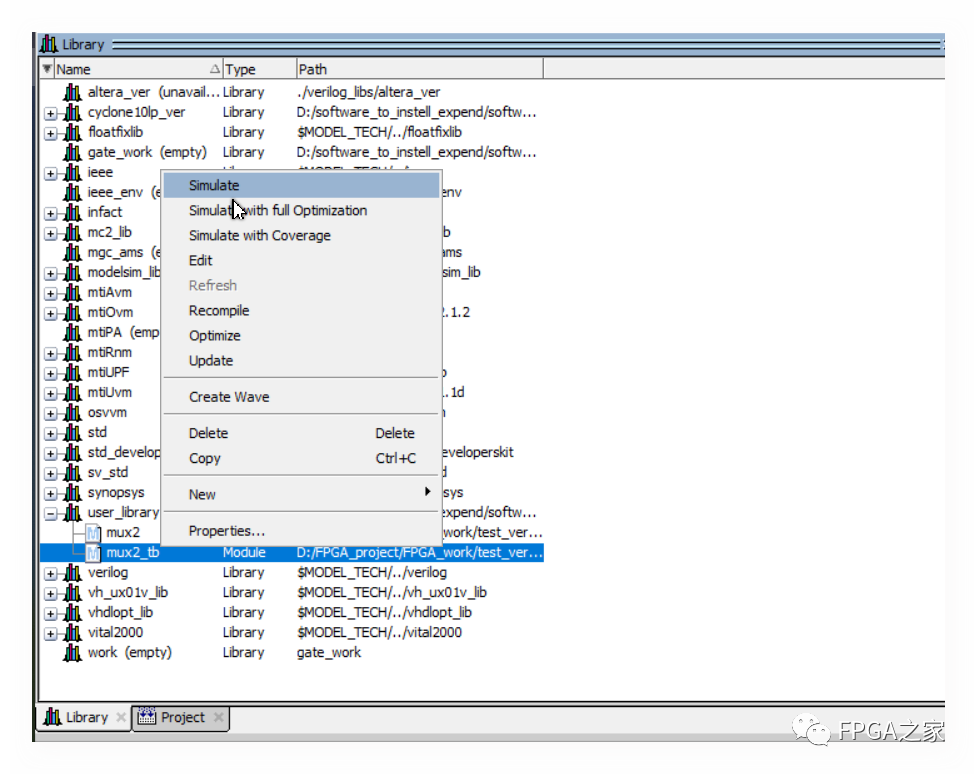

進入仿真階段。這是后會自動出現sim界面。(還是在左下角可以看到)

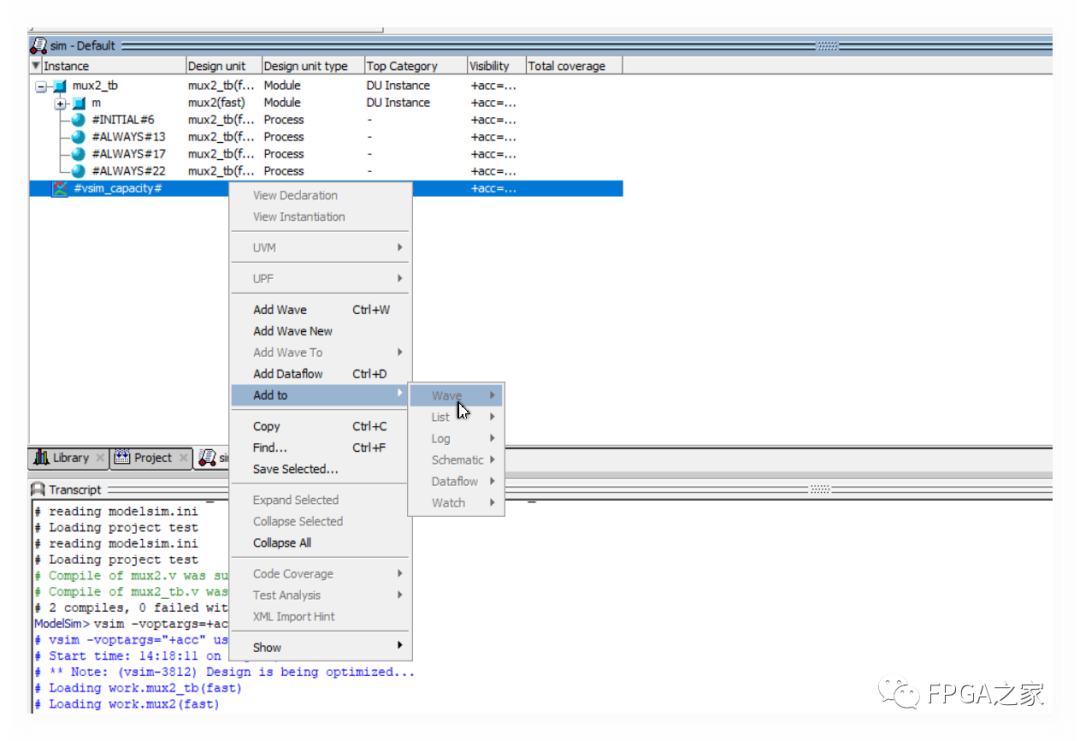

這里是沒有波形的,需要手動添加觀測信號。

這里的wave是暗的,為什么?可以看到sim的亮線指在sim_capacity上,而非mux2_tb上,導致沒有可以選擇的觀察信號。同理,如果指向其他的地方,被選擇的觀察信號可能是別的模塊,比如被測模塊。如果兩個模塊有同名變量且沒有連接,那就可能出現多個同名不同值的波形。(這里值得注意,但凡是右擊,都要確定光標所在,否則容易出錯)

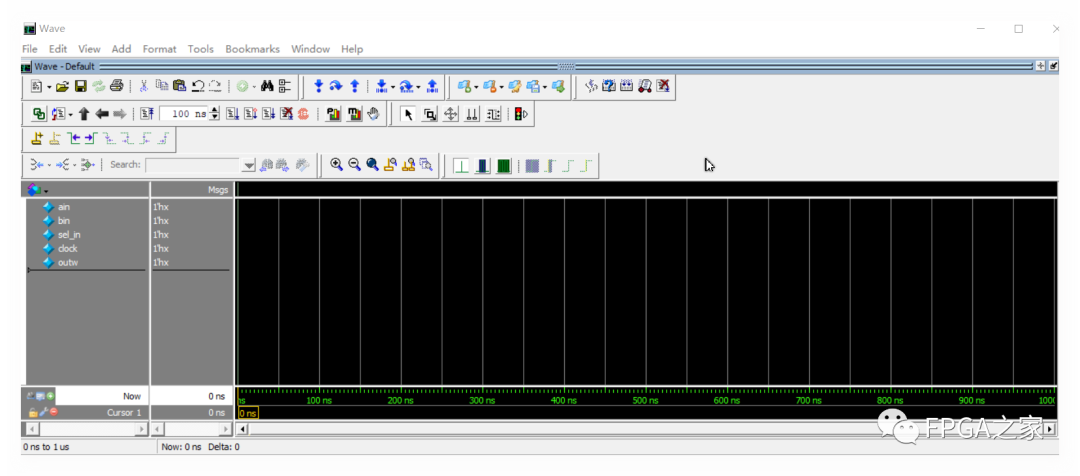

正確地添加信號后會出現wave(有些是浮動的,有些是嵌入的)

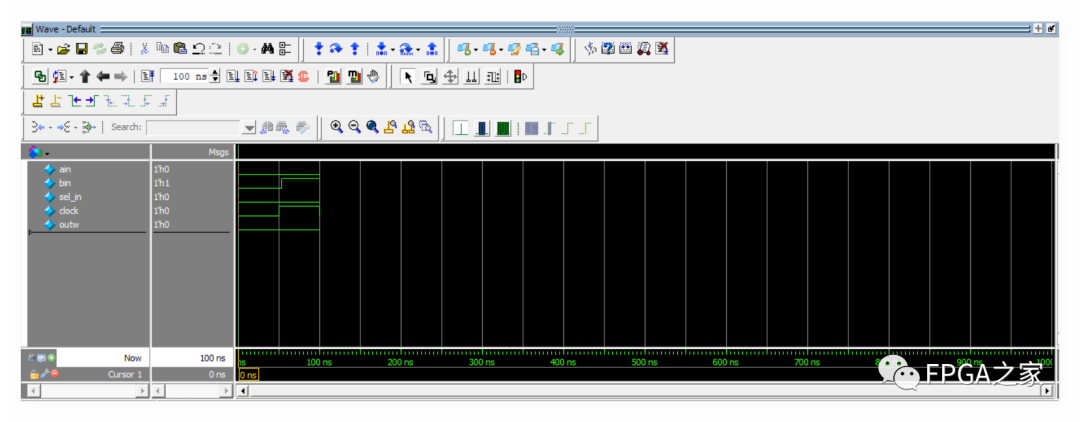

有信號名,但是沒有波形。這里出現的問題是沒有運行。光開顯示器不開主機,有啥子用。運行的快捷鍵在運行時間的右側,三種方式。第一個是正常運行,第二種是繼續(一般有stop系統函數的時候使用較多,第三個一直運行。運行時間的位置比較明顯,就是一堆快捷鍵中的數字輸入框。

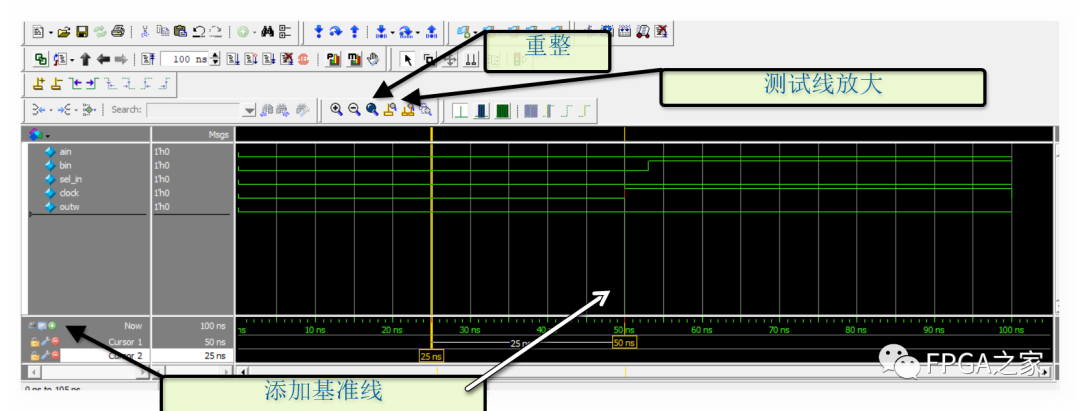

這是初始的波形,顯然看著不爽。調整波形的常用按鍵:

基本上掌握這三個鍵基本的功能就可以使用了。放大縮小也重要,但是一看就知,這里就不說明了。

基于軟件的順序邏輯,如果想要修改Verilog源文件,就要關閉工程,修改文件,保存文件、保存文件、保存文件,然后再編譯。重要的事情說三遍。modelsim的編譯是不會提醒文件是否保存的。一定要自己保存,否則,你得到的一直是修改前的文件編譯結果。

②基于聯合仿真的波形修改

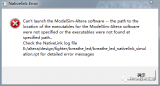

通過幾次實驗,發現使用重新啟動編譯的話,如果使用軟件操作的話還不如直接重啟后在啟動聯合仿真。比較合理的方法是使用現成的腳本,也就是聯合仿真時的.do文件。在控制臺再執行一次即可。

3、實驗結果

基本了解了modelsim的波形仿真的基本操作。但是對于聯合仿真的修改還是比較費時間,畢竟要編譯庫。不想記住的也可以重啟,反正差別不大。聯合仿真中會生成可執行工程文件,這個相當于一個快捷方式。這里說明一下。

審核編輯:郭婷

-

仿真

+關注

關注

50文章

4040瀏覽量

133413 -

Verilog

+關注

關注

28文章

1343瀏覽量

109983 -

代碼

+關注

關注

30文章

4744瀏覽量

68345

原文標題:modelsim波形仿真

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

用THP210做單端轉差分應用,仿真的波形里怎么總有個尖尖?

如何在ModelSim中添加Xilinx仿真庫

ISE 關聯 Modelsim 詳細操作

最實用的Modelsim使用教程

最實用的Modelsim使用及仿真的基本步驟

modelsim波形仿真的基本操作了解

modelsim波形仿真的基本操作了解

評論