引言

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標題:快速實現基于FPGA的脈動FIR濾波器,VHDL,脈動陣列,PE處理單元,FIR濾波器

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1626文章

21665瀏覽量

601828

原文標題:快速實現基于FPGA的脈動FIR濾波器,VHDL,脈動陣列,PE處理單元,FIR濾波器

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何區分IIR濾波器和FIR濾波器

IIR(無限脈沖響應)濾波器和FIR(有限脈沖響應)濾波器是數字信號處理領域中兩種非常重要的濾波器類型。它們在許多應用中都發揮著關鍵作用,如

iir濾波器和fir濾波器的優勢和特點

IIR濾波器和FIR濾波器是數字信號處理領域中兩種非常重要的濾波器類型。它們各自具有獨特的優勢和特點,適用于不同的應用場景。本文將介紹IIR

基于matlab FPGA verilog的FIR濾波器設計

今天和大俠簡單聊一聊基于matlab FPGA verilog的FIR濾波器設計,話不多說,上貨。

本次設計實現8階濾波器,9個系數

發表于 07-04 20:11

matlab與FPGA數字信號處理系列 Verilog 實現并行 FIR 濾波器

在 FPGA 實現 FIR 濾波器時,最常用的是直接型結構,簡單方便,在實現直接型結構時,可以選擇串行結構/并行結構/分布式結構。

并行結構

發表于 05-24 07:48

DSP教學實驗箱_DSP算法實驗_嵌入式教程:4-3 有限沖激響應濾波器(FIR)算法(CCS顯示)

一、實驗目的

了解FIR濾波器的特點,掌握程序算法生成濾波器系數的方法,并實現FIR濾波器濾除高

發表于 05-16 09:30

Vivado 使用Simulink設計FIR濾波器

型濾波器,是數字信號處理系統中最基本的元件,它可以在保證任意幅頻特性的同時具有嚴格的線性相頻特性,同時其單位抽樣響應是有限長的,因而濾波器是穩定的系統。因此,FIR

發表于 04-17 17:29

基于多速率DA的根升余弦濾波器的FPGA實現

處理技術和分布式算法的FPGA實現技術,使得計算量大幅減少,處理速度得到較大提高,而且使得FPGA資源利用更合理。1、根升余弦

發表于 03-25 14:21

Vivado經典案例:使用Simulink設計FIR濾波器

FIR(Finite Impulse Response)濾波器:有限長單位沖激響應濾波器,又稱為非遞歸型濾波器,是數字信號處理系統中最基本的

AD6620的FIR濾波器是什么類型的濾波器呢?

請問AD6620的FIR濾波器是什么類型的濾波器呢?它的功能是什么呢?可不可以直接從AD6620的輸出中進行符號同步的時鐘提取呢?謝謝!!!

發表于 12-22 07:00

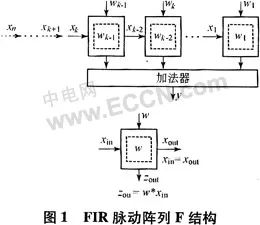

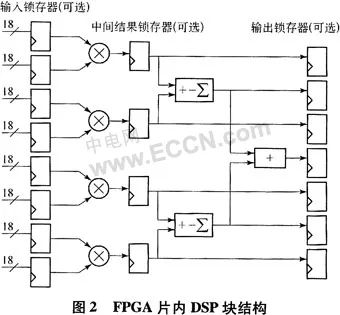

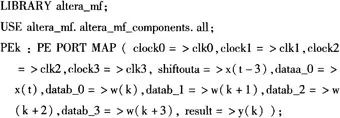

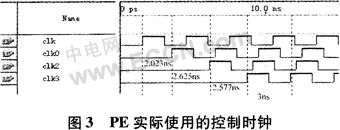

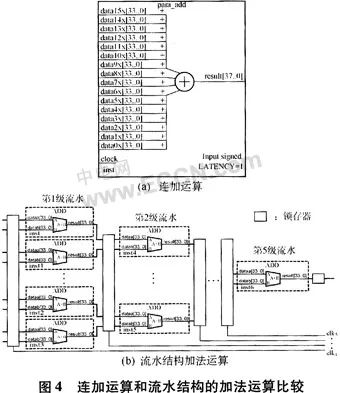

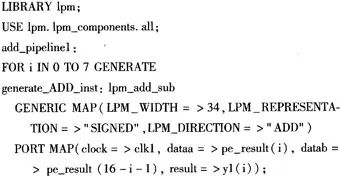

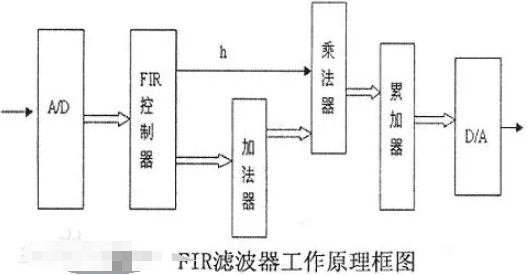

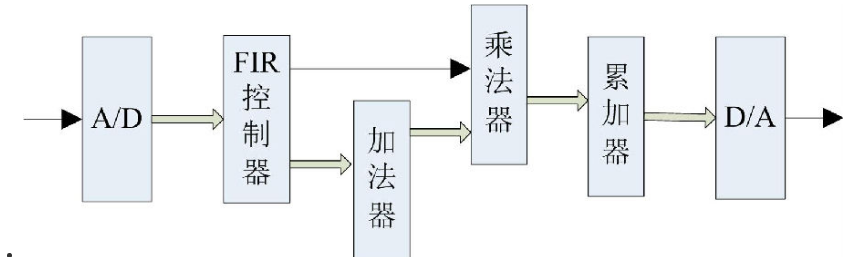

快速實現基于FPGA的脈動FIR濾波器,VHDL,脈動陣列,PE處理單元,FIR濾波器

快速實現基于FPGA的脈動FIR濾波器,VHDL,脈動陣列,PE處理單元,FIR濾波器

評論