大規(guī)模多輸入多輸出(mMIMO)的出現(xiàn)為基站硬件帶來了新的射頻挑戰(zhàn),而新的無線電技術(shù)則促進(jìn)了5G無線的發(fā)展。因此,已經(jīng)面臨日益增加的RF復(fù)雜性的5G基礎(chǔ)設(shè)施現(xiàn)在要求半導(dǎo)體公司進(jìn)行另一輪創(chuàng)新,以通過適應(yīng)性更強(qiáng)的解決方案來提高網(wǎng)絡(luò)效率。

到目前為止,通信設(shè)備制造商勢(shì)必會(huì)創(chuàng)建具有特定頻率的多個(gè)卡,以滿足無線行業(yè)對(duì)全球各種許可和未授權(quán)5G頻段的要求。以愛立信為例,該公司每周創(chuàng)建兩個(gè)電路板設(shè)計(jì),以跟上全球所有頻率計(jì)劃。

那么,我們?nèi)绾伍_發(fā)一個(gè)與頻率無關(guān)且可以在多個(gè)地區(qū)使用的單一平臺(tái)呢?特別是對(duì)于mMIMO無線電,它在面板中使用大量天線,這使得網(wǎng)絡(luò)效率至關(guān)重要。賽靈思聲稱其ZynqUltraScale+ ? RF?片上系統(tǒng) (SoC) 提供單芯片自適應(yīng)平臺(tái),可針對(duì)多種 5G 標(biāo)準(zhǔn)進(jìn)行重新配置。

直接射頻采樣

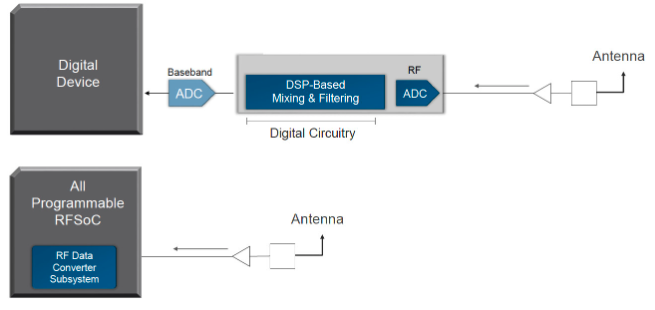

在傳統(tǒng)的模擬方法中,RF信號(hào)鏈通過JESD204接口連接到數(shù)字前端,RF采樣由分立元件執(zhí)行。它還涉及每個(gè)芯片一個(gè)或兩個(gè)轉(zhuǎn)換器。在這里,從一個(gè)芯片到另一個(gè)芯片的數(shù)據(jù)轉(zhuǎn)換可能需要高達(dá)8瓦的功率來傳輸320 Gb的數(shù)據(jù)。

但是,當(dāng)您使用大量發(fā)射器和接收器時(shí),就像在mMIMO設(shè)計(jì)中一樣,您必須非常注意功耗。因此,Zynq UltraScale+ 提供了一個(gè)單芯片自適應(yīng)無線電平臺(tái),可對(duì)射頻信號(hào)進(jìn)行直接采樣。

圖 1:傳統(tǒng)基于模擬的方法(上圖)和直接射頻采樣方法(下圖)之間的比較。

直接RF采樣直接處理輸入信號(hào),無需下變頻至中頻(IF)信號(hào),并應(yīng)用DSP技術(shù)在數(shù)字域中執(zhí)行信號(hào)調(diào)理等任務(wù)。這消除了JESD204在RF電路進(jìn)入下一個(gè)芯片執(zhí)行網(wǎng)絡(luò)路由等任務(wù)時(shí)的瓶頸。

這反過來又簡(jiǎn)化了模數(shù)信號(hào)鏈,并允許處理更多數(shù)據(jù),這是5G系統(tǒng)中mMIMO基站的關(guān)鍵優(yōu)勢(shì)。該單芯片自適應(yīng)平臺(tái)集成了基帶、無線電IP、MAC、DSP信令和濾波以及具有通用數(shù)字處理器和DDR4存儲(chǔ)器子系統(tǒng)的數(shù)據(jù)轉(zhuǎn)換器。

例如,RF數(shù)據(jù)轉(zhuǎn)換器的集成為降低功耗、占位面積和物料清單(BOM)成本提供了寶貴的途徑。ZynqUltraScale+ 使用 14 位模數(shù)轉(zhuǎn)換器 (ADC) 支持高達(dá) 5 Giga 樣本/秒的直接射頻采樣,使用 14 位數(shù)模轉(zhuǎn)換器 (DAC) 支持高達(dá) 10 G 采樣/秒的直接射頻采樣。?

在 Zynq UltraScale+ 中,RF ADC 的采樣速率從 4 G 采樣/秒提高到 5 G 采樣/秒,RF DAC 的采樣速率從 6 G 采樣/秒提高到 10 G 采樣/秒。對(duì)于時(shí)分雙工(TDD)用例,RF數(shù)據(jù)模塊的功耗降低了20%。在這里,值得一提的是,大多數(shù)5G無線電都是基于TDD技術(shù)的。

FPGA 如何助力射頻設(shè)計(jì)

以FPGA為中心的設(shè)計(jì)通常需要數(shù)據(jù)轉(zhuǎn)換器,但到目前為止,只有低性能轉(zhuǎn)換器被集成到FPGA中,用于系統(tǒng)監(jiān)控等應(yīng)用。這主要是因?yàn)槟M和數(shù)字處理器是由半導(dǎo)體公司的不同集團(tuán)甚至完全由不同的公司開發(fā)的。

數(shù)字團(tuán)隊(duì)致力于節(jié)點(diǎn)遷移以縮小節(jié)點(diǎn)大小,而模擬工程師則使用穩(wěn)定的舊處理節(jié)點(diǎn)。但是,在像mMIMO這樣的現(xiàn)代無線電用例中,它必須改變,這些用例要求更高的集成度。

Xilinx 聲稱,采用 16 nm 鰭式場(chǎng)效應(yīng)晶體管工藝制造的 Zynq UltraScale+ 是這種更高集成度的體現(xiàn);它將模擬域和數(shù)字域集成到一塊硅片中,以通過可編程邏輯優(yōu)化信號(hào)流。

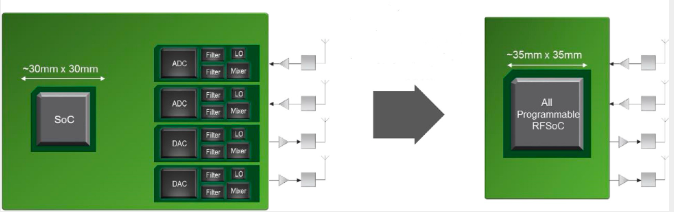

硬件和軟件可編程引擎的集成消除了分立元件,從而將功耗和設(shè)計(jì)尺寸降低了多達(dá) 50%。例如,Zynq UltraScale+ 通過將外部 PLL 振蕩器的數(shù)量從四個(gè)減少到一個(gè)來降低 BOM 成本。

圖 2:集成模擬和數(shù)字部件的單芯片射頻解決方案如何降低功耗、占位面積和 BOM 成本。

除了 5G 基站設(shè)計(jì),Xilinx 還將這種多頻段無線電芯片用于其他射頻應(yīng)用,如相控陣?yán)走_(dá)網(wǎng)絡(luò)和天氣監(jiān)視系統(tǒng)。然后,還有一些用例,例如用于電纜接入的遠(yuǎn)程PHY節(jié)點(diǎn),汽車中的激光雷達(dá)系統(tǒng),測(cè)試和測(cè)量以及衛(wèi)星通信。

適應(yīng)5G世界

5G標(biāo)準(zhǔn)將在未來幾年內(nèi)不斷發(fā)展,這將繼續(xù)改變系統(tǒng)要求。因此,與通信設(shè)備制造商一直在使用ASIC的3G和4G設(shè)計(jì)領(lǐng)域不同,靈活的邏輯方法更有可能經(jīng)受住增量5G部署。

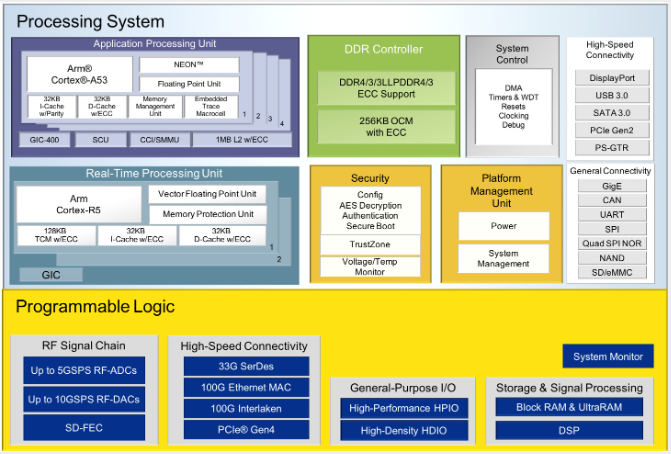

當(dāng)今5G設(shè)計(jì)環(huán)境中的ASIC解決方案很可能在一年內(nèi)過時(shí)。另一方面,連接模擬域和數(shù)字域的可編程解決方案(圖3)可以針對(duì)各種5G安裝進(jìn)行重新配置。

圖 3:顯示不同子系統(tǒng)的 Zynq UltraScale+ 射頻芯片框圖。

本文介紹了一種高度集成的RF芯片的概況,該芯片在數(shù)字域內(nèi)執(zhí)行下變頻過程,從而繞過了傳統(tǒng)的模擬RF采樣方式,該方式涉及分立元件的下變頻。

生活筆記本:郭婷

-

芯片

+關(guān)注

關(guān)注

454文章

50430瀏覽量

421894 -

射頻

+關(guān)注

關(guān)注

104文章

5551瀏覽量

167557 -

無線電

+關(guān)注

關(guān)注

59文章

2131瀏覽量

116320

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

智能駕駛所需的基礎(chǔ)設(shè)施

愛立信連續(xù)四年獲評(píng)5G網(wǎng)絡(luò)基礎(chǔ)設(shè)施市場(chǎng)領(lǐng)導(dǎo)者

愛立信連續(xù)第四年名列Frost Radar? 5G網(wǎng)絡(luò)基礎(chǔ)設(shè)施市場(chǎng)榜首

5G基站關(guān)鍵射頻參數(shù)的測(cè)量

美格智能聯(lián)合羅德與施瓦茨完成5G RedCap模組SRM813Q驗(yàn)證,推動(dòng)5G輕量化全面商用

高通推出面向5G基礎(chǔ)設(shè)施的智能計(jì)算解決方案

一文詳解5G射頻功率放大器

5g基站端的毫米波射頻芯片有哪些

5G網(wǎng)絡(luò)速度影響因素與潛在應(yīng)用

5G毫米波相控陣通信射頻芯片有哪些

5G 外置天線

5g毫米波相控陣通信射頻芯片有哪些

4G/5G MiMo鯊魚鰭#天線 解決方案#無線通信 #射頻與天線 #通信 #5G #移動(dòng)通信網(wǎng)絡(luò)

5G射頻PA架構(gòu)設(shè)計(jì)

5G基礎(chǔ)設(shè)施開啟射頻芯片內(nèi)部的新集成前沿

5G基礎(chǔ)設(shè)施開啟射頻芯片內(nèi)部的新集成前沿

評(píng)論