本系列的前一期是從理解數據手冊到實際實現以實現預期性能的轉變。這包括對模數轉換器(ADC)輸入信號的電源和信號路由的考慮。最后一期將重點介紹差分信號的優勢,現在許多微控制器(MCU)都提供了差分信號。

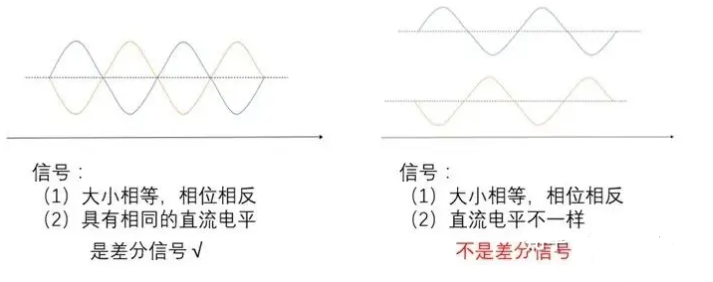

差分信號是在模擬測量過程中解決噪聲的寶貴工具。差分信號的優勢在于將噪聲作為共模消除的簡單性。挑戰在于設計一個電路,使差分對的兩個導體實際上具有共性噪聲。這一挑戰延伸到嵌入式硬件工程師和集成電路(IC)設計人員。

在IC設計中,基板噪聲是一個挑戰。基板充當產生噪聲的元件或外設與集成ADC之間的橋梁或介質。同樣,在板級,相鄰的數字信號可以與模擬走線耦合。這種耦合的強度通常會因不良(高阻抗)接地結構而增強,迫使返回路徑較長,從而增加電磁場邊緣。對于輻射抗擾度,與無線電的距離相比,差分間距應該相對較小。在這三種情況下,假設噪聲與正極和負極導體相等耦合,并且噪聲在兩個導體上的傳播相等。這突出了差分信號對稱性的必要性,以便抑制共模信號,例如IC、電路板和應用(系統)級的噪聲。

在討論差分信號的好處之前,重要的是要提到成本。在MCU上,成本是ADC輸入引腳數量的兩倍。在整個信號鏈中,構成模擬前端(AFE)的組件也會加倍或復制。與任何設計一樣,您必須權衡這些成本與收益。

以下部分說明了在IC級、板級和應用級差分信號的優勢,在被測器件(DUT)附近放置Sub-1 GHz無線電。

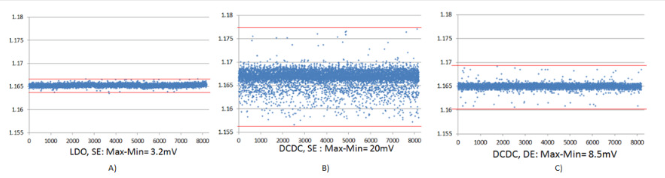

在IC級,電源管理架構會給系統帶來噪聲,在比較一種架構相對于另一種架構的優勢時,應考慮這一點。對于內部電壓調節,IC可以使用低壓差穩壓器(LDO)或DC/DC轉換器。雖然DC/DC通常是兩者中效率更高的,但圖1b顯示,相對于圖1a中的LDO,DC/DC也貢獻了更多的噪聲。噪聲等同于ADC返回的最小和最大電壓之差的增加。在圖1a和圖1b中,ADC測量直流電壓約為250KSPS,持續32ms。DC/DC穩壓器的轉換結果變化是LDO的六倍以上。

圖 1:具有單端測量的內部 LDO 穩壓器 (a);具有單端測量的內部 DC/DC 穩壓器 (b);帶差分端測量的內部 DC/DC 穩壓器 (c)

比較圖1b和1c,如果在差分模式下使用DC/DC穩壓器進行相同的測量,則總噪聲會降低,LDO和DC/DC性能之間的差異很小。圖1顯示了以伏特而不是最低有效位(LSB)為單位的性能,垂直軸轉換為伏特,因為差分的LSB是單端的兩倍,以考慮對有符號結果(負電壓)的支持。差分測量中的方差小于單端實現中方差的一半,表明ADC將來自DC/DC的大部分噪聲視為共模噪聲。

被測直流電壓被視為差分輸入,其中Vss是ADC的負輸入。因此,即使信號本身是單端信號,在差分模式下進行測量也能降低噪聲,而且在使用DC/DC穩壓器時還可以降低噪聲。這是一個非常好的消息,使工程師能夠利用DC/DC的優勢,同時消除相關的噪聲。

來自內部穩壓器的噪聲只是一種可能的噪聲源。其他可能的噪聲源可以是相鄰的數字信號,例如I2C 或串行外設接口 (SPI) 通信,或脈寬調制 (PWM) 波形。我們建議使這些信號盡可能遠離ADC引腳,如果可能的話,在ADC測量期間保持非活動狀態。大多數IC制造商通過創建專用模擬引腳,有意使數字信號遠離模擬。然而,在較小的封裝中,某些數字功能可能與模擬引腳多路復用,或者數字輸入/輸出(I/O)引腳可能與模擬引腳相鄰。

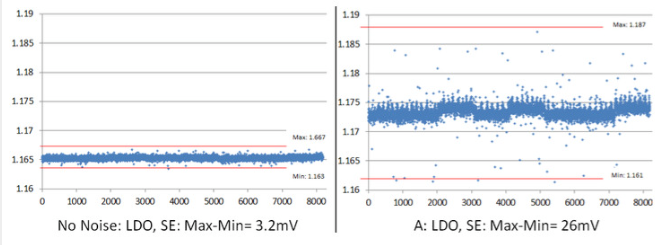

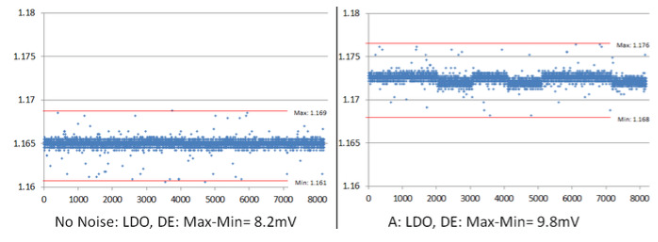

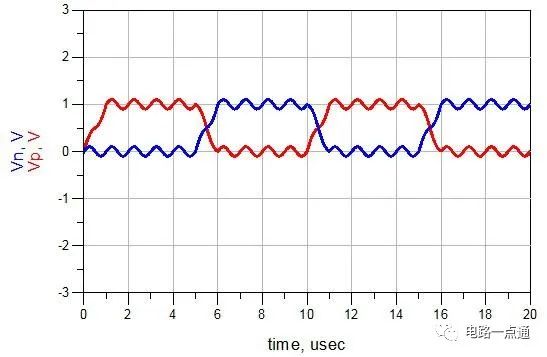

作為實驗,讓我們將DUT模擬輸入緊鄰48MHz時鐘輸出(全軌到軌擺幅)定位,以表示數字噪聲源。如圖2和圖3所示,與差分相比,單端測量增加相鄰時鐘輸出時噪聲增加幅度更大。在單端情況下,測量的電壓連接到模擬輸入。差分模式下的互補輸入保留在通用I/O (GPIO)模式下,并主動驅動低電平,即器件的數字源電源電壓(DVSS)。在差分情況下,互補輸入從外部連接到器件的模擬源電源電壓(AVSS)。

雖然與單端示例相比很小,但差分結果表明噪聲仍然存在。目視檢查顯示,與差分對的正極和負極之間的分離相比,時鐘相對接近差分測量的正極。因此,相對耦合將不相等,噪聲也不會完全顯示為共模。

該實驗是在四層PCB上進行的,第三層提供幾乎完全堅固的接地層,因此返回電流可以直接跟隨走線下方。第二層提供基準電壓,并分為多個位置,使信號和接地層返回路徑之間的耦合復雜化,并可能產生噪聲介質以影響測量,這可能進一步解釋噪聲的存在

圖 2:從相鄰時鐘感應到單端 ADC 輸入的串擾 A 與無噪聲的關系

圖 3:從相鄰時鐘感應到差分 ADC 輸入的串擾 A 與無噪聲的關系

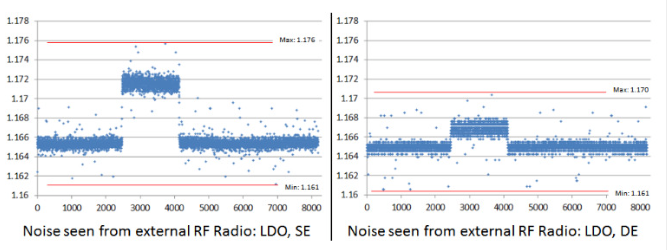

在最后一個實驗中,一個以50kB(868MHz,2GFSK,2kHz偏差)傳輸100個隨機數據包的評估模塊引入了無線電信號。EVM 放置在 DUT 附近,因此 MCU(和 ADC)距離 EVM 的 PCB 天線約 6 厘米。圖4再次顯示,差分配置的抗擾度優于單端。關鍵是能量均勻耦合在差分ADC的正輸入和負輸入上,因此信號作為共模被抑制理想情況下,在圖4所示的差分測量中不會看到噪聲,因此這種偏離預期值得討論的潛在原因。

圖4:附近無線電信號引起的噪聲

時鐘和Sub-1 GHz無線電實驗之間最顯著的區別是相對耦合面積。就時鐘而言,耦合區域與時鐘走線與ADC輸入線平行的位置最相關。在這種并行運行之后,信號發散:ADC信號脫離板外到電壓源進行測量,而時鐘終止于另一個接收輸入。

正是具有最小屏蔽的板外連接為無線電能量耦合到ADC提供了一種潛在的方式。此外,ADC正輸入和負輸入之間的任何電氣長度差異都可能導致耦合噪聲為差分噪聲,而不是共模噪聲。最小化ADC正輸入和負輸入之間電氣長度差異的一種有效方法是設計對稱的信號路徑。

本節中的測試旨在顯示差分信號提供的改進范圍。改進發生在應用程序或實現級別。來自鄰近無線電的干擾也適用于需要電磁兼容性 (EMC) 的藍牙和 Wi-Fi 應用。在電路板層面也有明顯的改進,來自相鄰數字信號的交叉耦合(串擾)。最后,在IC級甚至可以看到改進,選擇噪聲穩壓器可以實現低功耗操作,并減輕ADC性能的下降。

雖然差分信號是實現數據手冊中ADC性能的寶貴工具,但了解數據手冊參數必須是優先事項。MCU中有許多與ADC性能相關的配置和依賴關系,這使得理解數據手冊性能與應用要求相關的困難。

本系列討論了一些主要的性能依賴性,并提供了一些趨勢,以幫助揭開MCU數據手冊和集成ADC性能的神秘面紗。有了這種理解,開發人員可以為傳感器應用做出更明智的MCU選擇,并實現完全實現集成ADC性能的設計。

審核編輯:郭婷

-

ldo

+關注

關注

35文章

1846瀏覽量

152722 -

adc

+關注

關注

97文章

6300瀏覽量

542459 -

無線電

+關注

關注

58文章

2114瀏覽量

115823 -

差分信號

+關注

關注

3文章

361瀏覽量

27539

發布評論請先 登錄

相關推薦

探討差分信號的優缺點

差分信號是什么意思?差分信號怎么產生?

高速差分信號有哪些

高速差分信號概述及其應用

解讀差分信號、單端信號的優缺點

什么是差分信號?什么是單端信號?

普通探頭對差分信號測量的危害有哪些?如何避免呢?

AD差分信號走線有哪些規則要遵循?

差分信號進入ADC芯片,怎樣才能保證兩差分信號自動均衡呢?

什么是差分信號?差分信號的優勢和注意事項

介紹差分信號的優勢

介紹差分信號的優勢

評論